1 引言

从1976年美国数据加密标准算法(DES)公布以来,到20世纪末,DES算法或其某些变形基本上主宰了对称算法的研究与开发进程。随着密码分析水平、芯片处理能力和计算技术的不断进步,DES的安全强度已经难以适应新的安全需要,其实现速度、代码大小和跨平台性均难以继续满足性的应用需求。因此,AES(高级加密标准)应运而生。作为DES的继承者,AES自从被接纳为标准之日起就已经被工业界、银行业和行政部门作为事实上的密码标准。在网络通信和某些工业控制应用场合,对加密速度的需求成为对AES算法的最关键要求,同时功耗成为日渐突出的问题,必须进行低功耗设计。

2 AES加密算法简介

AES是一个密钥迭代分组密码,对加密来说,输入是一个明文分组和一个密钥,输出是一个密文分组。它将分组长度固定为128比特,而且仅支持128、196或256比特的密钥长度,本文仅对密钥长度为128比特的情况进行讨论。

加密过程包括一个初始密钥加法,记作AddRoundKey,接着进行9次轮变换(Round),最后再使用一个轮变换(FinalRound)。轮变换由SubBytes、ShiftRows、MixColumns 和AddRoundKey 共4个步骤构成。轮变换及其每一步均作用在中间结果上,将该中间结果称为状态,可以形象地表示为一个4*4字节的矩阵。

3 AES的改进算法(T盒算法)

假设加密过程中轮变化的输入为a,输出为d,则:

上式中SRD(S盒)由有限域GF(28)中的乘法逆变换和GF(2)中的仿射变换复合而成,符号 代表有限域GF(28)中的加法运算,符号 代表有限域GF(28)中的乘法运算。

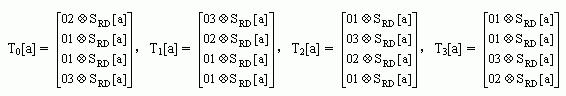

这样我们可以定义4个表:T0,T1,T2以及T3:

则d简化为:

该实现方案中T0~T3,每个表都包含了256个双字,一共占用4KByte的空间。在每次循环迭代中,只要通过4次表查询和4次异或运算,就能快速地得到一次轮操作中一列的运算结果。改进算法有效降低了关键时序路径的传输延迟,能够明显的提高ASIC工作频率。

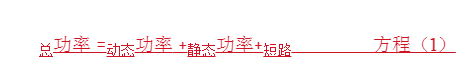

4 CMOS功耗

对于一个CMOS逻辑门,其功耗主要由静态功耗和动态功耗两部分组成。静态功耗是指门处于非活动状态时的功耗,大部分是由扩散层到衬底,源极到漏极存在的反偏二极管造成的泄露电流产生的。一般来说,泄漏电流功耗在总功耗中所占的比重不到1%。动态功耗是门处于活动状态下产生的,它又包含两部分:开关功耗和内部功耗。内部功耗包括对门内部的寄生电容充放电的翻转电流功耗,以及PMOS管和NMOS管瞬间同时导通所形成的短路电流功耗。对于信号上升(下降)快的电路,短路电流功耗很小,但对信号上升(下降)较慢的电路,短路电流功耗可能要占总功耗的30%以上。开关功耗是对输出端负载电容充放电的翻转电流引起的。

5 低功耗设计

该实现方案中主要采用了以下两种低功耗设计方法。

1) 动态功耗管理

动态功耗管理是一种系统级低功耗设计方法,降低功耗的主要思路是根据芯片工作状态改变功耗管理模式,从而在保证性能的基础上降低功耗。在不同模式下,时钟的频率可以进行调整,一些空闲模块甚至整个芯片的时钟也可能会被停止。还可以通过调整芯片的电压,进一步降低功耗。由于工作库的限制,本文没有对动态电压管理作进一步的研究。

本文采用动态功耗管理,分为normal和idle两种功耗模式。有开始(START)信号时,芯片由idle模式进入normal模式,开始对明文分组加密。经过初始密钥加法和10次轮变换,输出密文分组,并产生结束(STOP)信号,使芯片返回idle模式。因此设计了一个鉴相器产生idle模式的控制信号(EN)。电路由与非门和基本RS触发器组成(图1),对输入信号(开始和结束)的上升沿感应,由D触发器输出EN。具有结构简单的特点,并对噪声的影响有很好的抑制作用,并能有效地去除毛刺。

2) 时钟门控

EN有关闭和打开ASIC内部模块的作用,但这样不是最佳的,因为EN只是关闭了内部模块的功能操作,而并没有把模块内的时钟网络关闭,也就是说时钟网络依然处于激活状态,而时钟网络造成的功耗占总功耗的很大部分,只有关闭时钟网络才能同时达到关闭模块功能和降低功耗的目的。

采用时钟门控技术可以达到关闭时钟网络的目的。以图2(a)中所示电路为例,仿真生成的波形如图2(b)所示。可以看到只有在EN信号为1和时钟信号CLK上跳同时发生,ENCLK才会从0变为1,激活时钟网络。在其他时刻,时钟网络是关闭的。插入的时钟门控单元不仅能通过关闭时钟网络而明显的降低功耗外,还有其他几个重要的功能:

① D触发器的时钟输入端口对毛刺敏感,门控单元能有效地滤除信号EN的毛刺,从而确保进入D触发器时钟端口的ENCLK信号不会出现毛刺,避免因竞争而导致触发器发生错误的状态变化。

② 锁存器的插入增加了ENL信号的延时。

③ 对于n位寄存器组,n条反馈连线和n个多路选择器被一个门控单元所取代,不仅带来面

积上的节省,降低后端布线的拥塞,同时又进一步降低了功耗。

6 实现方案

该实现方案采用Synopsys公司的芯片设计流程和VeriSilicon公司0.18μm CMOS工艺。首先根据设计规范,使用Verilog硬件描述语言编写可综合的RTL代码,并对RTL代码进行仿真。然后对RTL代码进行综合。综合后生成的门级网表和RTL代码进行等效性检验并做静态时序分析。接着进行版图设计,先是根据各逻辑单元间的时序采用时序驱动布局策略来做物理布局和全局布线,之后在设计中插入时钟树。然后进行详细布线,并从详细布线后的版图中提取出真实的时延值并将其反标给网表,再作等效性检验、静态时序分析和仿真验证保证满足时序约束。最后对版图做设计规则检查。

7 结论

本文针对AES的ASIC实现,使用改进算法和低功耗设计方法,实现了高速低功耗的AES ASIC设计,其基本思想是:采用T盒算法,只要通过4次表查询和4次异或运算,就能快速地得到一次轮操作中一列的运算结果,同时在满足时序约束的前提下,通过动态功耗管理和时钟门控等方法,根据芯片的工作状态关闭模块的功能操作并关闭时钟网络,达到了降低功耗的目的。从表1可以清晰地看出,采用T盒算法后,设计的数据吞吐率提高了13.8%,同时采用功耗优化方案后,normal模式下功耗下降了10.7%,在idle模式时更低。该实现方案适用于ECB,CBC等运行模式。

-

asic

+关注

关注

34文章

1141浏览量

119246 -

寄存器

+关注

关注

30文章

5020浏览量

117628 -

低功耗

+关注

关注

9文章

2223浏览量

102572

发布评论请先 登录

相关推荐

在ASIC的物理设计的低功耗实现技术解析

FPGA设计怎么降低功耗

基于FPGA的AES加密算法的高速实现

基于FPGA的AES加密算法的高速实现

低功耗AES信息安全芯片设计与实现

新型流水线实现高速低功耗ADC的原理及方法

高速低功耗的AES ASIC设计如何实现

高速低功耗的AES ASIC设计如何实现

评论