在高速数据采集系统中,若A/D转换器直接与微处理器MCU相接,则因高速A/D的转换速率较高,迫使MCU不断地读取转换结果,因而就占用了MCU大部分的I/O带宽,降低了MCU的工作效率。在此情况下通常都会加缓存器,这样“模/数转换器缓存器一处理器”就成为一种通用模式。下面就介绍如何利用FIFO芯片CY7C4255V实现高速高精度模/数转换器AD767l与LPC2200系列ARM处理器的接口。

1 、器件简介

1.1 模/数转换器AD7671

AD767l是采样速率达1Msps的16位逐次逼近型高速高精度模/数转换器,采用5V单电源供电,并能提供单极性和双极性两种输入方式,可适用不同的输入范围;它还提供校准与误差校正电路、内部时钟、8位或16位并行口和1个串行口。AD7671能够达到16位分辨率,而且无失码,最大积分非线性误差(INL)仅为2.5 LSB,能够满足各种高精度应用的要求。

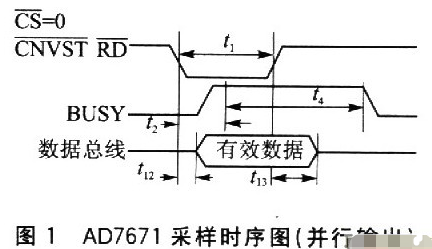

通常情况下,AD7671有两种数据读取方式:一种是在数据转换完成后,读取转换的数据;另一种是在数据转换的过程中,读取上一次转换完成的数据。图l中的时序图描述了后一种情况,即主控制器发出CNVST信号后,检测BUSY信号。当BUSY信号置为高电平时,读取由上一个转换过程所转换的数据。

1.2 FIFO芯片CY7C4255V

FIFO(First In First Out)简单说就是指先进先出。作为一种新型大规模集成电路,FIFO芯片以其灵活、方便、高效的特性,逐渐在高速数据采集、高速数据处理、高速数据传输以及多机处理系统中得到越来越广泛的应用。CY7C455V是Cypress公司的3.3V高速,低功耗的FIFO,芯片容量为8K18位,最高工作速率为100MHz(最短读/写时间为10ns),输入/输出端口由单独的时钟和使能信号控制,具有“空”、“满”、“半满”和可编程的“几乎空”、“几乎满”标志。

CY7C4255的18位输入/输出端口由单独的时钟和使能信号控制。输入端口由一连续写时钟(WCLK)和写使能信号(WEN)控制,当写使能WEN有效时,数据在每个时钟周期WCLK信号的上升沿被连续写入FIFO存储器中。同样,输出端口由一连续读时钟(RCLK)和读使能信号(REN)控制,而且有一个输出使能引脚(OE)。如果是单时钟操作,则读/写时钟可连接在一起;在异步读/写应用中,两个时钟可以是独立的,时钟频率最高可达100 MHz。利用芯片提供的级联输入(WXI、RXI)、级联输出(WXO、RXO)和首先加载(FL)引脚可进行深度扩展。

1.3 ARM处理器LPC2210

LPC2210是基于一个支持实时仿真和嵌入式跟踪的16/32位144脚ARM7TDMI-S核的微控制器。它内部包含ARM7TDMI-S核与片内存储器控制器接口的ARM7局部总线、与中断控制器接口的AMBA高性能总线(AHB)和连接片内外设功能的VLSI外设总线(VPBARM AMBA总线的兼容超集)。LPC2210具有16KB片内静态RAM;片内外设与器件引脚的连接由引脚连接模块控制,该模块由软件进行控制以符合外设功能与引脚在特定应用中的需求;通过外部存储器接口可将存储器配置成4组,每组的容量高达16MB,数据宽度为8/16/32位;具有2个32位定时器(带4路捕获和4路比较通道)、PWM单元(6路输出)、实时时钟和看门狗;多个串行接口包括2个16C550工业标准UART、高速I2C接口(400kb/s)和2个SPI接口;多达76个通用I/O口(可承受5V电压),12个独立外部中断引脚EIN和CAP功能。

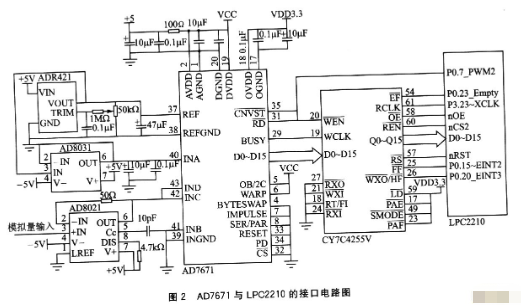

2 、接口电路

利用FIFO芯片CY7C4255V实现AD7671与LPC2210的接口电路,如图2所示。图中,AD7671的输入范围已经配置成士5V,其数据端口采用高速并行接口;接口的数据读取模式设置为图l所示的模式,其中+5V和一5V分别是模拟电压。由于CY7C11255V与LPC2210的数据接口的电压为3.3V,所以将3.3V数字电压输入到OVDD引脚,这样AD7671的数据接口电压就可以与FIFO芯片的数据接口相兼容。ADR421为AD7671提供了+2.5V的基准电压;AD7671的模拟输入端,采用了由低噪声系数的激励放大器ADS02l构成的驱动电路来驱动A137671。

A/D转换结果输出直接与FIFO数据输入端D0~D15相连}转换控制由ARM处理器的一个PWM输出端产生所需的采样频率的采样控制信号,该信号同时作为 FIFO的输入使能端的控制。AD767l的BUSY输出端作为FIFO的输入时钟(WCLK)控制信号,当转换结束时 BUSY(WCLK)由低变高,此时FIFO写使能WEN有效,转换数据就在WCLK(BUSY)信号的上升沿被写入FIFO 存储器中。LPC2210 ARM处理器总线数据宽度配置为 16位,由EMC总线的片选信号nCS2、输出使能信号 nOE、时钟输出XCLK来控制FIFO的数据读取。FIFO 的半满(HF)、全满(FF)标志与ARM的2个中断引脚相连,可通过编程在实际应用中选择使用;EF接ARM的 PO.23引脚作为FIFO的空查询引脚。

3、结语

采用FIFO器件作为高速A/D与ARM处理器间的数据缓冲,具有电路结构简单、性能可靠等优点;同时提高了处理器的工作效率,使控制更加方便。

责任编辑:gt

-

处理器

+关注

关注

68文章

18240浏览量

222016 -

芯片

+关注

关注

446文章

47728浏览量

409012 -

fifo

+关注

关注

3文章

369浏览量

43055

发布评论请先 登录

相关推荐

SEP3203处理器的FPGA数据通信接口设计

SEP3203处理器实现FPGA数据通信接口设计

采用CPLD实现ADS8323与高速FIFO接口电路

采用ARM微处理器实现液晶触摸屏接口设计

什么是ARM处理器 ARM处理器有哪些系列

基于FIFO存储器实现AD转换器与ARM的接口设计

如何采用SoPC实现了一个UART串行口和以太网接口的转换器?

熟悉串行接口模/数转换器的基本原理和编程方法

高速模数转换器与TMS320C6000DSP接口的FIFO实现

基于FIFO存储器实现高速AD转换器与ARM处理器的接口设计

通过采用FIFO芯片实现模/数转换器和ARM处理器的接口设计

通过采用FIFO芯片实现模/数转换器和ARM处理器的接口设计

评论