基于P89C51RD2和FPGA的信号延时模块主要用在传输时钟信号、数字同步信号等对信号延迟有高要求的点对点传输系统中,它可对多路信号进行单独的适当延时调整。造成信号的延迟原因有:不同的传输线路、信号处理时间不同以及器件速度存在差异等。无论何种原因,延时模块可以对输入的已存在有延时积累的信号进行不同精度、不同范围的延时量调节,使信号到达终端后相对延迟时间符合要求。由于利用了可编程器件FPGA和增强型单片机,延时模块不仅能较好地实现其功能,而且实现了系统的模块化和微型化,利于模块在系统中的使用和模块的二次开发。

系统结构及硬件设计

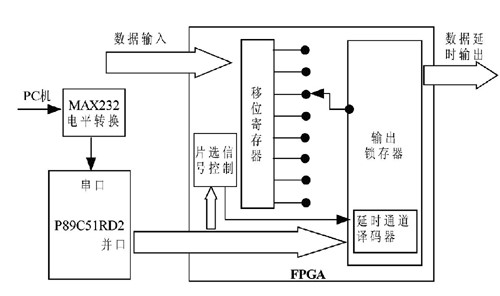

系统结构框图如图1。其硬件结构比较简单,主要由单片机P89C51RD、RS-232/TTL接口电路MAX232和可编程逻辑器件FPGA三部分组成。单片机P89C51RD2是上位PC机和FPGA的连接纽带,它通过并口发送数据给FPGA,另一边通过RS-232/TTL接口芯片与PC机进行串行通讯;PC机主要功能是实现延时调整的可视化操作;FPGA是延时调整处理的硬件实现,单片机将PC送过来的延时调整参数输入FPGA,FPGA在单片机的控制下对信号进行延迟处理,最后送入相应传输通道。某些系统使用现场存在较强的电磁干扰,模块的设计考虑信号隔离问题,故对串行接口进行了电气隔离,强化了PC机和模块通讯的安全系数。

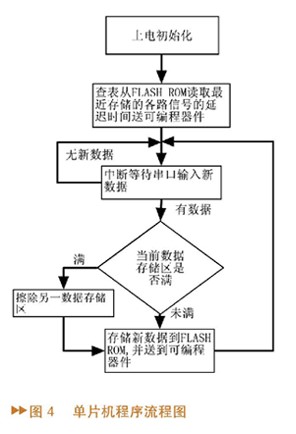

延时模块正常上电后,单片机P89C51RD2首先从数据存储区读出最近一次存储的延迟时间、信号通道等参数,并转发到FPGA数据接口。FPGA根据接收到的参数,首先筛选出目标地址以便切换到对应的信号通道,然后再根据时间对该通道进行预定的延时,恢复先前调整好的延时信号。在模块运行期间,P89C51RD2实时监测、接收来自上位PC机发送的新延时数据。如果需要对某一路信号的延时量进行调节,通过PC机的串口发新数据,P89C51RD2中断收到新数据后,将数据分成两路处理:一路进入到单片机的数据存储区,待下次上电读取使用;另一路则转发至由FPGA控制的延时控制,实现信号的延迟时间调整。

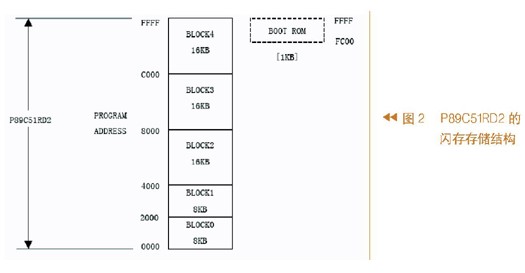

块使用的P89C51RD2是PHILIPS公司内核基于8 位80C51单片机的派生产品,它们在完全保留80C51 指令系统和硬件结构的大框架外,还具有多方面的功能加强、扩展、翻新和创新,其中在应用中编程(IAP:In-Application Programming)是最显著特点之一。在应用中可编程是指MCU可以在系统中获取新代码并对自己重新编程,即用程序来改变程序。P89C51RD2的IAP功能实现是通过PHILIPS 公司提供的BootROM 固件来完成的,它位于0FC00H?0FFFFH空间,与闪存空间重叠(见图2)。固件中已经固化有擦除和编程等子程序,PHILIPS 公司提供了寻址该固件的方法,只要用户程序简单调用BootROM中带适当参数的公共入口,即可实现所需要的操作。

P89C51RD2闪存结构见图2,它具有如下特点:

1. 其闪存空间是分块的64kB的闪存空间,共分5块,由低到高分别为8kB(BLOCK0)、8kB(BLOCK1)、16kB(BLOCK2)、16kB(BLOCK3)以及16kB( BLOCK4);

2. 每一块都可以单独擦除;

3. 在程序中可以调用IAP功能对闪存中的每一字节进行单独编程。

正是由于上述三个特点,在不外扩展存储器情况下,将程序空间剩余下的闪存空间作为数据空间,把单片机接收中断采集到的信号通道、延迟时间等参数存储下来,实现掉电数据保存。

软件设计

整个延时模块的软件包括了PC机发送参数程序,单片机接收并存储参数程序和FPGA信号延时处理程序。

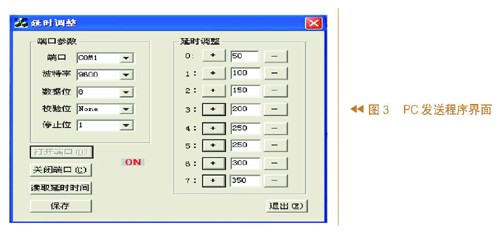

PC机发送参数程序是用户将PC机的串口与模块连接,通过PC机的发送程序界面,很容易对信号进行延时调整。发送程序采用VC作为编程语言,调用串口控件,设计方便且界面简洁,界面如图3所示。发送的每个数据帧8位,包括延迟时间和信号通道两个参数,其中高三位是要调整的信号通道,后五位表示延迟的时间。发送程序中,对界面中的“+”或“?”进行一次操作,PC就通过串口向单片机连续发送8路信号延时参数,即只要调节了任一路信号的延时,PC机就会连续发送8个数据帧。

在P89C51RD2的64k闪存空间中,地址为0000H-7FFFH的32kB闪存空间作为程序空间,整个单片机程序编译后为15k,所以32k的程序空间足够大。余下的8000H?FFFFH的32kB 闪存空间留作数据存储空间。两块数据存储空间轮流使用,当数据量存满其中一块时通过程序跳转到另一块,在使用前先将该块擦除。

各函数介绍如下:

main()——主程序;

InitUart(void)——串口初始化;

IapInit(void)——IAP功能初始化,使用IAP功能前必调用;

PowerOnRead(void)——上电读取最近一次存储的参数。模块对上电时间要求不苛刻,最新数据的地址可通过查表方式寻找。每一个数据帧占一个数据存储空间,由于单片机每次中断都接收到8个数据帧,所以将每8个数据存储空间划分成一组,这样只要查询每组的头一个地址就能快捷地完成查询,大大节省了查询时间。

EraseBlock (uint AddressRestore)——判断当前数据存储空间块满,并擦除;

RestoreData(void)——数据存储在数据存储空间;

FPGADataUp(uchar DataRec)——更新FPGA接口数据。

在程序中,要多次调用BootROM固件中的子程序。由于IAP子程序接口是汇编语言,为了编写方便,同时使程序框架明了,编写了一个IAPLIB.A51汇编语言接口函数库和IAPLIB.H头文件。在程序中加上IAP.H头文件,调用固件程序时就不需在C51程序中嵌入汇编,而是像调用C语言函数一样简单,这大大简化了编程。

FPGA设计

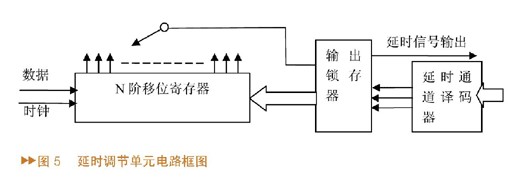

FPGA主要设计了DECODE延时通道译码器、CS片选信号控制器、N阶SHIFTER移位寄存器。其中译码器用于完成对单片机并口送来的数据进行通道、时间参数的分离,用通道参数进行寻址和译码,这是一种简单的译码逻辑和触发电路。N阶移位寄存器用于完成对信号进行N阶的延时处理,是延时处理的核心单元。单路信号延时调节的基本框图见图5。

延时通道译码器将单片机并口送来的延时参数送入锁存器,同时输出控制电路将移位寄存器对应的延时阶切换到输出端。从不同的阶引出信号即可获得不同的延时量。控制时钟和移位寄存器的阶数决定了延时步进调节精度和延时调节范围。如果定时模块有N个信号通道,每个定时模块集成N个完全相同的延时调节单元,就可实现独立调节各个通道信号延时大小的功能。集成的延时调节单元越多,占用可编程芯片的资源就越多,这可以根据实际需要选择可编程逻辑器件。

FPAG软件的设计采用“自顶向下”、“软硬兼施”的设计方法,主要的各单元设计采用VHDL语言描述完成,而整个多路信号的延时功能处理采用图形输入设计方法。软件设计完成后,根据电路原理图进行引脚锁定,然后启动编译程序来编译项目。编译器将进行错误检查、网表提取、逻辑综合和器件适配,然后进行行为仿真、功能仿真和时序仿真。最后通过编程器方式将POF文件下载到EPROM中。加电后,FPGA将EPROM中数据读入片内编程RAM中,完成配置,从而生成硬件电路。

模块功能调试实现

模块在调试中出现P89C51RD2有时上电程序运行不正常,读取程序空间是空的。但是只要上电工作起来,就恢复正常。怀疑由于上电复位时序混乱,造成误调用固件擦除芯片子程序。采用专用复位芯片替换电容电阻加二极管的复位电路,使问题得到了解决。同样,在单片机正确送数情况下,FPGA上电出现不能正常恢复预设好的延时信号,信号总是零延迟(第一次上电,单片机数据存储空间内没有数据,信号就处于零延时状态),但在工作状态下,能够很好地实现延时调节。怀疑这种情况是因存在复位问题而导致,但专用复位芯片不能解决问题。经多次检查程序,发现硬件语言程序中触发语句是电平触发,改写为脉冲上升触发后问题得以解决。

结束语

采用单片机和FPGA设计的延时调节模块,硬件结构简单,设计集成度高。软件方面,单片机程序将C语言和汇编语言很好地结合,FPGA充分发挥了硬件语言易改变电路结构和算法的优越性。提高FPGA中移位寄存器的时钟频率,同时相应增加移位寄存器程序输出阶数,可实现更高精度的延时步进调节和增大延时调节范围。因此可以在不改变模块硬件结构基础的上,通过软件升级来提高模块的性能,从而扩大模块的应用领域。

-

FPGA

+关注

关注

1600文章

21281浏览量

592868 -

单片机

+关注

关注

5998文章

43948浏览量

620562 -

寄存器

+关注

关注

30文章

5020浏览量

117630

发布评论请先 登录

相关推荐

利用单片机和FPGA实现系统中可延时调节模块的设计

利用单片机和FPGA实现系统中可延时调节模块的设计

评论