虽然系统级芯片(SoC)的架构师们已了解嵌入式FPGA(eFPGA)内核能如何为他们的ASIC/SoC设计增加价值,甚至是在规划出一个具体应用之前就了解,但可能还不清楚如何开始进行一次评估。Achronix将该阶段称为准备阶段或者Phase Zero——这是一个客户去规划其应用概念的评估期,客户可以通过使用Achronix的工具和模型来对这些概念进行测试。

以下是一种非常实用的方法,可以帮助设计人员去决定eFPGA是否是其下一代SoC的正确选择。

为什么会考虑使用eFPGA

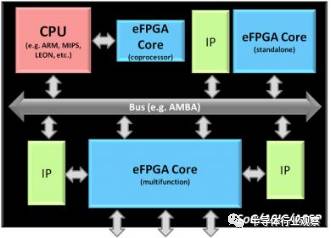

设计人员通常会遇到各种各样的计算处理问题,常用的解决方案都是在SoC中嵌入CPU或GPU,然后依靠外部的分立FPGA来进行加速。通常情况下,推动SoC设计团队去探索嵌入一个可编程阵列结构的主要动力是增加可用来解决问题的技术,使用传统方法去解决这些问题既棘手又成本高。

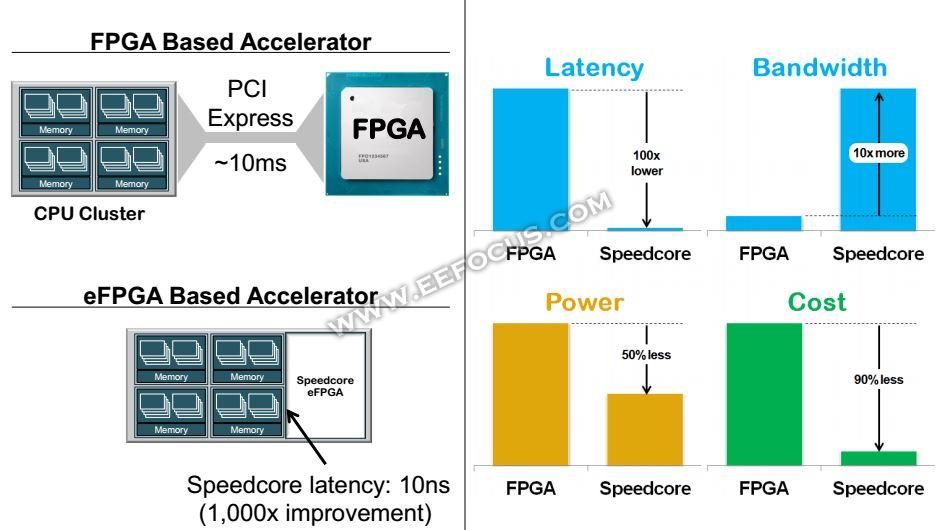

利用已经在多种ASIC设计中得到验证的eFPGA半导体知识产权( IP)产品,可支持SoC开发人员为其解决方案增加逻辑可编程能力,从而设计出能够适应多种应用的同一款器件。在SoC中嵌入一个可编程硬件加速器不仅具有与之俱来的系统级优势,eFPGA还可为SoC设计人员提供其它优势。例如,eFPGA可提供与应用相匹配的存储器、查找表(LUT)和数字信号处理器(DSP)单元模块等个性化组合。eFPGA还可以改善带宽、信号延迟、延迟时间和功耗,最重要的是成本方面的节省。除了这些优势以外,随着采用eFPGA后对电源和冷却需求的降低,电路板的设计也变得更简单。最终,系统的物料清单(BoM)成本也降低了,这是因为不再需要独立的FPGA芯片以及诸如电平位移器和稳压器等所有支持它的器件了。

一旦决定采用eFPGA途径,潜在客户心中的下一个问题都差不多是“先不要在意数据手册,重要的是我该如何评估Speedcore eFPGA IP的能力是否可解决我的问题?”

Phase Zero准备阶段,也是合作的第一步

通常情况下,Achronix的客户是通过了解设计流程来找到对Speedcore eFPGA IP的“感觉”而开始了这个过程。该过程从使用Achronix的ACE设计工具开发样例设计开始,其中已经准备好了客户要求的许多核心功能。该步骤有助于客户去熟悉Speedcore的设计流程和可用于支持他们自己设计工作的资源。这个流程有助于客户进一步清晰Speedcore IP在其潜在ASIC设计中的设计理念,并且在获得最终解决方案之前对功耗和性能设定期望值。

准备阶段很快就发展成为高度协作参与阶段,该阶段可通过IP和设计流程培训、咨询问答环节、及应用讨论来明了客户对Speedcore eFPGA的评估。此项交互性工作理应共享文档、工具、专业知识和详细的技术资料,因而在Achronix和客户之间需要签署一份相互保密协议(NDA),以保护大家的知识产权。一旦NDA完成,Achronix将为评估人员提供登录认证信息来允许他们去下载ACE工具并激活评估用的许可。

ACE包括一个经Achronix优化的Synopsys Synplify Pro软件,以及对Speedcore IP的全面支持。为了帮助评估,ACE工具在下载时附带了两个样例性的Speedcore实例,可以用于所针对的样例设计。这两个样例实例拥有不同的面积大小和资源数量(BRAM、LUT等等),以便于支持ASIC设计团队去将他们的设计编译到一个Speedcore eFPGA中,从而更好地、更深入地了解设计流程和性能。

设计人员需要大量的反馈——ACE设计工具会生成多个有关性能、功耗和资源利用率的报告,也包括各种用于版图设计、布局和布线、位流数据生成、调试支持、静态时序分析、以及自动功能和时序仿真的工具。Achronix的应用团队将在整个过程中提供培训和支持。

面向金属堆层的逻辑综合

使用ACE软件工具,客户能够通过RTL逻辑综合对Speedcore IP进行基准测试,目标是两个通用Speedcore样本实例中的一个。通常,该过程是在Achronix应用团队的帮助下执行的。在这个阶段,评估人员通常会收集资源使用率,及最高频率(fMAX)和早期的功耗集合文件。

一旦有了从初步评估中获得的数据,客户就能够确定他们自己独特的Speedcore实例所需的、合适的资源组合——即一个能够满足他们准确需求的实例。Achronix则以预计的芯片面积和IP的纵横比、静态功耗分布图、配置时间和可编程单元模块的精确配比作为回应。影响Speedcore实例的这些早期面积评估的变量包括设计元素本身、客户在性能和功耗之间的权衡、及客户的目标工艺节点和金属层数。

查找表和逻辑存储器已经演变

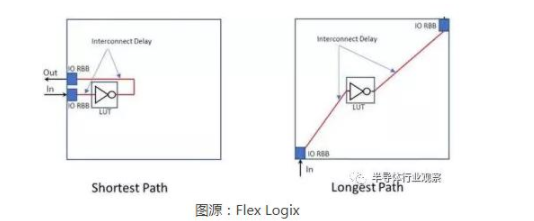

不同FPGA阵列结构之间的硬件差别一直存在。Speedcore eFPGA阵列结构基于4输入查找表,而与其它FPGA供应商的6输入查找表架构截然不同。使用4输入查找表是一个深思熟虑的选择,因为经验数据表明4输入查找表方案可为绝大多数当代的可编程逻辑应用提供最佳性能,并同时兼顾到芯片面积。

另一个显著区别是Speedcore阵列结构的分布式存储器。Speedcore逻辑RAM(LRAM)单元模块为4096位(被配置为128x32),使其比其他竞争对手产品所采用的分布式存储器协议更大,因而是诸如缓冲任务这样的中型应用最理想的选择。事实上,Speedcore LRAM已经被证实特别适用于各种各样的联网和多媒体功能,包括包管理和视频处理。并且通过提供块随机存储器(BRAM)和行业领先的LRAM,Speedcore存储器单元模块有助于设计人员去选择合适的存储器配置,来为其个性化的Speedcore实例优化其中每平方毫米片芯上的性能。

原始设计转换和RTL

对于eFPGA的客户来说,从以前面向分立FPGA芯片的RTL开始不是很少见的,而且它们通常还针对某一特别的FPGA供应商的架构进行优化。为了将这些代码重新定向到Speedcore架构上,可以使用Achronix提供的IP库来帮助客户将原有的Intel/Altera和Xilinx的设计转换为面向Achronix架构的设计。此外,任何最初打算用于标准单元实现的RTL都可以在目标Speedcore eFPGA上工作,但将受益于为Speedcore架构去优化代码的努力。客户可以查阅一组已发布的代码写作最佳范例,这样就能更高效地使用Speedcore逻辑、存储器和DSP资源。

整个过程密切合作

Achronix的应用团队经常深度参与到Speedcore客户的项目中。这种参与是Achronix和ASIC团队之间的协同评估努力的一个正常组成部分,并有助于解释设计结果,从而推动功耗、编译时间、配置时间和性能方面的进一步改善。

准备阶段只是引入Speedcore的开始,它支持设计人员去充分探索使用一个或多个定制化Speedcore实例去部署SoC的益处。一旦准备阶段完成(可控制在仅仅3周之内),剩下的就是推动设计步骤向前,也就是完成授权许可协议。这样的一份协议(包括条款、条件和授权时间)实际上与半导体行业内去购买嵌入式CPU、基于标准的电路单元模块和大多数其它嵌入式IP的许可是一致的。简而言之,确定一款Speedcore eFPGA是否是您下一个SoC开发项目的合适选择,就是一个直接明了的、由Achronix团队密切支持的评估过程。

-

FPGA

+关注

关注

1600文章

21281浏览量

592851 -

soc

+关注

关注

38文章

3737浏览量

215580 -

芯片设计

+关注

关注

15文章

888浏览量

54394 -

efpga

+关注

关注

1文章

31浏览量

15616

发布评论请先 登录

相关推荐

浅谈集成FPGA的两种方式:eFPGA(SoC)& cFPGA(SiP)

SoC设计中嵌入FPGA(eFPGA)内核实用评估方法

SoC设计中嵌入FPGA(eFPGA)内核实用评估方法

评论