1引言

逻辑分析仪的测试对象是数字系统中的数字信息[1]。为了满足现代数据域的检测要求,逻辑分析仪应具有高的采样速率和足够多的输入通道。本文基于虚拟仪器的概念,主要论述以PC586为基础400MHz/102通道逻辑分析仪设计原理和方法,重点阐述系统控制电路设计和系统软件设计。

2虚拟逻辑分析仪体系结构

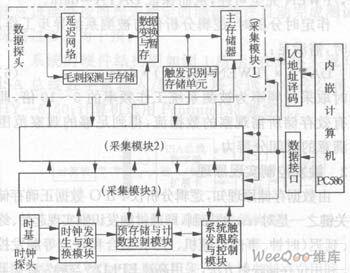

图1为PC环境下的400MHz/102通道虚拟逻辑分析仪控制与采集系统总体构成原理框图,主要包括数据采集、探头、触发跟踪、时序变换与生成,测试接口等部分。该系统输入采集由3个模块构成,每个模块有32个数据通道(另附加2个时钟通道),采用完全相同的功能结构。第3个模块附加了时钟输入与输出、控制等功能。采用该结构的主要原因,一是避免主采集板过大,元件过密造成散热方面的困难(因高速工作的器件较多),二是系统结构灵活,可以根据需要选32、64、96路组态方式。

该逻辑分析仪的控制和管理、数据处理以及数据显示卢内嵌计算机完成。因此,系统硬件的设计主要集中在高速数据捕获以及与微机的接口,而软件设计主要在系统管理、数据的后处理及数据显示。

图1 400MHz/102通道虚拟逻辑分析仪原理框图

3系统硬件设计

400MHz/102通道虚拟逻辑分析仪中的高速数据捕获是由控制电路完成触发控制、数据存取控制而实现的,控制电路同时实现与微计算机的接口。

3.1数据存储原理

作状态分析时,逻辑分析仪与被测系统同步工作。为了使存储器存储的状态数据与被测系统运行的数据流一致,则应满足:

DATA*/FWEN=f(sclk,trw,dtc)*data(1)

式(1)中,DATA为逻辑分析仪存储的数据;/FWEN为逻辑分析仪主要存储器FIFO的写使能控制;sclk为状态(外部)时钟;trw为触发字;dtc为数据控制;data为被测系统数据。由式(1)知下式:

DATA=data(2)

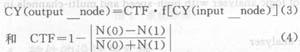

成立的条件是/FWEN信号与sclk、trw、dtc信号必须符合严格的关系。根据数字系统可测性设计中可控性理论,应用CAMFLOT[2]法(Computer Aided Measure For Logic Testability),有:

式(3)~(4)中,CY为可控程度,其值ε(0,1);CTF为可控传递因子;N(0)、N(1)为在电路输入端加所有不同输入值时,电路输出端出现“0”和“1”的总次数。由式(3)知,当可靠置位sclk、trw、dtc等控制信号,可计算出:

CY(/FWEN)=1(5)

即,/FWEN完全可控,从而保证DATA=data。

作定时分析时,逻辑分析仪与被测系统异步工作。此时,需满足:

DATA*/FWEN=f(trw)*data (6)

同时取采样频率为被测系统工作频率的5~10倍,即可有效存储所需观察的数据流,得到足够的观察范围和满意的时间分辨力。

3.2触发控制实现原理

由数据存储原理知,逻辑分析仪FIFO数据正确存储的关键之一是对trw的控制,即通过触发识别实现起始、终止、延迟(时钟、事件)、随机、序列、组合和限定等触发控制。利用位存储映射方法,采用高速EPLD[3]与触发存储器结合,设计的实现触发控制的原理框图如图2所示。

图2中,D0~Dmk-1为被测数据。触发RAM数据位宽为n,地址宽度为k,个数为m,故可观测的数据流的宽度为m·k。当k≥n时,最大序列触发或组合触发识别级数L为:

L≦2n-1(7)

图2 触发控制实现原理框图

4系统软件设计

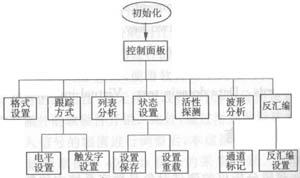

利用图像界面操作系统Windows和以Windows为基础的可视化程序设计平台C++Builder,软件由15个窗体加5个单元文件组成,各主要窗体之间的关系如图3所示。

图3 系统软件各窗体及相互关系

5结束语

逻辑分析仪结构复杂,技术要求高。本文所述的基于虚拟仪器概念的设计思想和方法,因部分硬件功能软化而使硬件电路大为简化,同时采用了EPLD器件,从而降低了仪器成本,提高了仪器的可靠性和性能,且功能易于扩展。400MHz/102通道逻辑分析仪已于2000年12月28日通过了信息产业部军工预研局主持的技术鉴定。

-

逻辑分析仪

+关注

关注

3文章

200浏览量

22909

发布评论请先 登录

相关推荐

400MHz/102通道虚拟逻辑分析仪控制与采集系统方案

400MHz/102通道虚拟逻辑分析仪控制与采集系统方案

评论