随着IC产业的发展,IP核的需求越来越高。微控制器MCU(Micro Control Unit)是嵌入式系统的核心,8位MCU IP核具有很高的通用性和灵活性,广泛地应用于工业控制、机械设备、家用电器以及汽车等各个领域。本文设计的MCU IP核与Microchip公司的PIC16C57完全兼容。MCU IP核采用哈佛结构,内部单元可简化为时序控制和数据通道两部分。时序控制部分为数据通道提供控制信号,控制数据流动方向以及数据通路的选择,它是IP核的指挥中心;数据通道部分在控制部分的控制下,具体实现MCU IP核的指令功能,它是影响MCU性能、功耗等因素的关键,是整个芯片设计的重点。

本文在设计该款MCU IP核的数据通道部分过程中,提出了一种特定的数据通道模型;最后,通过对整个MCU IP核仿真综合,对该数据通道模型进行了验证。

1 、数据通道模型及数据总线Verilog HDL模型

1.1数据通道模型结构图

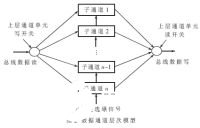

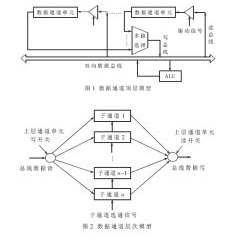

本文设计的MCU数据通道模型包含各数据通道单元及单条双向数据总线。其中数据通道单元主要由特殊功能寄存器、通用寄存器及运算单元ALU等电路组成,每个通道单元还可再分为多个子通道单元。数据通道顶层模型如图1所示,数据主要在数据总线及各数据通道单元中流动,由一条双向数据总线完成每个数据组元的读写操作,充当每个组元源总线及目的总线双重功能,并由特定电路完成总线数据的读写操作。该数据通道模型的最大特点为:通过n个子通道选择信号,各数据通道单元内部可再分为n个子数据通道,由1/n译码器实现每一个时刻只有一条子通道选通。上层的数据通道控制信号仍然有效,作为子层数据通道的公共开关。依次类推,该数据通道模型可以是多层的。数据通道层次模型如图2所示。

数据通道模型内数据的流动在时间轴上是时刻向前的,而数据流动的轨迹则呈现为相互环绕的螺旋形。

1.2 内部数据总线的Verilog HDL模型

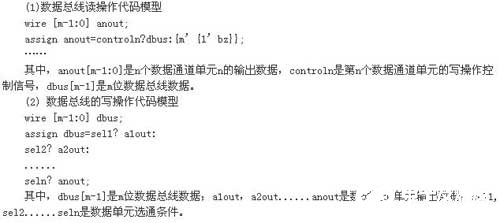

数据通道模型中内部数据总线分别由三态门和多路选择器实现读写操作,使用特定的硬件描述语言Verilog HDL代码模型进行描述。对于挂接n个数据通道单元的m位数据通道内部数据总线,读、写两种操作的Verilog HDL代码模型分别表示如下[3]:

2、 设计实现

本文以数据通道单元ALU为例介绍数据通道模型的层次结构。ALU是MCU IP核的运算单元,是数据的加工处理部件,是数据通道中最特殊的数据通道单元。它实现加、减、与、或、异或、非、左移、右移、半字节交换等九种运算,其中前五种是双操作数操作,其余四种是单操作数操作。对于双操作数操作,ALU数据通道单元一边采用两条两个源操作数数据通道,另一边采用一条目标操作数数据通道;而单操作数操作仅需开启一条源操作数数据通道。

本文的ALU采用低功耗设计。通过控制部分译码得出ALU主要实现四种运算:算术运算、逻辑运算、移位运算以及半字节交换运算。本文通过加、减操作复用一个8位超前进位加法器,将ALU模块分为8个运算单元,构成8个子数据通道。通过对ALU子数据通道选通信号aluop[2:0]进行译码对8条子通道进行选通,如表1所示。在系统复位或者不工作时,各运算单元处于休眠状态;在每条指令的执行周期,ALU中8个子数据通道始终只有一条子数据通道处于选通工作状态。不同类的指令对应不同的数据通道,把对ALU运算的控制转化为对ALU内子数据通道的选择,降低了ALU整体功耗。

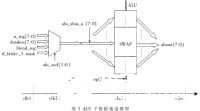

一般来说,数据通道的选通由选通信号控制,而数据通道的开启必须由整个MCU IP核控制部分产生的四相不重叠时钟节拍控制,分别为clk1、clk2、clk3、clk4。时钟节拍不参与数据通道的选择,所起作用只是数据通道的开启。数据通道内数据的流动是有方向的,本文中数据流动的方向性体现为不同时钟节拍控制的不同数据通道的开启。以单操作数指令半字节交换指令(SWAP)为例说明,半字节交换指令只需开启一条源操作数通道。如图3所示,控制部分在clk1时取出指令,产生控制信号,进入数据通道操作;在clk2时,在存储单元中选择源操作数写入数据总线,开启ALU运算单元的源操作数alu_xbus_a[7:0]数据通道,此时内部双向数据总线充当ALU源总线;在clk3时,根据ALU模块子通道选通信号aluop[3:0]选择ALU功能模块SWAP,开启源操作数进入ALU进行半字节交换运算的数据通道;在clk4时,将ALU运算单元的运算结果aluout[7:0]通过数据总线写入到各目的数据通道单元中,即开启目的操作数数据通道,此时内部双向数据总线充当ALU目的总线。

需要说明的是,图3中数据databus[7:0]来自数据总线,由数据通道单元特殊功能寄存器和通用寄存器提供数据。其中特殊功能寄存器包括F0间址寄存器、F1实时时钟/计数寄存器RTCC、F2程序计数器PC,F3状态计数器STATUS、F4寄存器选择寄存器FSR以及F5、F6、F7 I/O寄存器。可以向下再分为8条子数据通道,子通道选通信号为fsel[2:0],而上层数据通道开关控制信号为rf_spr_re、rf_spr_we,即特殊功能寄存器读写控制信号。其具体实现与ALU数据通道单元类似,这里不再赘述。

在该款MCU IP核数据通道模型中,数据总线全部采用本文所述的Verilog HDL代码模型描述。基于中心国际SMIC 0.35μm工艺库(工作电压为3伏),使用Synopsys公司VCS和 DC对该款MCU IP核进行了仿真综合,并进行了功耗分析。综合分析结果得出,该数据通道电路结构规整,设计得到了简化,总体功耗约为49.5980mW,实现了低功耗设计。

本文使用固定电路结构描述内部数据总线,通过特定层次化数据通道模型的设计,体现了自顶向下(Top-Down)的设计方法,降低了整个MCU IP 核设计的复杂度,缩短了设计周期。该设计适用于大规模系统芯片开发设计。

责任编辑:gt

-

mcu

+关注

关注

146文章

16011浏览量

343545 -

嵌入式

+关注

关注

4981文章

18274浏览量

288361 -

仿真

+关注

关注

50文章

3872浏览量

132148

发布评论请先 登录

相关推荐

使用Robei利用verilog语言做ALU设计

在做FFT IP核的仿真时遇到问题,居然不能生成FFT的仿真文件,求解答

使用Robei利用verilog语言做ALU设计

基于层次模型的USB2.0接口芯片IP核固件的设计

以太网在MPSoC中的数据通讯实现

基于FPGA的数据采集控制器IP核的设计方案和实现方法研究

基于VHDL语言的IP核验证

Xlinx IP Core实现FFT变换——为什么你的matlab数据无法严格比对?

基于FPGA的PCIe总线接口的DMA控制器的实现并进行仿真验证

MCU IP核特定层次化数据通道模型的设计及仿真验证分析

基于MCU IP核ALU单元实现数据通道模型的设计并进行仿真验证

基于MCU IP核ALU单元实现数据通道模型的设计并进行仿真验证

评论