先进的串行通信标准外围组件互连(PCI)最初用于个人电脑,以克服限制并行总线标准带宽的挑战如时钟和数据信号偏移。PCI作为串行互连,还有助于避免实现并行数据链路所需要的高引脚数。

后来PCI升级到PCI Extended (PCI-X),然后到PCI Express (PCIe),这是一种点对点的全双工串行计算机扩展总线标准,取代了较早的标准并支持更快和更灵活的方案。

PCIe通过三代发展演变,现已能满足更高速度和数据吞吐量。第一代PCIe 1.1采用2.5GT/s(千兆传输每秒)的原始数据传输速率和8b/10b的数据编码,支持每通路500MB/s的高效的数据吞吐量。PCIe 2.1通过提高传输速率到5.0GT/s增加数据吞吐量到每通道1GB/s。PCIe 3.0通过将传输速率进一步提高到8GT/s和采用更高效的128b /130b编码方案相结合,达到每通路2GB/s的数据吞吐量。

一条PCIe通路包含发送和接收两条不同的通道。总PCIe链路数据带宽可通过增加额外的通路扩展。这灵活性已使PCIe普遍用于服务器、网络附加存储、网络交换机、路由器和机顶盒等应用中。这些应用固有的严格的时序预算和系统挑战对PCIe时钟性能施以严苛的要求。

PCIe指定一个100 MHz的外部参考时钟(Refclk),精确度在± 300ppm以内,用于协调在两个PCIe设备间的数据传输。PCIe标准支持三种范围的时钟分配方案:公共时钟、数据时钟和分离时钟架构。所有时钟方案都要求±300ppm的相同的时钟精确度。

在公共时钟架构中(图1),单个Refclk源被分配到发送器和接收器。这种时钟方简单而普遍用于成本敏感的商业应用。支持扩频时钟(SSC)可最大限度地减小电磁干扰(EMI)敏感的应用中的电磁辐射。

图1:公共时钟架构。

在数据时钟架构中(图2),时钟信号被嵌入并从数据信号中恢复。时钟恢复需要额外的硬件,以在接收端从信号流提取时钟。数据时钟架构也支持SSC。

图2:数据时钟架构。

分离时钟架构(图3)通过在每一PCIe端点使用分离时钟源,而省去向所有通道发送时钟。该标准允许在时钟间± 600ppm的频率间隔,以便每一Refclk仍然保持± 300ppm的频率精确度范围。因为时钟是独立的,接收器的有效抖动是发送器抖动和接收器锁相环(PLL)的和的平方根(RSS)。这种架构没有指定抖动限制。但可直观地理解为它的抖动预算比共同时钟架构更严格。

图3: 分离时钟架构。

以往,若采用± 300ppm的整个允许的频率幅度,在分离时钟架构中Refclks间允许的有限的频率间隔已阻碍了SSC的采用。但以不同的发射器和接收器速率的时钟是被允许的,在Refclks间的频率间隔高达5600ppm。PCI-SIG正着手起草独立的分离参考时钟独立扩频(SRIS)标准。安森美半导体PCIe时钟发生器符合这草拟标准中说明的SRIS Refclk要求。

系统抖动源和影响

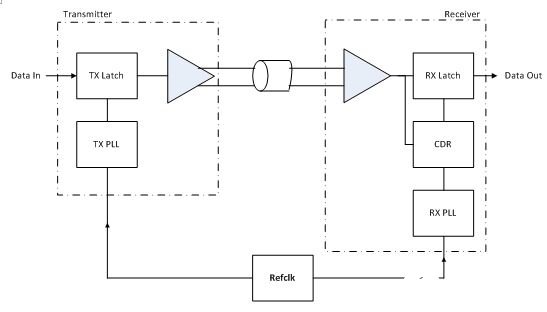

图4显示一个采用公共时钟架构的PCIe x1链路。内部锁相环(PLL)负责复用Refclk达25次,以产生所需的更高频率信号,以通路比特率传输数据。

图4:PCIe x1数据链基本功能块。

PCIe链的整体目标是以高的统计成功确定性从发射器到接收器传输大量数据。为实现此,接收器必须采样由位中心或附近的发射器发出的数据位。在接收器中,时钟/数据恢复块(CDR)产生一个时钟,定期采样数据到锁存器。各种相位抖动源引起样本时序波动。由于样本位置偏离理想位置,误码率增加。

系统中的相位抖动源包括参考时钟抖动、发射器PLL和接收器CDR独立的相转移功能、电源噪声影响,和电缆及PCB空间分散、符号间干扰、串扰和反射的影响。

总相位抖动以皮秒计算,由各种源产生,引起采样时钟和数据位中心间的位移。按照数据眼图术语,误码被定义为相位抖动的累积引起数据和采样时钟间的总相位差超过数据眼宽度的一半,否则被称为单元间隔(UI)。

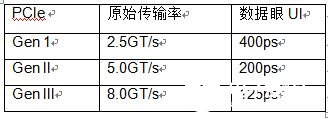

表1显示在PCIe 2.1和3.0中数据传输率更高UI变短,这有效地实行更严格的抖动预算。

表1:PCIe Gen 1到III数据速率和数据眼UI的比较。

低抖动设计

采用稳压电源和校正电路设计可有效地消除电源噪声影响。同样,采用阻抗匹配、高品质板材和优化布线可设计出防止信号完整性问题如ISI和串扰。

参考时钟抖动是最难抑制的。它的影响不仅成倍增加并直接以发送信号传播,而且对接收器信号恢复产生不利影响。

Refclk包含宽范围的频率抖动。接收器只能跟踪这些频率的一个波段。有意义的PCIe系统抖动主要是通过时钟/数据恢复(CDR)模块的传输功能跟踪抖动分量(不滤波)。对于PCIe Gen I、II和III模型,用于计算抖动的数学函数是不同的。

信号抖动由确定性(Dj)和随机(Rj)性内容组成。Dj由非高斯概率密度函数有界的振幅控制。它有特定的起因如干扰、数据依赖和占空比失真(DCD),是可预测的。对于时钟,Dj在相位噪声图中呈现出一定幅度的毛刺。

Rj呈现高斯分布且无边界。它的存在是由于随机现象如热噪声和工艺变异。在时钟中,Rj在特定频率偏移范围呈现出集成的相位噪声。总抖动(Tj)通过卷积法从Dj和Rj计算。

n 取决于BER链(以太网为10-12)

表2描述在特定频带(基于CDR传输功能) PCIe Gen I、II和III系统可接受的Tj值,并比较这些要求与安森美半导体的NB3N51034四输出HCSL/LVDS时钟生成器性能,NB3N51034适用于Gen I、Gen II 和Gen III应用。

表2:PCIe规格抖动限制和PCIe时钟性能。

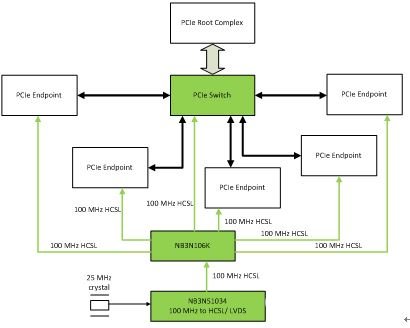

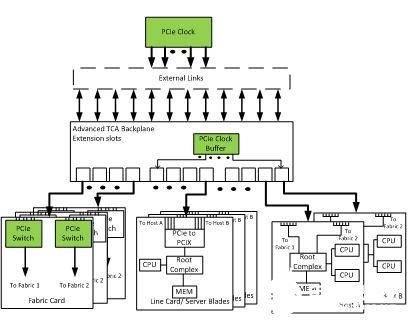

时钟树设计

当设计任何PCIe系统时,考虑到将来的扩展,好的时钟树技术至关重要。恰当的PCIe时钟源的最佳选择、缓冲器和开关取决于系统中内部和外部PCIe I/O(包括以后的扩展)数量,以及速度和带宽要求。图5和图6说明了常用的时钟树架构。在计算系统中,CPU和存储器通过由多个称作PCIe Root Complex 的PCI Express通路组成的集线器交换数据。

图5:典型的计算系统PCIe时钟树。

图6:典型的嵌入式/通信PCIe时钟树。

时钟树通常由多个功能部件组成,包括时钟生成器、扇出缓冲器、零延迟缓冲器和开关。虽然选择具有亚皮秒相位抖动性能的同类最佳时钟源是重要的,以确保符合PCIe规格的最佳性能,但用于分配多个高精度、低相位噪声时钟的缓冲器还必须有低附加相位抖动和低输出到输出偏移(skew)。

安森美半导体提供一系列缓冲器适用于PCIe Gen I、Gen II 和Gen III应用,典型的附加相位抖动低至0.1ps rms(在12 kHz到20 MHz集成),最大输出偏移为100 ps。低电流、多通道PCIe开关与这些精密的时钟和缓冲器一起使用,令单个控制器能管理多个PCIe插槽,如图6所示。

结语

下一代PCIe提供更高的数据传输速度,但对抖动的承受力较低。虽然在PCIe系统内有各种干扰源,如电源噪声和符号间干扰,但参考时钟是难以根除的主要抖动源。因为PCIe标准支持多种时钟分配策略,所以仔细选择低抖动时钟源和时钟树组建至关重要,以符合高速单路或多路PCIe系统的抖动预算。

责任编辑:gt

-

接收器

+关注

关注

14文章

2214浏览量

70656 -

时钟

+关注

关注

10文章

1479浏览量

130304 -

PCIe

+关注

关注

13文章

1083浏览量

80809

发布评论请先 登录

相关推荐

低抖动时钟源和时钟树组建为下一代PCIe提供更快的数据传输速度

低抖动时钟源和时钟树组建为下一代PCIe提供更快的数据传输速度

评论