1 引 言

近年来,以电池作为电源的便携式电子产品得到广泛使用,迫切要求采用低电压的模拟电路芯片来降低功耗。在低压供电条件下, 为了提高运放的信噪比、输入共模电压范围及信号动态输出幅度, 最好是能做到轨对轨。放大器的输出较容易实现轨对轨, 但在输入端实现轨对轨是比较复杂的, 原则上只能是折叠式共源共栅结构才能使输入端包含电源电压的轨, 这种技术是实现所有轨对轨输入放大器的基础。

输入级采用电流控制的三倍电流镜法, 输出级采用浮动电流源控制的前馈甲乙类输出级, 该电路结构可以克服直接将轨对轨输入级、求和电路、甲乙类输出级相连的缺点, 提高了运放的增益, 使输出管的静态电流不随电源电压及输入共模电压的变化而变化, 同时也降低了电路的功耗, 节省了芯片面积。

2 恒跨导Rail- to- Rail输入级

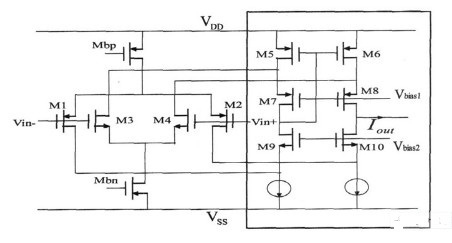

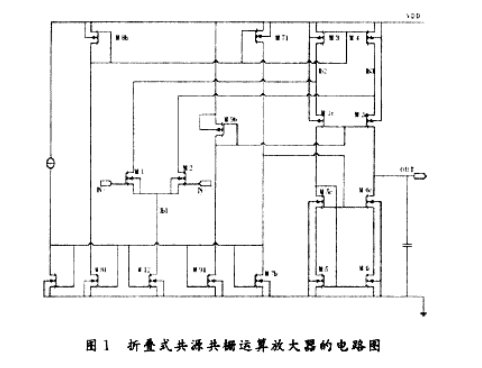

输入级等效跨导的不恒定不仅会降低运放的共模抑制比, 同时也会造成严重的失真, 而且还会给后面的频率补偿带来困难, 一个理想的频率补偿要求输入级的跨导是恒定的。因而输入级设计的关键也就是要使得输入级的跨导在整个输入共模电压范围内都保持恒定。显然MOS互补差分对管不能满足要求。如图1, 这是一种采用电流控制恒跨导的结构, 电路恒定跨导控制部分是由两个电流开关管M7、M8, 两个电流镜M5- M6、M9- M10组成。

每个电流镜的电流比例关系是1:3。当输入共模电压比较低时, 只有PMOS输入对管工作, 电流开关管M 7打开, M 8关闭, NMOS 输入对管偏置电流In流经开关管M7通过M9、M10电流镜放大三倍后与Ip 一起注入PMOS对管, 假设Ip = In = I, 则此时电路跨导等于2√β I; 当输入共模电压比较高时, 只有NMOS输入对管工作, 电流开关管M8 打开, M7关闭。Ip 经电流镜放大三倍后与In 一同抽取NMOS对管的电流, 此时电路跨导仍然等于2√β I; 当输入共模电压在中间时, NMOS输入对管和PMOS输入对管都工作。两个电流开关管都关闭, 此时电路跨导仍然等于2√β I。通过电流开关的控制及电流镜已基本做到在输入共模电压轨对轨的情况下输入级的等效跨导保持恒定。但这种恒定发生在输入共模电压接近电源正轨与电源负轨以及在二者中间,NMOS完全导通或者PMOS完全导通又或者NMOS与PMOS 同时导通的情况下。但是在两个“过渡区”, 由于流过NMOS 输入对管或PMOS 输入对管的电流小于各自恒流源提供的偏置电流, 开关管打开, 并将恒流源提供的偏置电流与流过NMOS 输入对管或PMOS输入对管的电流之差通过电流镜放大三倍后注入到另外两个输入对管, 造成流过NMOS输入对管与PMOS输入对管的电流之和增大, 使电路等效跨导增大, 增大幅度一般为恒定跨导区域的15%。此外该电路要求NMOS管与PMOS管的β相等, 即μnCox (W /L) n =μp Cox (W /L) p, 因此要求(W /L) n / (W /L) p =μp /μn。NMOS管与PMOS管的尺寸应当精确匹配, 但由于工艺以及温度的影响, μp /μn的比值并不是恒定的, 这又会对电路的跨导引入一些误差。并且由于NMOS与PMOS的失调电压不同使电路在整个输入共模电压范围内的失调电压是不同的。但是相比于开关电流方式、冗余差分对法、恒定电压方式、动态电平移位法等电路结构, 该电路电流并没有?浪费#的情况, 降低了运放的功耗, 并且此种电路结构原理简单, 容易实现。

图1 恒跨导Rail- to-Rail输入级。

3 电流求和电路

电流求和电路与输入级的输入管构成折叠式共源共栅结构, 这种技术是实现所有轨对轨输入放大器的基础。

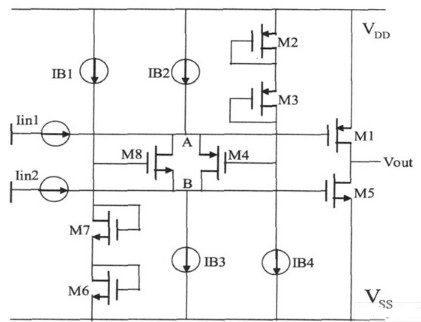

如图2, 电路中的右半部分为电流求和电路, 电流相加电路把两对差分对的输出信号相加, 并且进行双端至单端的转换。由于折叠共源共栅结构具有输出电阻大、增益大的特性, 电流相加电路同时相当于中间增益级。其中M5 - M8 组成低压共源共栅电流镜实现双端到单端的转换, M7- M10与前端的差分输入对构成折叠共源共栅结构。此电流求和电路应当注意连接的极性, 其工作原理如下:

图2 电流求和电路。

当Vin + 增大△V, Vin - 减小△V 时, I1 增大△I, I2减小△I, I3 减小△I, I4 增大△I。

因为I1 增大△I, 所以I9 减小△I, I7 = I9, 所以I7也减小△I; 因为I3 减小△I, I5 = I3 + I7, I7 减小△I, 所以I5 减小2△I; 由于电流的镜像, I5 = I6, 所以I6 也减小2△I; 因为I2 减小 △I, 所以I10增大△I; 因为I6 =I4 + I8, I6 减小2△I, I4 增大△I, 所以I8 减小3△I; 因为Iout = I8 - I10, I8 减小3△I, I10增大△I, 所以Iout减小4△I, 实现了电流求和。

4 Rail- to- Rail输出级

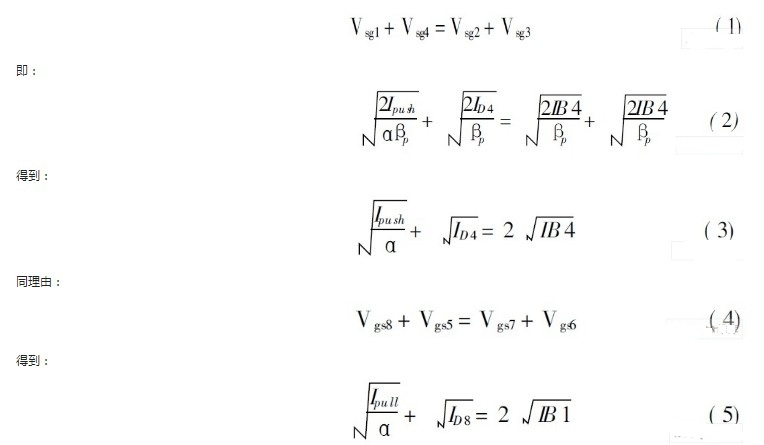

甲乙类输出级可以通过跨导线性电路来偏置,如图3 为MOS 管耦合前馈甲乙类输出级。其中M 1- M4为一个跨导线性电路, M5- M8 为一个跨导线性电路, 它们设置了输出管的静态电流, 其中M 2- M4为输出管M1提供偏置, M6- M8为输出管M 2提供偏置, M4、M8构成浮动的电压源, 此电路结构可以实现甲乙类输出。

图3 MOS管耦合前馈甲乙类输出级。

Iin1和Iin2是同相的交流小信号, 当Iin1 = Iin2 > 0,节点A 和B 电压升高, M5导通, M l截止; 当Iin l =Iin2 < 0, 节点A 和B 电压降低, M l导通, M5 截止。

设M2、M3、M4 的尺寸为(W /L ) p, M l的尺寸为a(W /L) p, M6、M7、M8的尺寸为(W /L) n, M5 的尺寸为a(W /L) n,βn =μn Cox (W /L) n,βp =μpCox (W /L) p, 并且所有的MOS管都工作在饱和区。由电路知:

若0. 5IB2= 0. 5 IB3 = IB1= IB4 = IB, 静态时:

ID 4 = ID8 = IB, Ipu ll = Ipu sh = Iq = aIB; 在工作状态时:

ID 4≠ ID8, Ipu ll≠Ipush。由式( 3)、( 5)及ID 4 + ID8 = 2 IB可以得出:

可以看出, 当推或拉电流的其中一个是静态电流的4倍时, 另外一个仅有静态电流的0. 34倍。

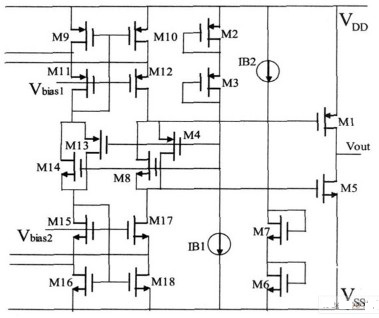

相对于简单的把轨对轨输入级、求和电路, 甲乙类输出级相连, 如图4所示的浮动电流源控制的前馈甲乙类输出级有更多的优点: 首先输入级通过求和电路如果与甲乙类输出级直接级连, 会造成运放增益的降低, 因为输出级中两个控制管的偏置电流与求和电路中的共源共栅器件并联, 因此浮动电流源控制的前馈甲乙类输出级对此问题进行了改进, 它将输出级中两个控制管的偏置电流由求和电路直接提供, 这样不仅消除了运放增益下降的缺点,而且减少了两条支路, 降低了整个电路的功耗, 同时也节省了芯片面积; 此外, 对于普通的前馈甲乙类控制输出级结构中提到的输出管的静态电流随电源电压的变化而变化的缺点, 该电路也很好的解决了此问题。注意到图中与控制甲乙类输出的晶体管的浮动电压源M4、M8结构相同的两个管子M13、M14,这两个管子构成了浮动电流源, 同样, M9、M13、M2、M3组成了一个跨导线性环路, M16、M14、M6、M7组成了一个跨导线性环路。

图4 浮动电流源控制的前馈甲乙类输出级。

由于该结构与控制甲乙类输出的晶体管组成的浮动电压源结构相同, 因此二者对于电源电压的依赖是相同的, 所以消除了输出管的静态电流随着电源电压的变化而变化的缺点。而且注意到浮动电流源还有另外一个优点, 对于直接将控制甲乙类输出的浮动电压源?镶嵌#到求和电路中, 而没有浮动电流源的电路结构, 随着输入共模电压的变化, 求和电路中每条支路的电流也是变化的。由于控制甲乙类输出的浮动电压源的偏置电流就是求和电路中一条支路的电流, 由上面的分析, 可知该电流的大小影响输出管静态电流, 因此输入共模电压的变化将造成输出管静态电流的变化。相比之下, 对于浮动电流源控制的前馈甲乙类输出级, 由于流过浮动电流源的电流是恒定的, 输入共模电压变化引起的电流变化会通过调节M9、M10、M16、M18 管的栅压调节其电流, 由于浮动电压源的偏置电流恒定, 所以输出管的静态电流是恒定的。

5 运放总体结构与仿真结果

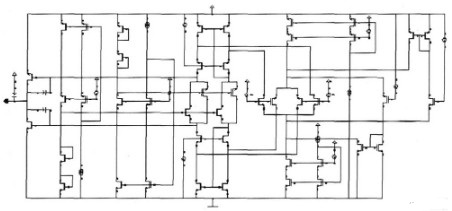

所设计的运放整体电路如图5所示。

图5 运放整体电路图。

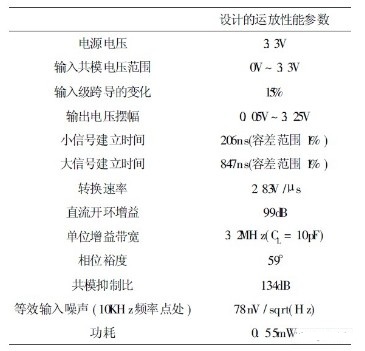

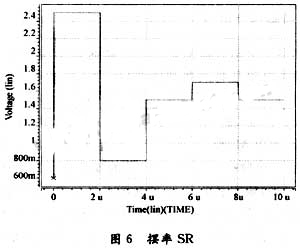

用Spectre仿真器对该运放的各种性能参数进行了仿真。仿真表明在整体输出上能跟随输入, 输入共模电压达到轨对轨, 仅在输入信号接近电源两轨时, 输出与输入间有误差, 其最大误差约为15mV。该运放直流开环增益为99dB, 单位增益带宽为3. 2MH z(负载电容10pF) , 相位裕度59° 。此外通过仿真得到的该运放其他性能参数如表1所示。

表1 运放性能参数表

6 结束语

在比较详细地分析了恒跨导轨对轨输入级、电流求和电路、轨对轨输出级电路的基础上完成了一种结构简单、功耗低、工艺上容易实现的恒跨导轨对轨运放的设计, 其可以广泛地应用于个人通信设备、TFTLCD的电压参考缓冲器、无线局域网设备、各种PDA产品、便携式电气产品等低功耗应用的诸多场合。

-

运算放大器

+关注

关注

211文章

3982浏览量

170666 -

开关管

+关注

关注

4文章

197浏览量

21411 -

电池

+关注

关注

82文章

9792浏览量

123461

发布评论请先 登录

相关推荐

放大器教程:运算放大器基础学习

CMOS两级运算放大器调零电路性能分析

折叠共源共栅运算放大器原理及设计

基于SMIC 0.18m CMOS混合信号的运算放大器设计

基于SMIC 0.18m CMOS混合信号的运算放大器设计

评论