Abstract:串扰是SI设计中较为重要的一个概念,如何在产品设计中保持信号在传递过程中不会受到周围信号的影响,同时不会影响到其它信号线,是确保产品顺利通过测试的关键。串扰的产生,主要是由于相邻传输线间的互电容(Mutual Capacitance)和互电感(Mutual Inductance),这些分布参数使信号在传递过程中将自身携带的电压电流信息部分耦合到相邻的受扰线(Victim line)上。目前常用的抑制串扰的手段,均是采用降低线间的分布参数的原理。如简单的拉开线间距(常见的3W原则)、加防护线、防护地孔等;对于线束间存在的串扰,通常会通过双绞、屏蔽等方式降低串扰幅值。本文将详细介绍这几种常见措施的效果及差异,希望通过不同角度的分析,让读者了解产品设计中的一些方法。

目录

Crosstalk

1、近端串扰和远端串扰

2、串扰模型的建立

3、耦合长度对串扰的影响(多重crosstalk)

4、间距变化对串扰的影响(3W原则由来)

5、防护地线对串扰的影响(Guard Trace Effect)

6、防护过孔对串扰的影响

7、Minimization of Crosstalk

8、ANSYS串扰检查模块

9、线缆间的串扰

参考

1、近端串扰和远端串扰

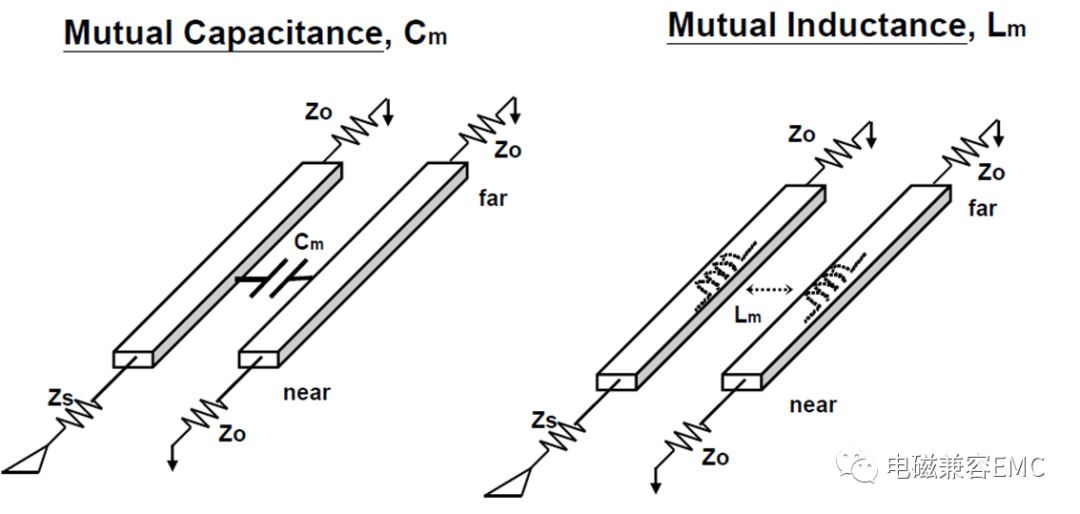

串扰是由一条线到另一条线的能量耦合引起的,耦合的方式主要分为电场(electric field)和磁场(magnetic field)。由于走线之间存在着互容(Mutual capacitance)和互感(Mutual inductance),一条走线上的AC信号便会从这些分布的互容和互感传递到另一根被扰线(victim net)上。

Fig1. Mutual Capacitance and Mutual Inductance

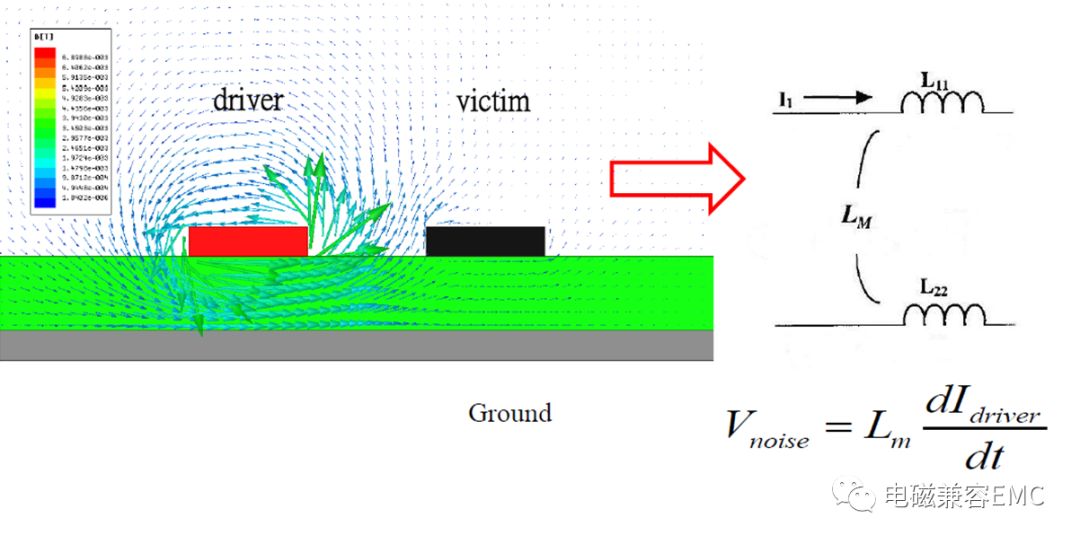

1.1互感

互感通过磁场将噪声电流从一条驱动线引导到相邻的被扰线上,驱动线产生的磁力线穿过被扰线上,行成感应电流。

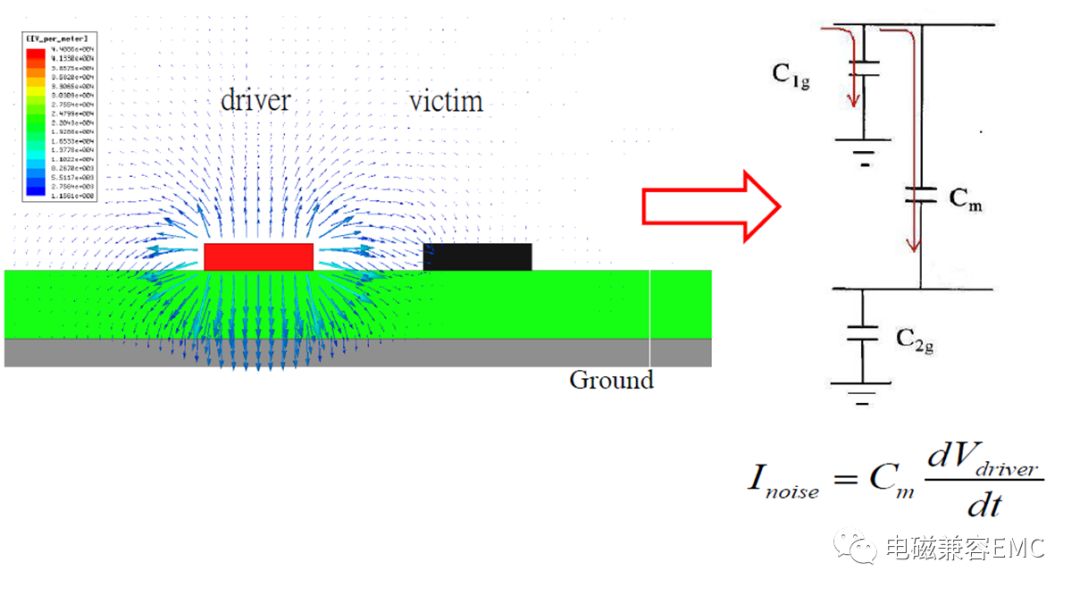

Fig2.Mutual Capacitance

1.2互容

是两导体间通过电场耦合,驱动线上的时变电压信号通过互容在被扰线上引起感应电压。

Fig3.Mutual Inductance

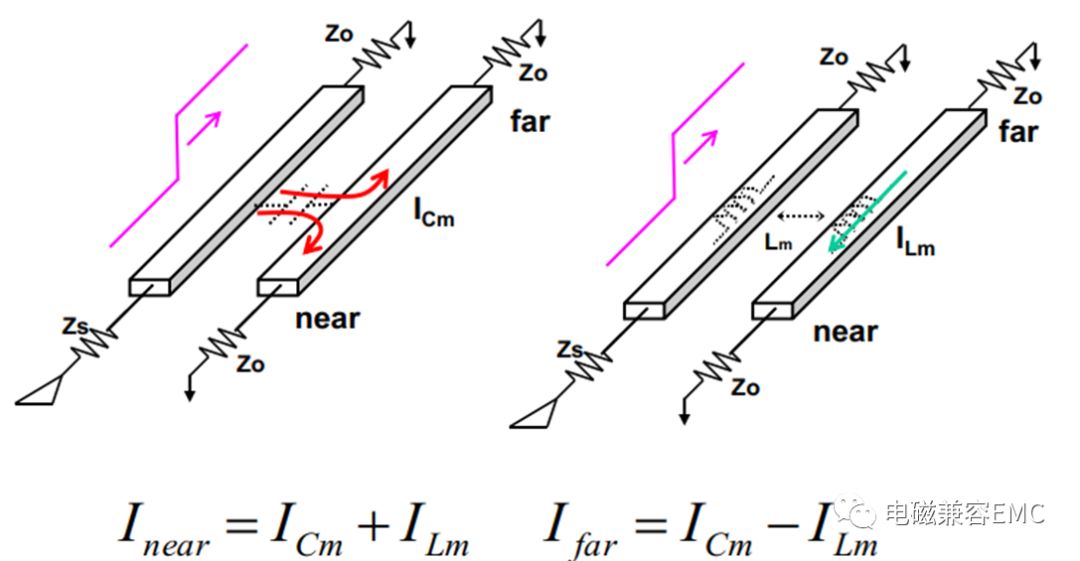

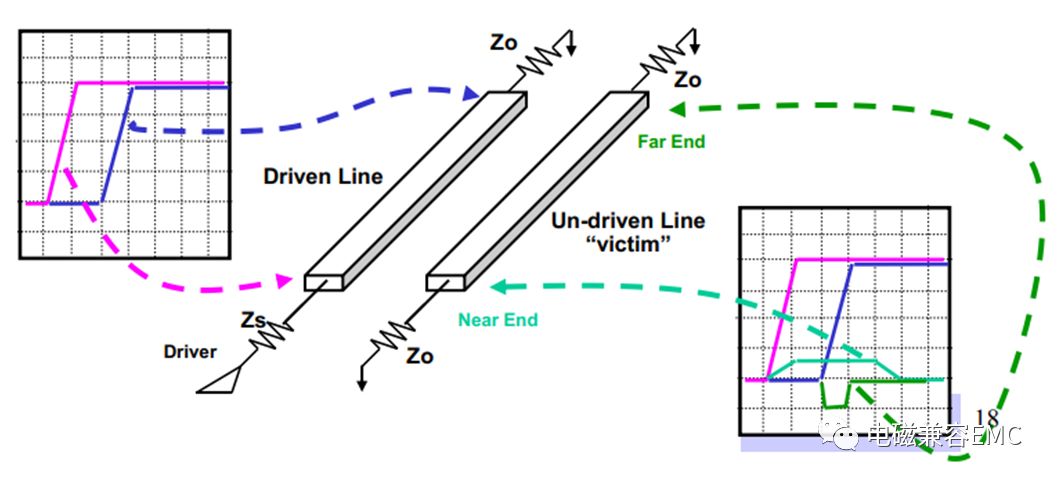

1.3 近端串扰和远端串扰

如图1所示,现实中为了测量串扰幅值,会分别测受扰线两端的噪声情况,为了区分这两个末端,把距离源端最近的一端称为“近端”,而远离源端最远的一端称为“远端”。这两端也可以用信号传输的方向来定义,即远端是信号传输方向的“前方”,近端是信号传输方向的“后方”。在受扰线(victim line)上耦合的噪声分为电流噪声和电压噪声。下图为耦合在victimline上噪声电流的示意图,NEXT近端耦合电流为互感耦合电流与互容耦合电流的和,相反,FEXT远端耦合电流为互感耦合电流与互容耦合电流的差。

Fig4. Coupled Currents

下图为电压耦合示意图,从图4中可知,近端串扰为互容和互感电流之和,所以近端串扰的电压幅值总是正的。而远端串扰为互容和互感电流之差,所以远端串扰不总是负的。其中原因有两个:

Lm的电流大于Cm电流情况

远端为开路的情况下

Fig5电压耦合示意图

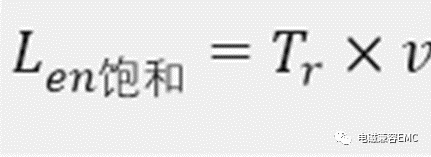

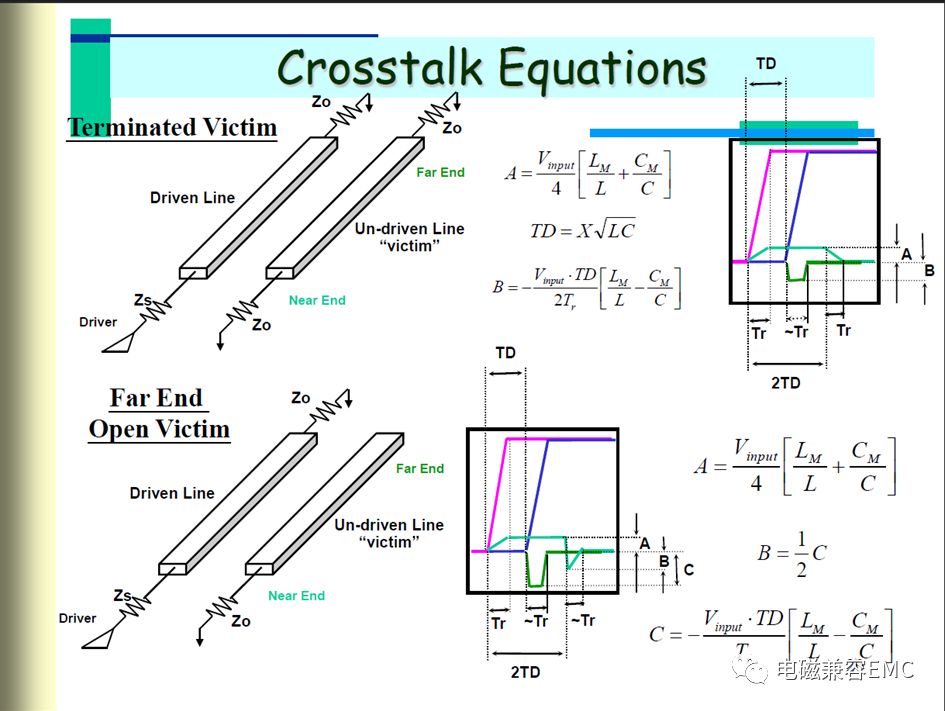

近端和远端耦合电压的描述,下图吴瑞北老师的课件中给出了三种情况下,近端和远端的串扰模型及相应的计算公式。从中可以看出,近端耦合噪声幅值仅与微带线分布参数和驱动电压有关,当耦合微带线截面尺寸和驱动电压电平确定,其幅值便可以确定。而远端耦合噪声的幅值,不仅与微带线分布参数和驱动电压相关,还受时延与驱动波形上升沿时间相关。

Driver pluse在quiteline近端造成一个较长的耦合信号,该信号开始于0时刻,持续时间为2Td,近端串扰信号随着驱动器上升边沿逐步上升,当信号前沿传输了一定长度后,近端的电流将达到一个稳定值不再增加,该长度称为饱和长度。传输线饱和长度Len为:

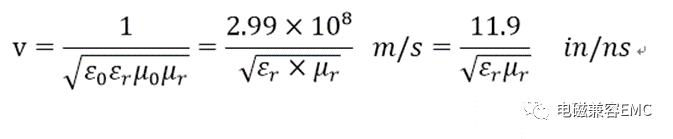

其中为信号上升时间,v为信号在driver line中的传输速度。

Fig6 NEXT和FEXT波形及幅值计算

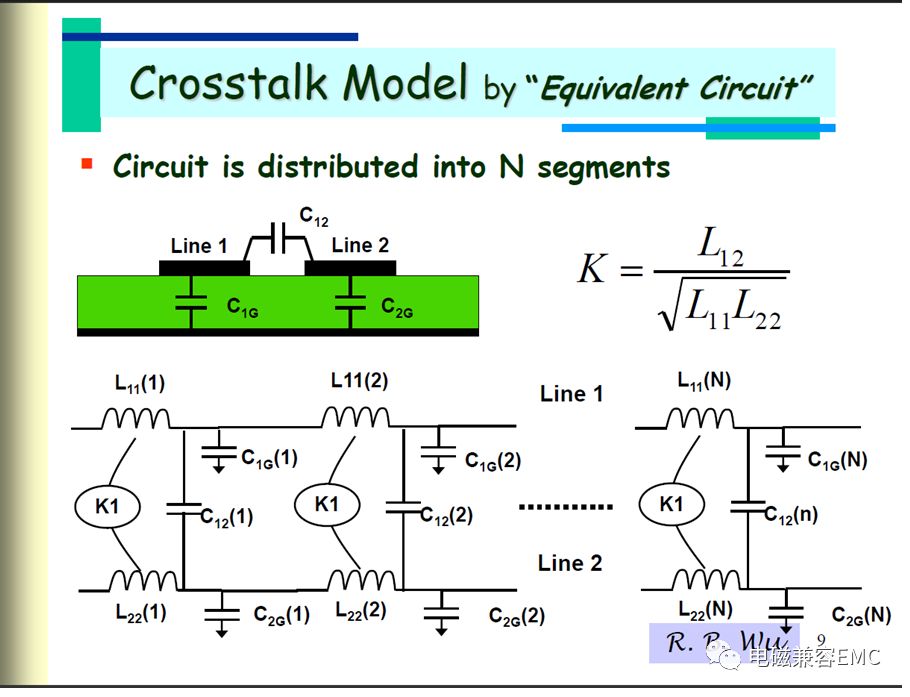

2、串扰模型的建立

因为现实中不存在理想传输线,所以无法实现理想情况下的阻抗匹配,因此可以说反射无处不在。反射的存在,使串扰的分析变得复杂。因此为了降低其影响,需要对所建立的模型进行阻抗设计,尽量降低反射的幅值。

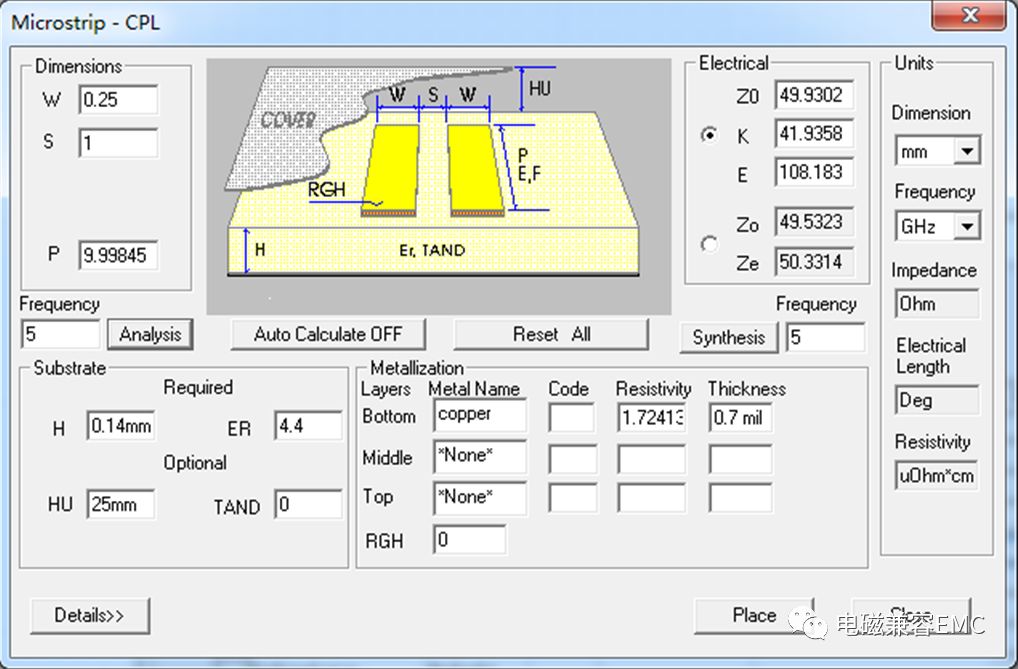

2.1 采用ANSYSMicrostrip-CPL工具进行特征阻抗设计

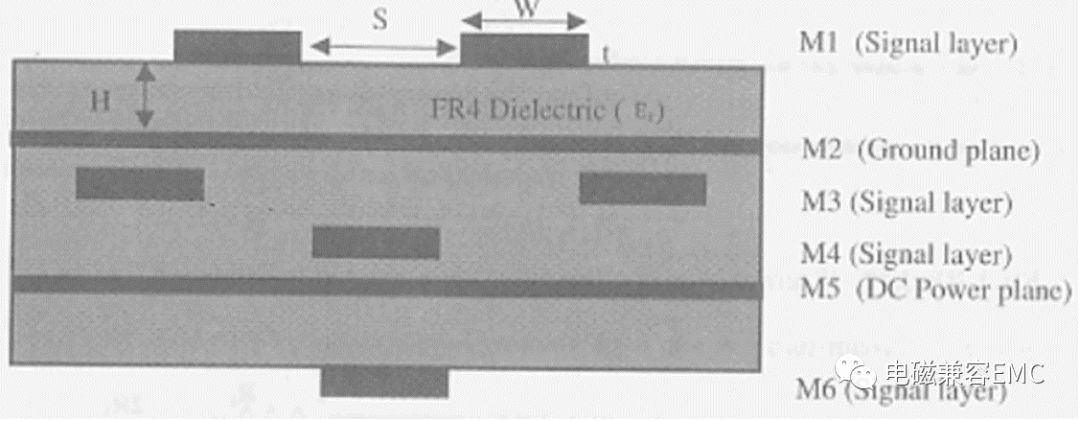

如图1所示,建立端口特征阻抗为49.93Ω的耦合微带线,线宽为0.25mm,距离GND平面高度为0.14mm,介电常数为4.4,长度为50mm。

Fig7.特征阻抗为49.93Ω的耦合微带线参数

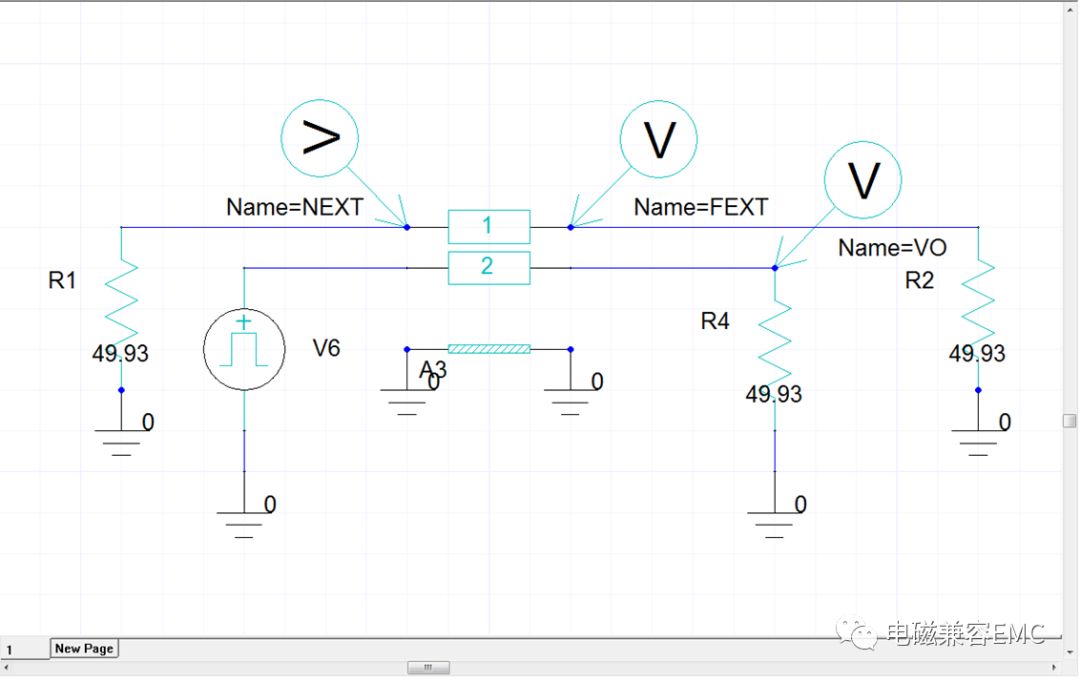

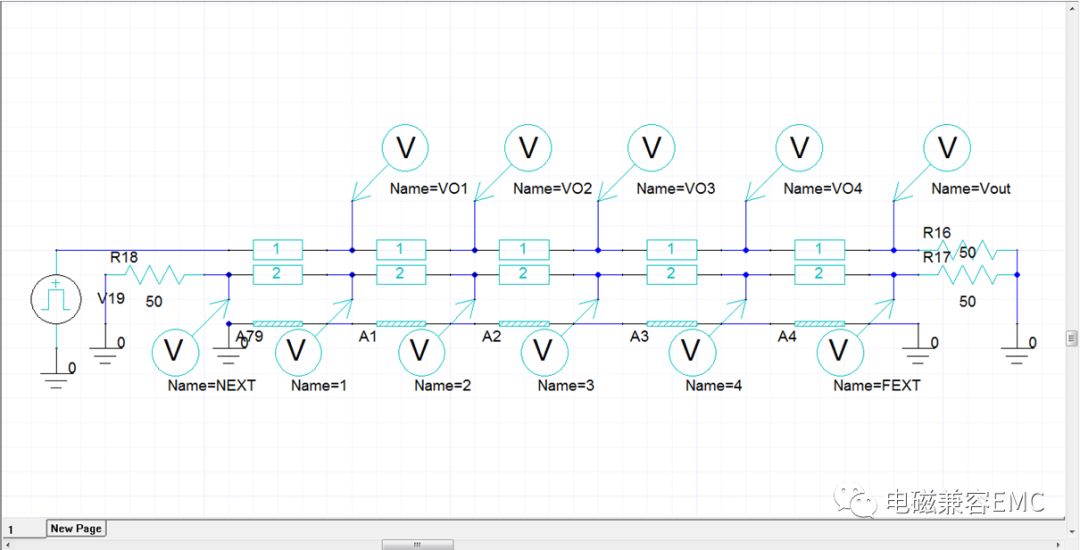

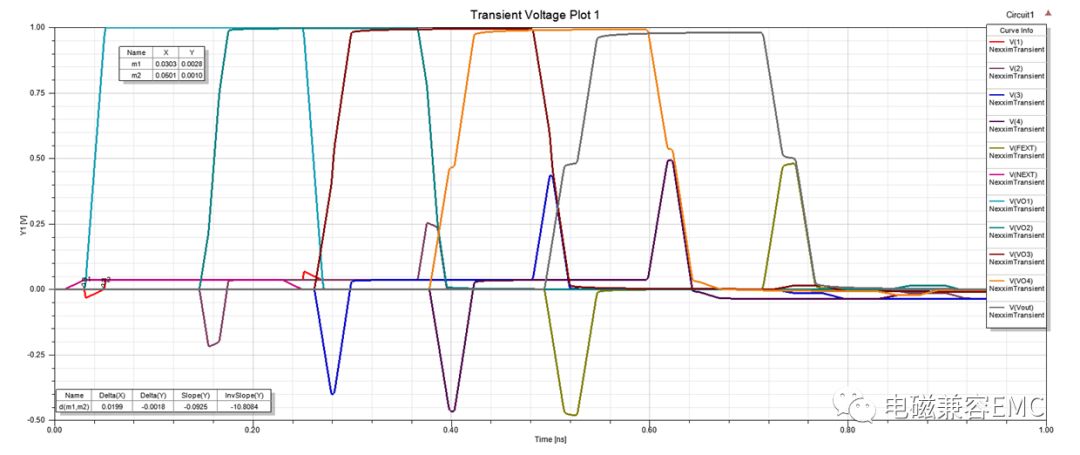

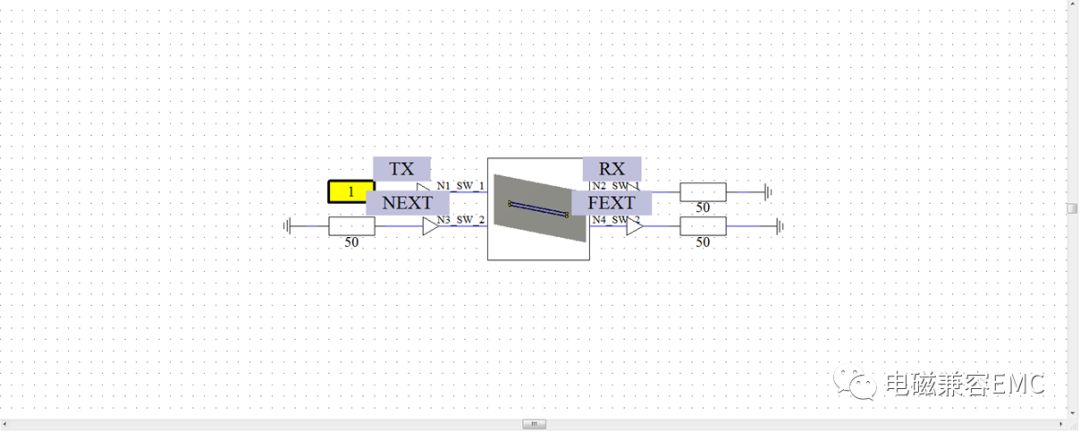

根据前面参数在designer中建立仿真模型,2号微带线为driver line,1号线为victimline,Vo为输出电压,NEXT为近端串扰电压,FEXT为远端串扰电压。

Fig8.耦合微带线仿真模型

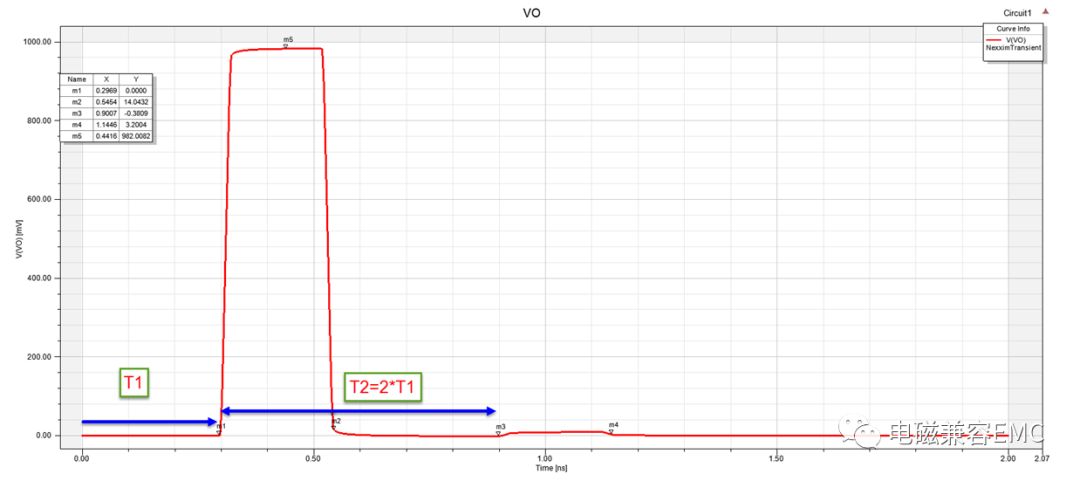

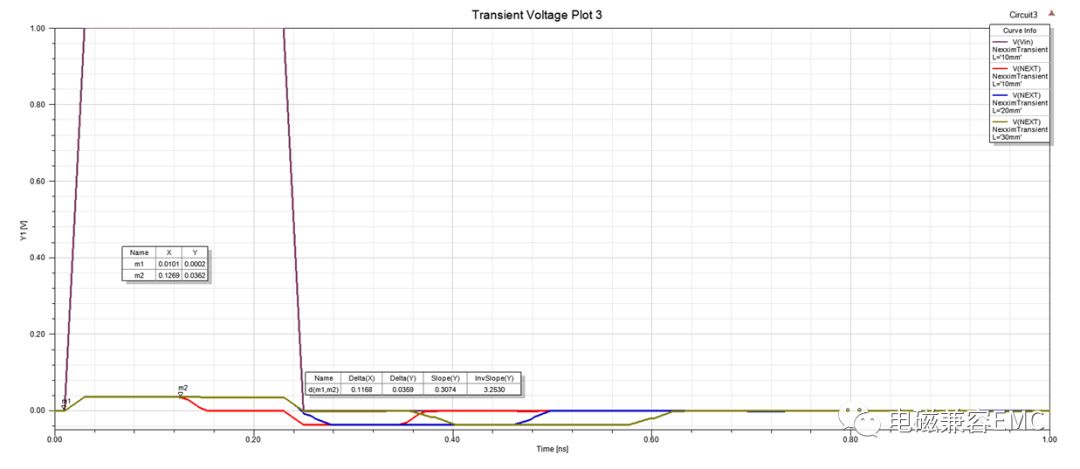

Driver line上驱动信号波形为,电压幅值1V,TR=20ps,TF=20ps,PW=200ps的单脉冲方波。图3为VO端的输出波形,从中可以看出几点,首先传输线产生了18mV的压降。其次,m3-m4间有9.5mV的凸起,这个是脉冲的二次反射,三次以上的反射因为幅值太小已经无法观察到。

Fig9.VO端输出波形

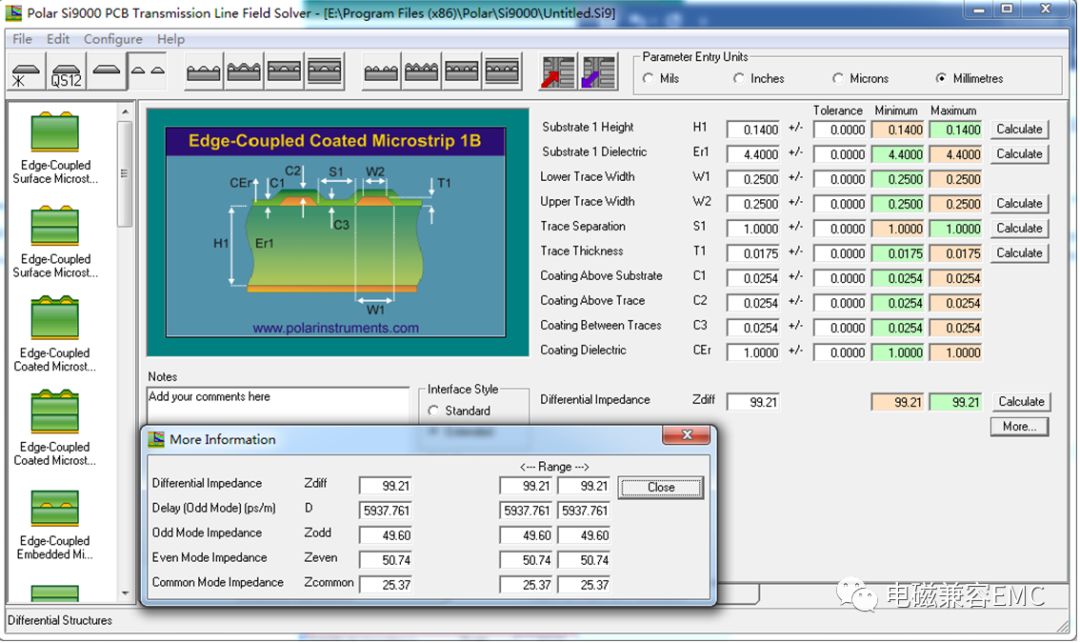

2.2 Delay-time

图3的结果中可以看出,信号在该耦合微带线上的传输时延约为297ps,这里用Polar验证一下不同软件算出的传输线时延是否吻合。选择Edge-Coupled Coated Microstrip 1B计算模型,如图4所示,可以看出Delay-time结果为5.938ps/mm,乘上微带线长度50mm,总的时延为5.938*50=296.9ps,与图3的结果完全吻合。

Fig10.同样参数下Polar计算出的阻抗和时延结果

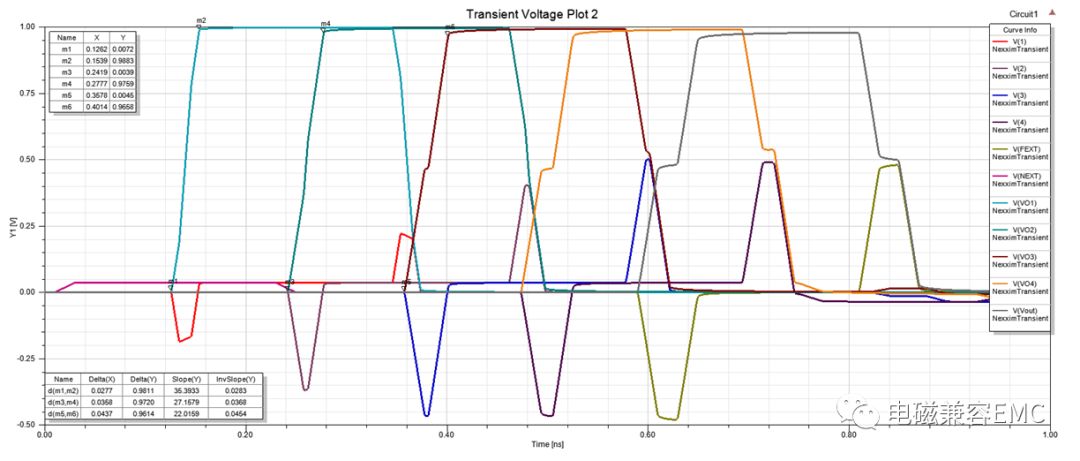

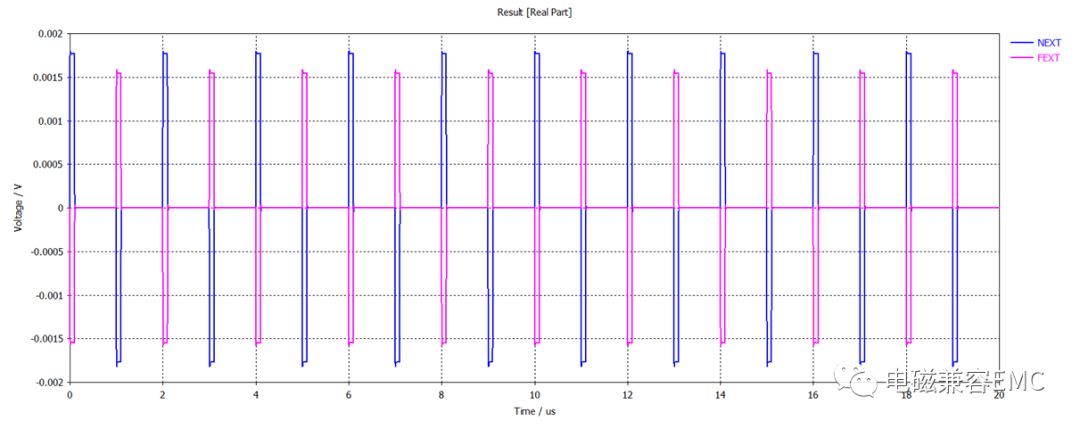

2.3 近端串扰NEXT和远端串扰FEXT

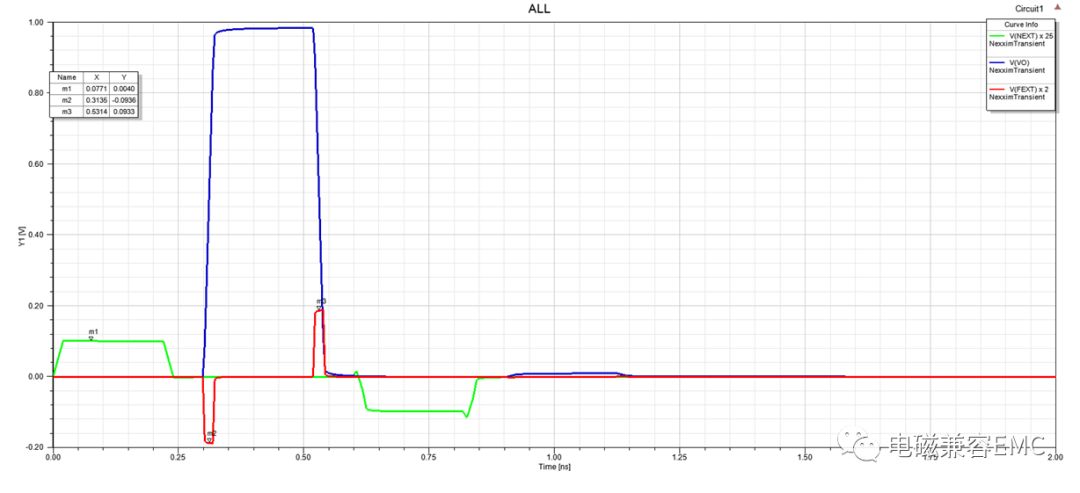

从图2中可以看出,Victim line与Driver line同样进行了阻抗匹配。图5中可以看出近端和远端接收到的波形情况,由于幅值较小,这里分别对NEXT曲线乘25倍,对FEXT乘2倍处理,以便观察。结果中可以看出,近端串扰幅值为4mV,远端串扰幅值为93mV。

观察NEXT波形,可以看出波形从0s开始上升,这是由于Victim line近端可以第一时间接受到来自Driver line的噪声信号,在这段时间内,波形还未到达传输线末端,认为FEXT端开路,NEXT端为短路,ICM+ILM为正,所以其电压幅值为正。而当过了594ps后,NEXT端迎来了FEXT端传过来的二次反射,这时从FEXT端看进去的情况刚好相反,所以电压波形为负。

观察FEXT波形,可以看出波形从297ps时开始下降,这时Driver line电压波形刚好开始上升,此时传输线末端为短路,近端是开路,ICM-ILM为负,所以接收到的电压波形为负值,当时间在320ps~520ps时,由于不存在dV/dt,所以没有感应电压产生。当Driver line电压波形下降时,FEXT端接收到相反的dV/dt,所以电压波形为正。

Fig11.NEXT和FEXT与VO的电压波形

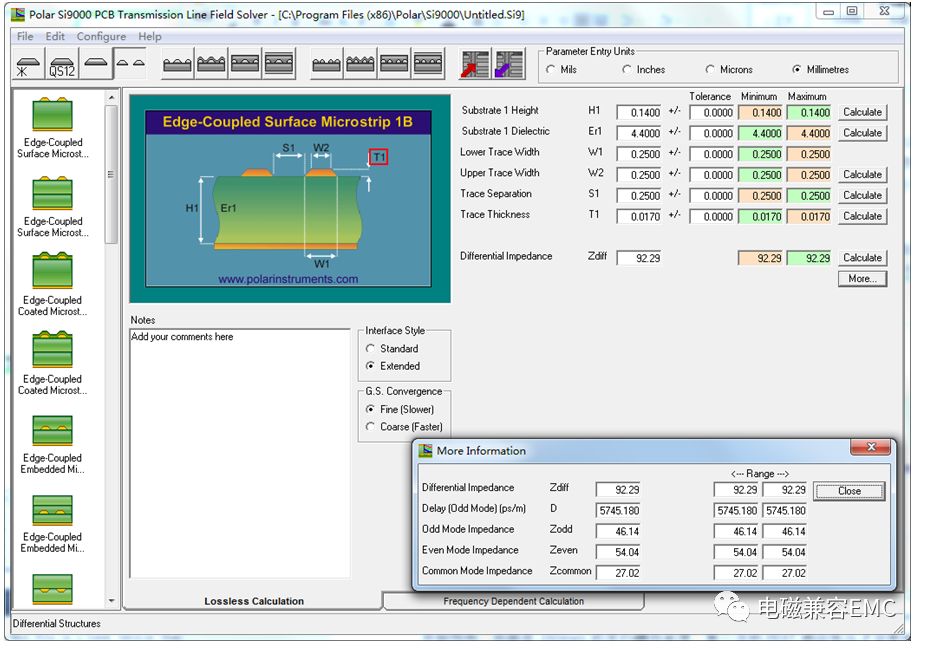

3、耦合长度对串扰的影响(多重crosstalk)

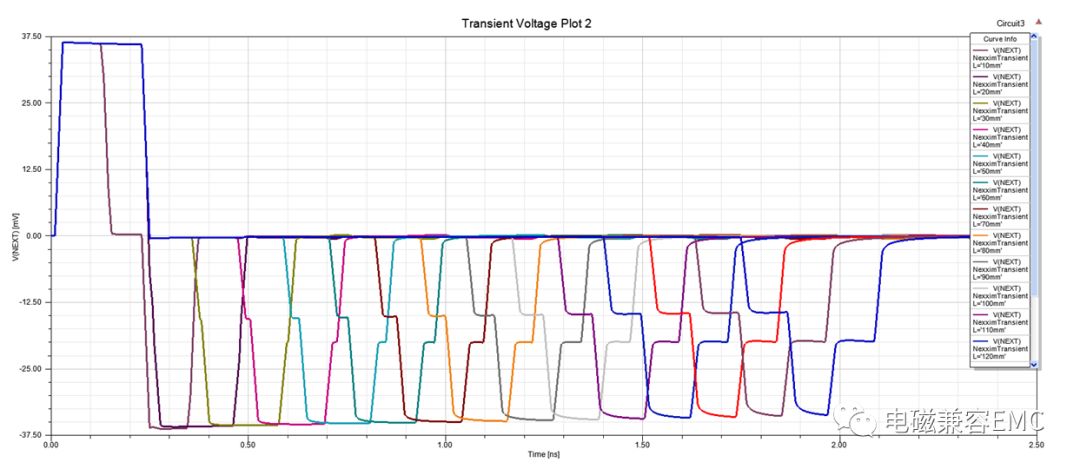

沿用第二节中微带线的参数,其中线间距SP设置为0.25mm,微带线长度设为L,sweepL 10mm~150mm per 10mm,查看三个电压波形。

3.1、疑问?

通常我们认为远端串扰宽度与pluse的上升沿和下降沿时间相等,均为Tr不变(20ps),而且随着耦合长度增加,远端串扰的幅值也应该随之增加。但下图中可以看出,随着平行走线超过50mm,FEXT的大小却呈现饱和(476.7mV),并且pluse宽度增加(>20ps),这是为何?

Fig12FEXT端电压波形

3.2、原因分析

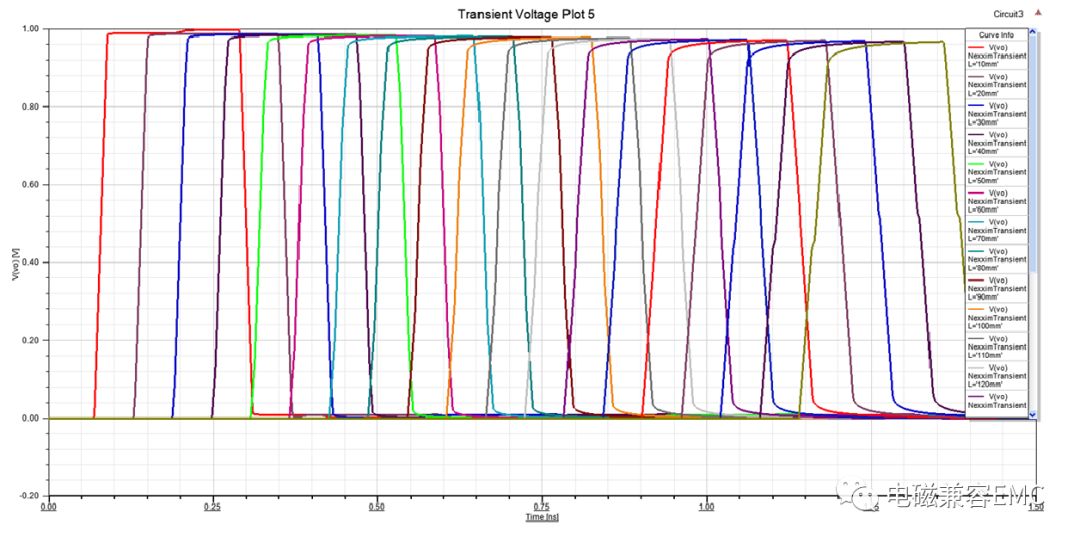

为了找出FEXT随着耦合线增加,其感应pulse的高度却在某长度不再增加的原因,我们观察一下Vo随着耦合线长增加的波形变化,如下图所示,physical length 50mm以上(含)时,Vo的rising/falling在一半高度开始有变化。

Fig13Vo端电压波形

假设:activeline上的pulse Vi对quiet line感应的FEXT电压又返回来对原active line上正在传递的该pulse信号产生影响,即第一次的FEXT对active line产生二次耦合(FEXT)。那这个问题不管怎么调active line或quiet line上的终端电阻都没有用,唯有拉开space或将stack-up变薄以降低crosstalkeffect才有效。

那么,实际上是否如假设说的一样呢?下图采用传输线模型描述了微带线间的耦合原理,我们用特征阻抗Z来代替复杂的分布电容和分布电感参数,可以看出active line与quiet line组成的微带线系统,其共模阻抗为50,差模阻抗约为100。在微带线长度为无限长时,认为其为完全耦合,此时,电路模型采用集总参数描述,分配到quiet line末端电压的幅值恰好为active line的1/2,这也就解释了为何FEXT端饱和电压幅值约为Vo的1/2。

Fig14采用传输线理论描述的耦合微带线模型

因为耦合微带线采用的是传输线模型计算,不能单纯的以集总参数描述它们之间的行为。下面建立多节传输线模型,研究信号在传输中的变化过程。微带线截面参数与上面保持一致,单节模型长度为20mm,总长度100mm。

Fig15传输线上信号变化过程

下图为每节active line输出波形与quiet line感应波形,从中可以发现,输出波形随着出,随着长度增加,波形上升沿和下降沿时间加长,横电平时间几乎不变。按照理想传输线中信号传输速度来看(下式),速度仅与介质有关,与频率无关。所以这种变化是不该出现的。

实际有耗传输线中会产生色散,因此上升沿与下降沿中对应的高频成分,会随着传输距离的增加,产生比低频成分更多的衰减。所以,随着传输距离的增加,上升沿和下降沿会趋于平缓。因为这里采用单个矩形波脉冲信号,当信号为连续脉冲时,退化的边沿会与后续的波形叠加,此时,信号的宽度不变,叠加会导致更严重的震荡产生,导致信号波形恶化。

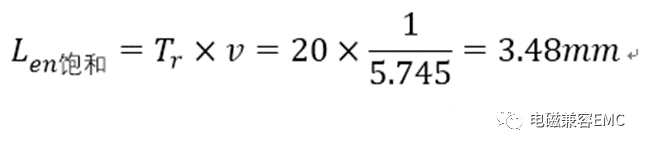

Fig16单节传输线上的波形分布

仔细观察图16,可以看到NEXT端波形为正,而V1波形为负,V1是否存在一个临界值?答案是否定的,当信号开始进入active line,quiet line上便会第一时间感应出负电压,随着距离增加,负电压持续时间增加。当信号传递到传输线饱和长度时,负电压持续时间开始与信号上升沿时间相等。下面我们验证该结论,采用SI9000计算信号时延为5.745ps/mm,时延与传输速度呈倒数关系。所以传输线的饱和长度为:

Fig17耦合微带线模型的时延

当把第一节传输线模型长度调整为3.48mm时,V1端电压波形在负电平时间恰好为20ps,第一章中指出,饱和长度的定义为近端串扰电流达到稳定值对应的长度,这里延伸到远端,也指远端电压持续时间达到与上升沿时间相等,且不再增加的长度。

Fig18饱和长度位置下的耦合电压波形

3.3、二次反射的情况

查看3.1节中NEXT端波形情况,可以看出只有当传输线长度为10mm时,电压波形宽度是小于20mm以上情况的。由3.2节可知,传输线时延为5.745ps/mm,当长度为10mm时,耦合波形时间长度为57.45ps。而结果中m1~m2对应的时间为117ps,这是为什么呢?

随着传输线长度的增加,二次反射回来的波形出现了明显的塌陷,这种情况产生的原因与3.2节中FEXT情况是一样的。

Fig19NEXT端电压波形随长度变化情况

Fig20NEXT端电压波形和active line输入波形

3.4、active line和quiet line参数调节

在3.1的基础上,同样的仿真参数再跑一次,但把active line与quiet line的距离由0.25mm修改为0.75mm,我们发现NEXT、FEXT都变小,且当physical length增加到160mm时,FEXT才开始饱和,也就是160mm的平行耦合长度,第一次的FEXT感应电压才会影响原active line上正在传递的pulse信号。

Fig21拉开距离后的输出电压波形

4、间距变化对串扰的影响(3W原则由来)

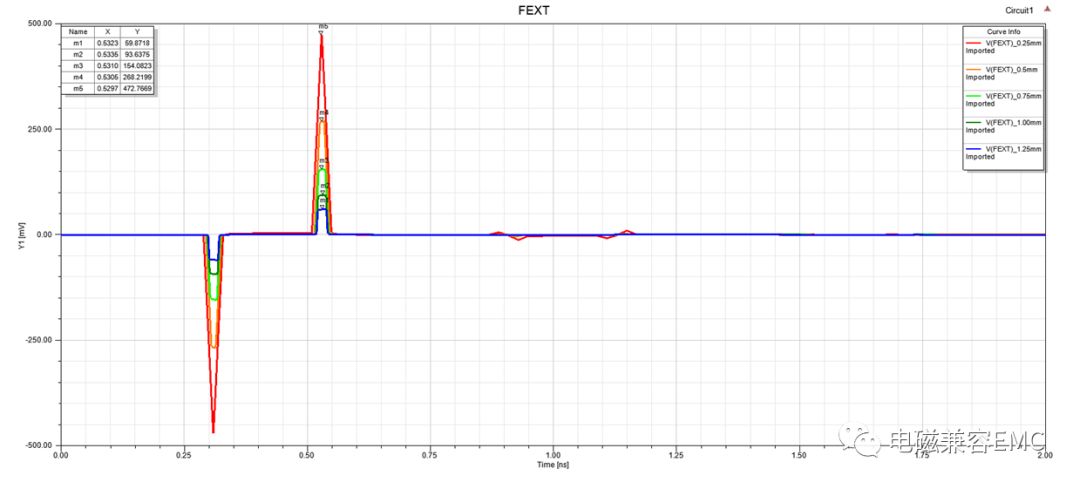

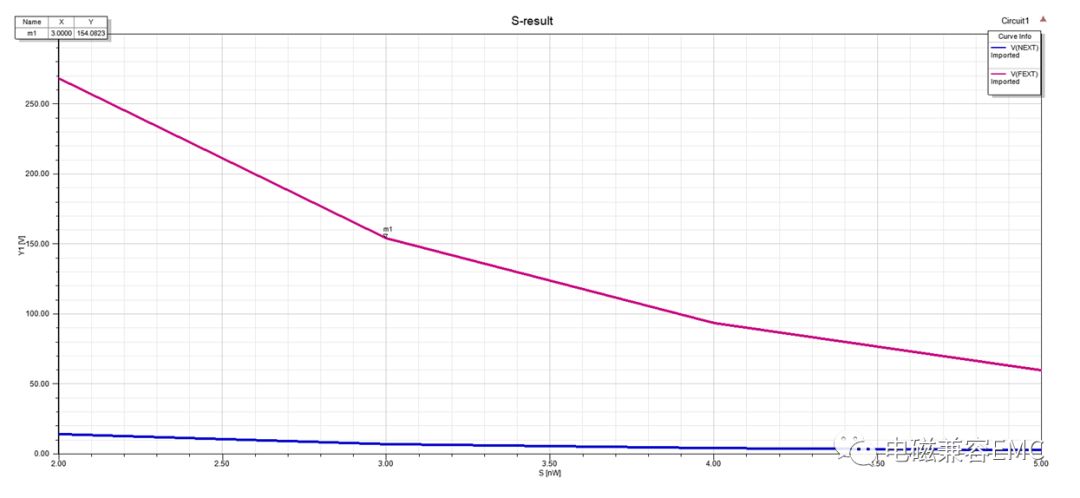

在第二节中,仿真模型默认间距S为1mm,线宽W为0.25mm,这里我们调节线间距S,以0.25mm为倍数,S的值从1W增加到5W,查看受扰线上NEXT和FEXT串扰幅值的变化规律。从图6和图7和图8中可以看出,随着间距增加,NEXT和FEXT端串扰电压幅值先是快速下降,随着S继续增加,下降趋势放缓。

Fig22.NEXT端串扰幅值随S变化情况

Fig23.FEXT端串扰幅值随S变化情况

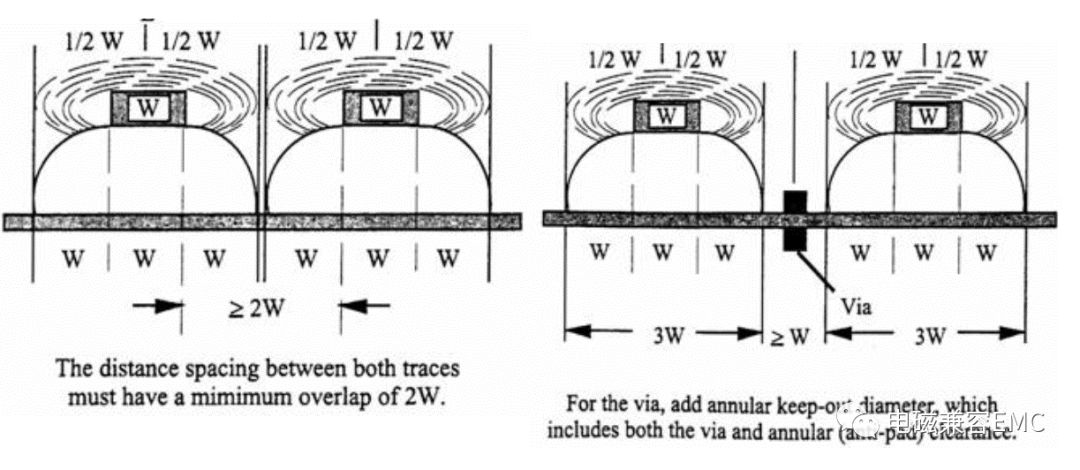

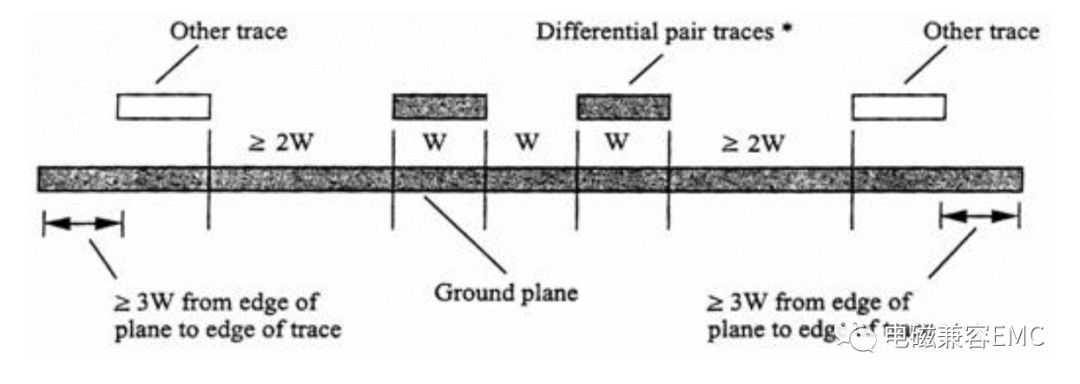

我们所熟知的crosstalk 3W rule一般是指:在特性阻抗50Ω下的传输线,保持3W的间距是安全的。对于特性阻抗高于50Ω的情况,3W的间距往往是不够的。

Fig24.Victim line随S增加,两端接收到的crosstalk电压走势

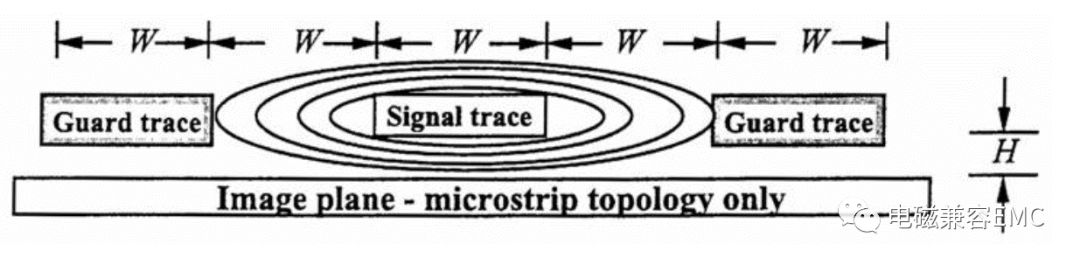

下面是Montrose 在《Printed Circuit Board Design Techniquesfor EMC Compliance》一书中对3W原则的描写

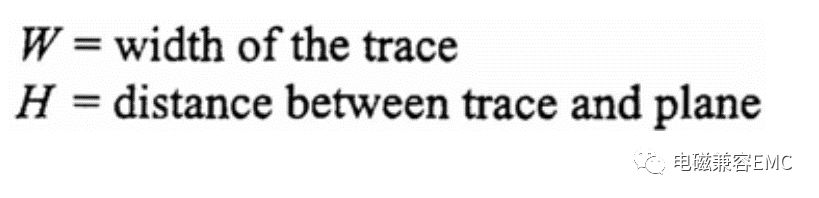

5、防护地线对串扰的影响(Guard Trace Effect)

从PCB设计的角度讲,敏感信号线间除了需要保持一定的距离,往往在设计时会考虑加入防护地线,进一步保护走线不被影响。防护线的作用主要是引入低阻抗边界,将信号线上发射出来的电力线引入到地回路。下面用ANSYS对防护线进行仿真,查看其对串扰的影响。

Fig25.With/withoutguard trace

5.1固定线宽下,防护地线的影响

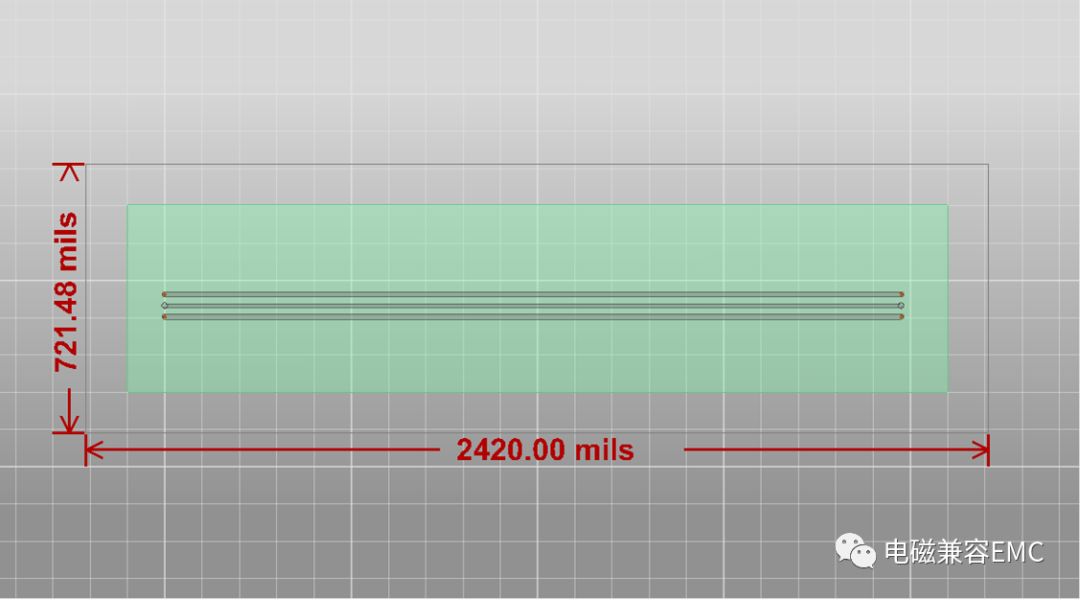

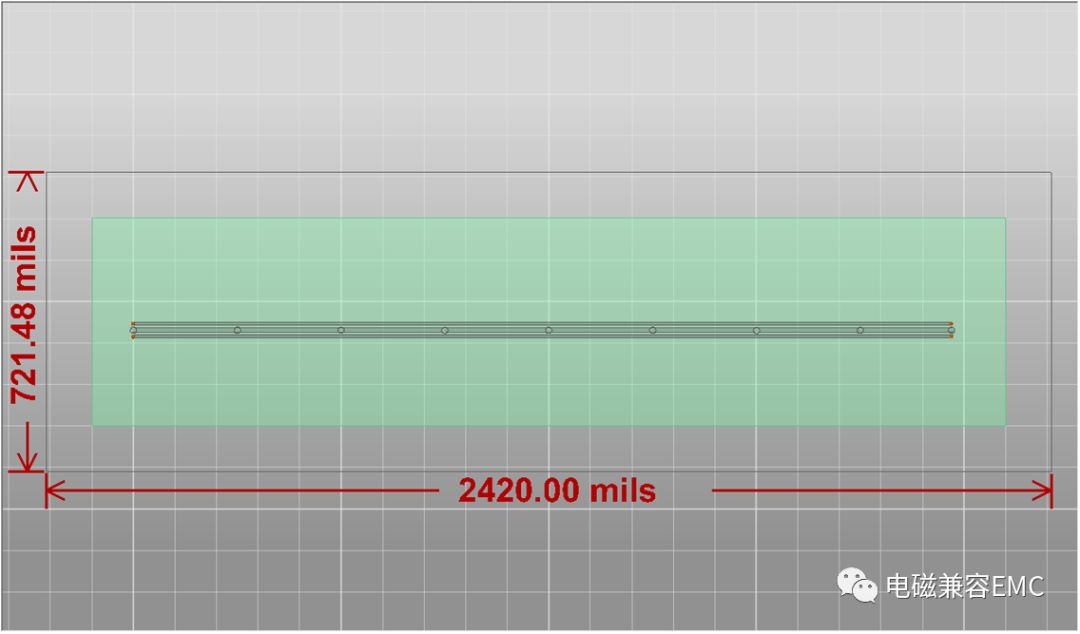

下图走线线宽7mils、线距7mils(走线边缘到边缘)、过孔直径5mils、ground guard trace线宽10mils、线长50mm,板厚1.6mm;分别是走线不伴随地线、两条走线伴随一条地线、四条走线伴随一条地线。

5.1.1 两条线穿插一条地线

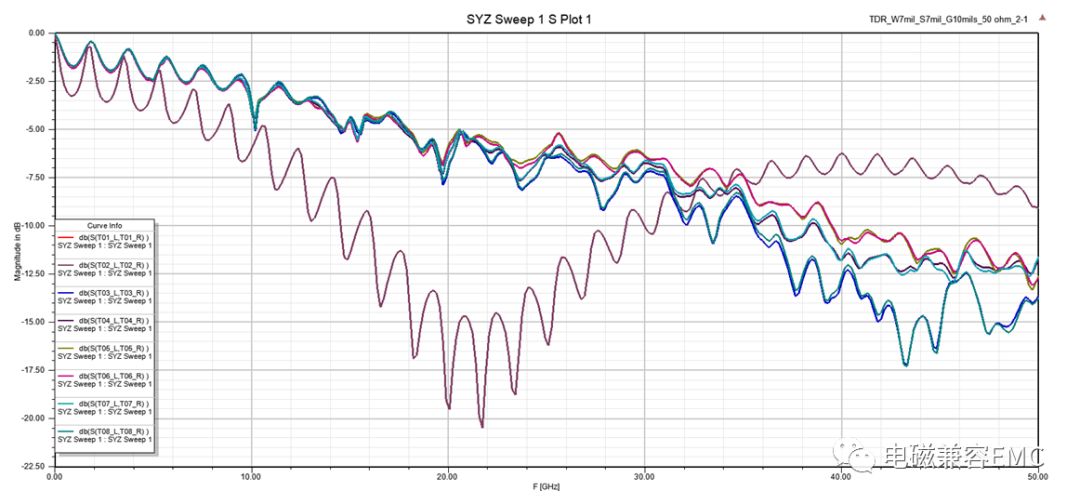

图26中所示模型,走线编号从上到下分别为T01~T09,每条trace的左侧为L端口,右侧为R端口,图27为每条trace的S21参数。

Fig26.两条线穿插一条地线

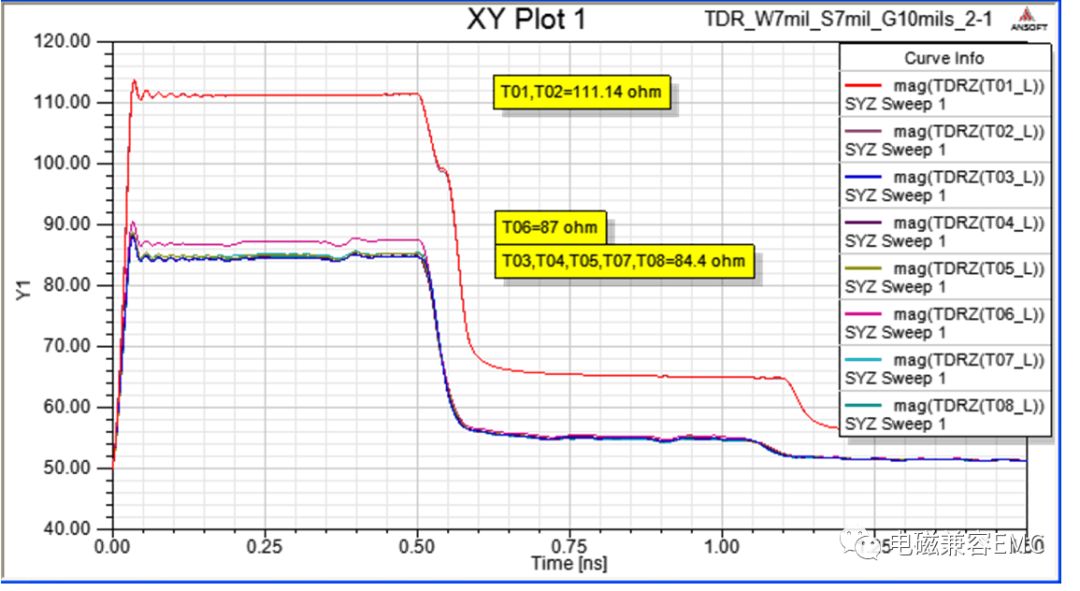

Fig28.TDR results

T03~T08是一样的结构,S21应该都差不多,从此例的模拟结果来看,SIwave的精度大概到25GHz,而Ansoft当时给出的官方说法是SIwave适用于DC~50GHz。

5.1.2四条线穿插一条地线

Fig29.四条线穿插一条地线

Fig30.S-parameters for S21

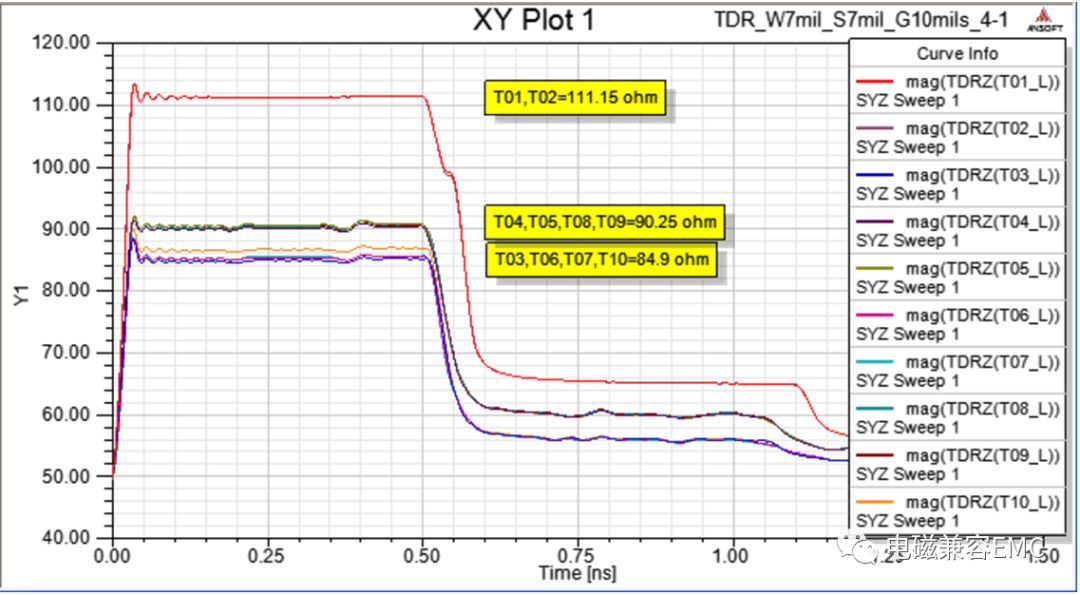

Fig31.TDR results

只要有伴随地线,不管是两条线穿插一条地线,或是四条线穿插一条地线,S21在20GHz以内表现都差不多(1dB)。但如果没有伴随地线,在1GHz就可以看出差异,S参数特性差很多。

没有伴随地线的信号,特征阻抗明显大很多(T01,T02=111Ω),而只要有伴随地线,不管是两条线穿插一条地线,或是四条线穿插一条地线,特征阻抗会在84~90Ω之间。这里的地线为10mil,并不是很宽,via间距为17mm。

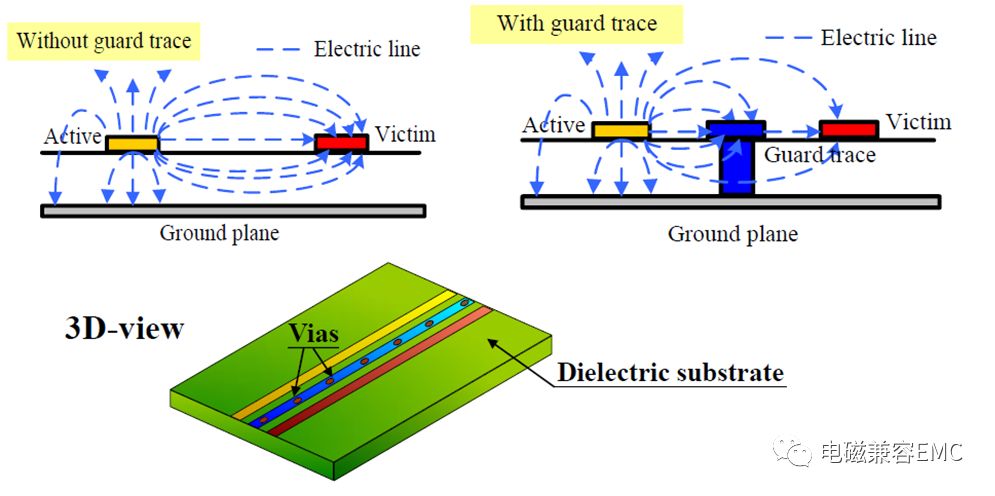

5.2 防护地线线宽的影响

如下图所示,建立特征阻抗为50Ω的微带线模型,线宽为14mil,介质厚度8mil,介电常数4.4,走线长度为1975mil,两根信号线间有一根可变宽度的伴随地线,地线通过两端接地。查看随地线宽度的变化,受扰线上噪声波形的变化情况。伴随地线初始宽度为5mil,每次增加宽度为2mil。

Fig32.两根走线间的伴随地线

6、防护过孔对串扰的影响

PCB中过孔的设计是多数人容易忽略的环节,过孔的设计直接影响到诸多参数,对于电源平面过孔,会直接影响到电源网络的压降,分布参数,改变电源网络谐振特性;对于信号部分,过孔的引入会对信号的完整性造成影响;当用作板上各层GND间的连接时,过孔直接影响GND平面噪声电流的分布,关系到信号回路面积的大小。

盧俊郎等在《The Via'sEffects on PCB Traces》一文中对于过孔效应的分析中提到以下几点:

对于同一过孔而言,数学过孔模型比实际过孔测量的电容效应大,且过孔的电容效应与电感效应相比,以电容效应为主。

走线上第一个过孔对阻抗不连续的影响最大,随着过孔数的增加,过孔电容效应增加不明显。这是因为过孔与传输线会带来高频信号损耗,所以分析仪器所测量到的效应也递减。

厚度越薄的PCB,过孔电容效应越小(电感效应也会越小)。

过孔的电容效应,对微带线与带状线的影响差别不大。

线宽大于或等于过孔直径时,过孔所形成的阻抗不连续性几乎消失,此时的过孔效应很小。

以过孔换层走不同层时,若是能参考同一地平面,过孔的电容效应较小(电感效应也会越小),换层所引起的阻抗不连续性较轻。

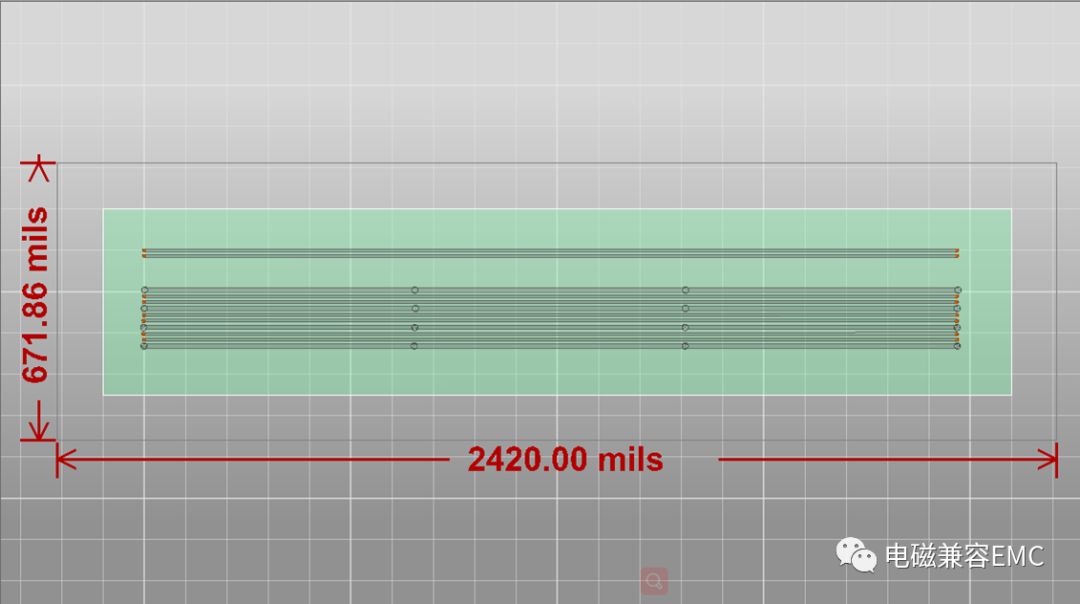

李丽平等在《防护线减小微带线间串扰的FDTD分析》一文中提出,只要:(1)添加有接地过孔的防护线并使过孔间距小于信号在Tr/2(Tr:传输信号的上升时间)时段内的传输距离;(2)在满足线间距布线规则的前提下,将防护线适当加宽而又维持三条线(防护线和两条微带线)中两两之间的中心距不变,就能有效减小线间的远端和近端串扰。

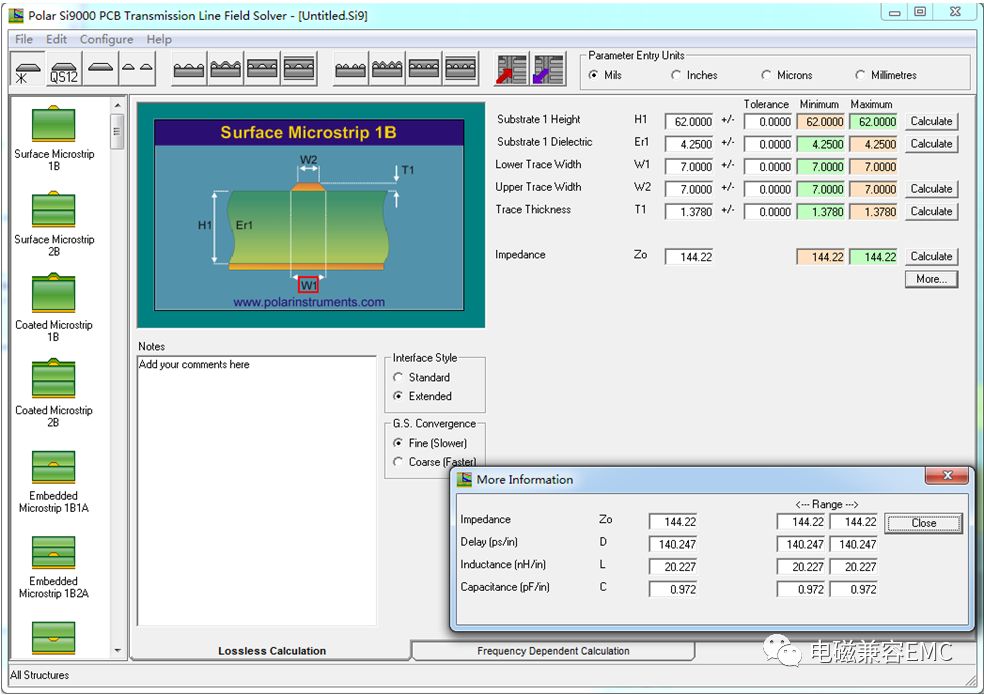

按照5.2节模型,在中间防护GND走线上每隔250mil放置一个GND过孔,如下图所示。

Fig33.带有GND孔的防护地线

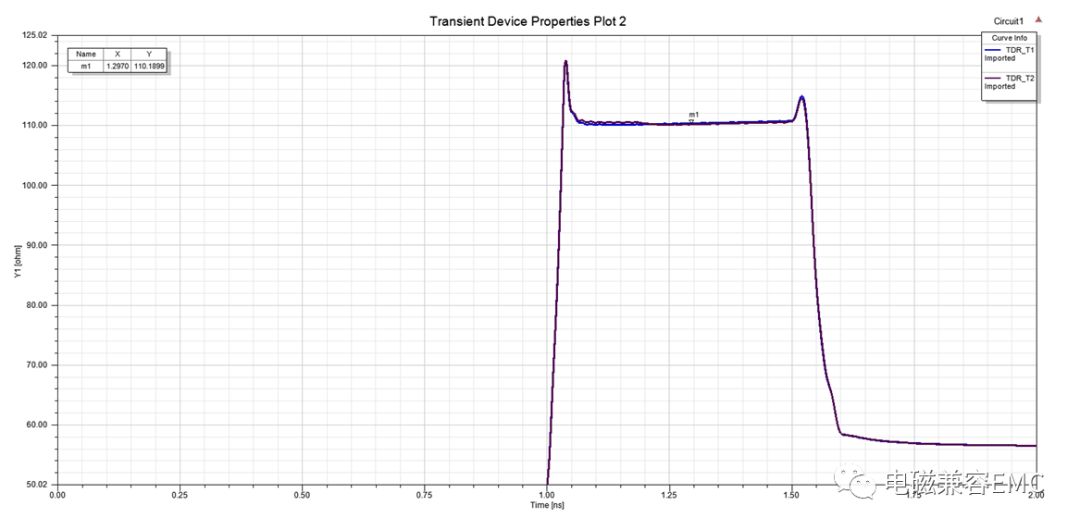

采用SI9000计算得到单线阻抗为144.22Ω,因为伴随GND的缘故,实际用siwave计算得到TDR阻抗为110.19Ω。该走线时延为140.247ps/in。为满足孔间距小于Tr/2,RT须大于70ps。

Fig34.走线特征阻抗与时延

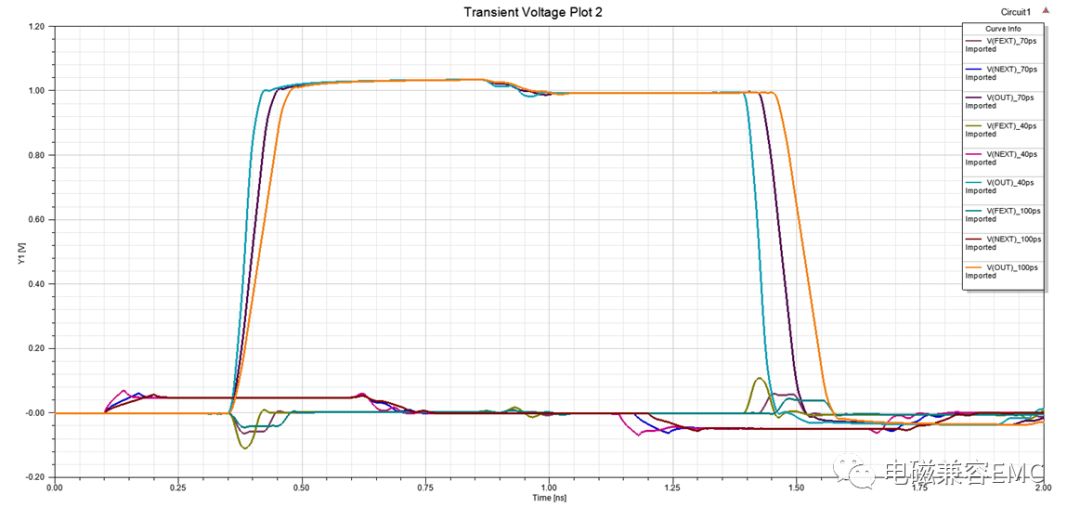

我们将RT时间分别设置为40ps、70ps、100ps,查看victim line上串扰电压幅值的变化,如下图所示。可以看出,上升沿时间的变化,对于近端串扰电平的影响不大,主要影响远端串扰电平。Tr/2大于孔间距的定义是处于对远端串扰防护的设计要求。当Tr时间不变,改变过孔间距的情况会得出相同的结论,感兴趣的读者可以自己去计算一下。

Fig35.不同Tr下的串扰电压波形

注意:高速信号过孔间也会存在串扰,对于板厚较厚的PCB来说,以3mm单板为例,一个通孔在PCB板厚方向上的长度可以达到将近118mil。如果PCB上扇出过孔间距较小,如BGA封装的IC,其扇出过孔间距只有几十mil。这时,过孔间垂直方向并行距离大于水平方向间距,就需要考虑高速信号过空间串扰问题。高速PCB设计时应该尽可能最小化过孔根长度,以减小对信号的影响。对此感兴趣的读者可以去TI论坛中查看《高速差分过孔之间的串扰分析》一文。

7、Minimizationof Crosstalk

7.1吴瑞北的设计方法

在Crosstalk_App一文中列举了降低串扰的集中设计方法,分别如下

• 在布线允许的前提下,尽可能增加S,降低H;

• 关键的信号线,如系统时钟,采用差分布线;

• 在有显著耦合的层间使用正交布线;

• 如果条件允许,尽可能采用带状线而不是微带线;

• 信号线间并行长度控制在最小;

• 在PCB板上减小元件间走线的拥挤;

• Use slower edge rates with caution.

• Use genius layout design, say Tx-line interpose.

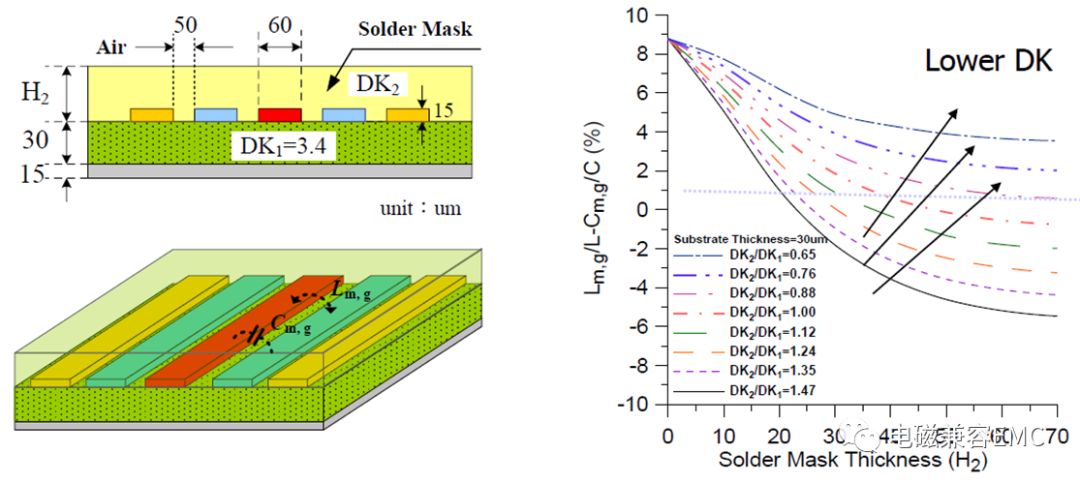

7.2 Y.-S. Cheng, W.-D. Guo等的观点

他们在“Enhancedmicrostrip guard trace for ringing noise suppression using a dielectricsuperstrate”一文中提出,通过调整阻焊层厚度和介电常数,可以达到抑制串扰的效果。参考图6中远端串扰幅值的公式,可以发现,当阻焊层介电常数与厚度为某一特定值时,远端串扰将会消失。

Fig36.Novel Guard Trace Design

8、ANSYS串扰检查模块

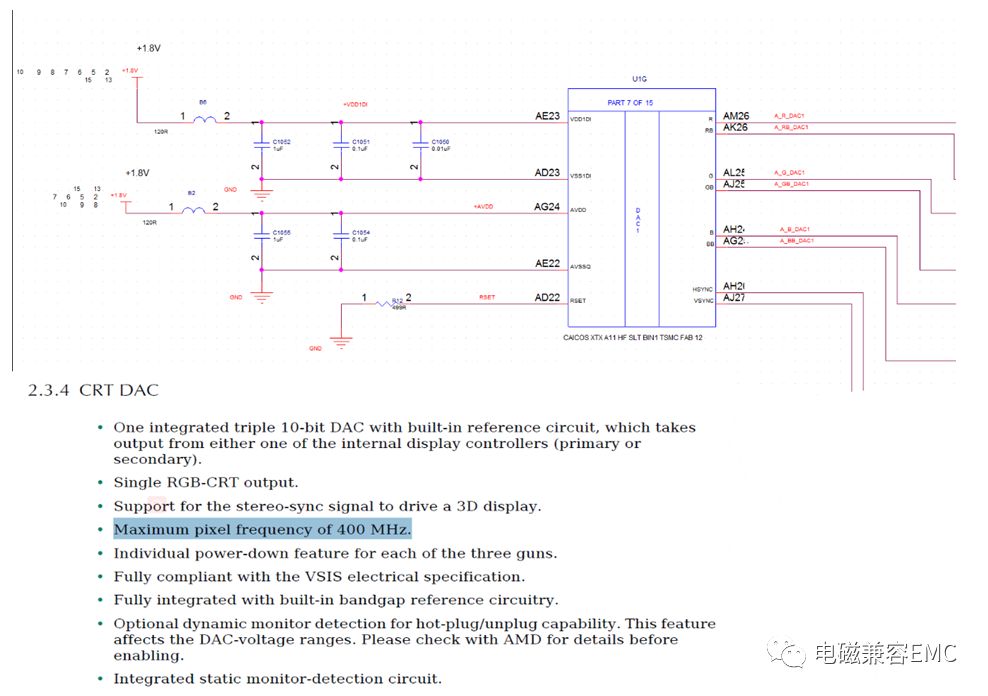

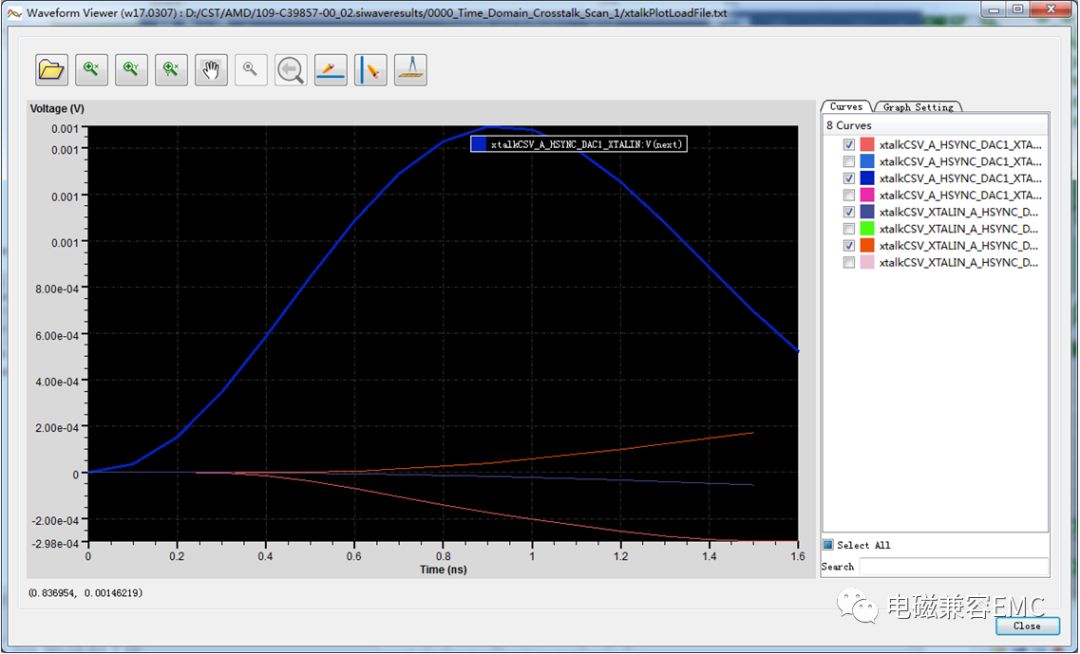

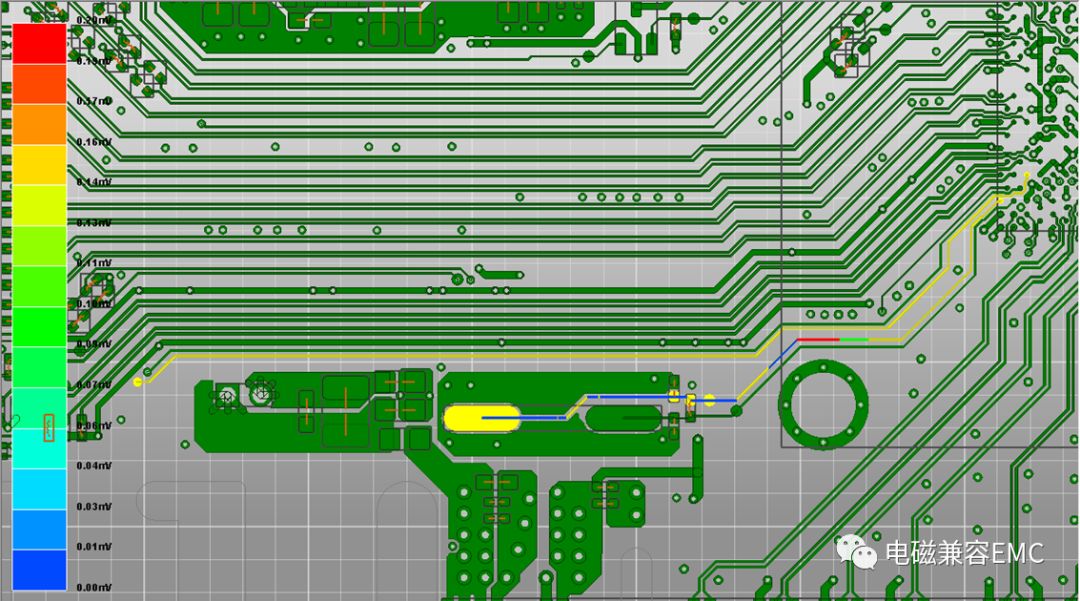

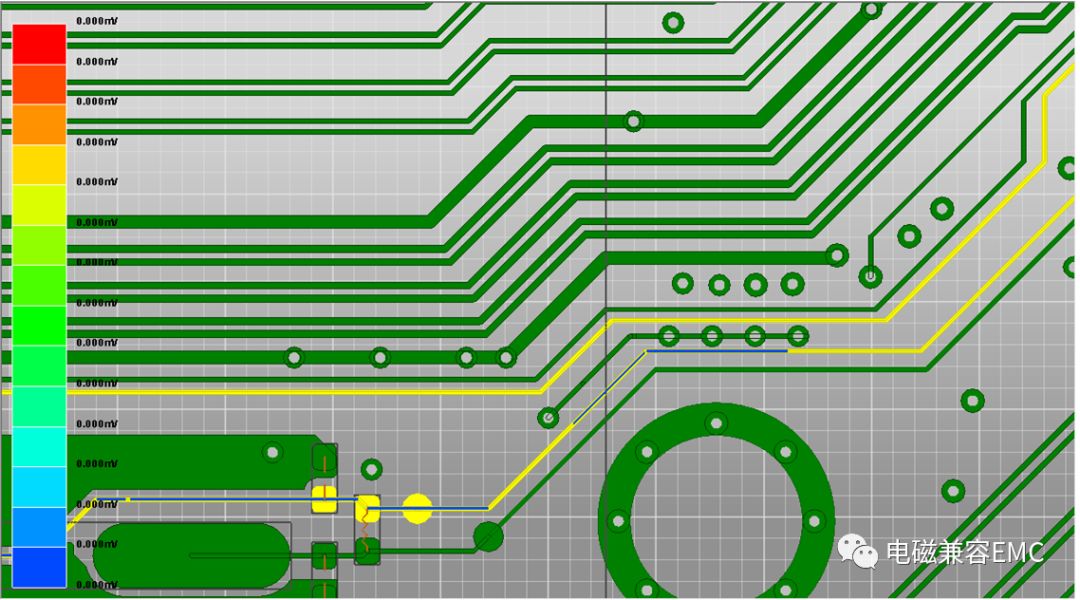

ANSYS SIwave中提供了CrosstalkScan串扰分析模块,分别有时域和频域选项,可对单线/差分线进行串扰的快速分析,图33中以某PCB为例,图中箭头位置为U1的晶振X2,时钟走线XTALIN与信号线A_HSYNC_DAC1有一段较长距离的平行走线,需要评估时钟走线对信号线的影响。

Fig37.SIwave仿真某PCB示例

8.1 参数设置

查看芯片手册和原理图,可以得知A_HSYNC_DAC1信号为RGB输出信号,电平为1.8V,速率为400MHz,XTALIN信号电平同样为1.8V,速率为27MHz。查规格书中DAC信号上升时间为0.58ns~1.7ns取1ns,DAC信号为查分形式,差分阻抗为75R,对地阻抗为37.5R。XTALIN信号上升时间在15pF负载下为4ns,这里为12pF,将其设置为3ns。

Fig38.信号参数

进行仿真前,将精度调制合适水平,crosstalk收敛精度调整为-60db,求解频率调高到20GHz,然后选择Time domain时域仿真,将信号对应的参数填入两根走线的信号定义中,选择launch开始仿真。

Fig39.参数设置

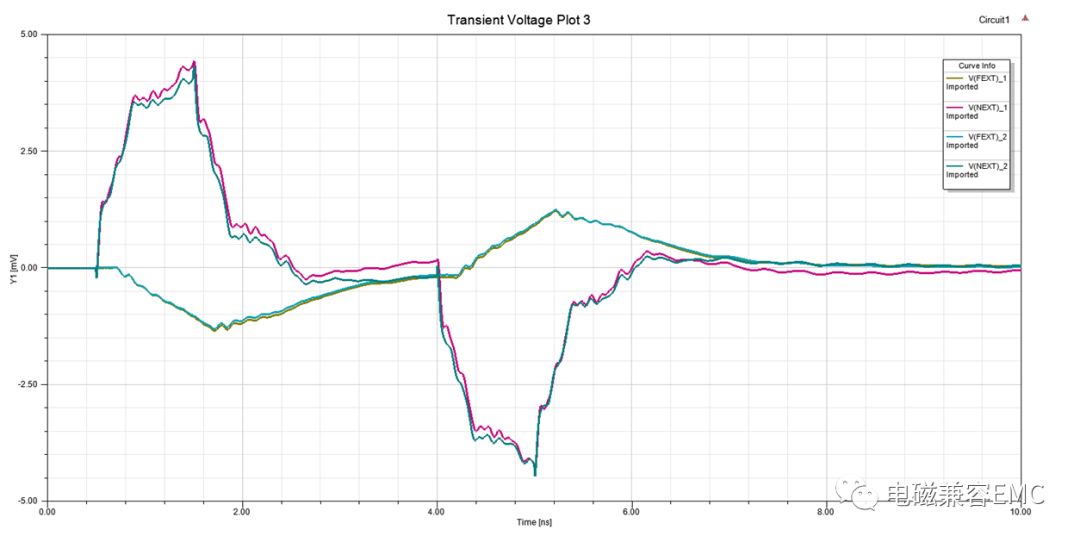

不到半分钟后仿真结束,查看FEXTt和NEXT端各自耦合到的电压波形,如下图所示,从结果可知,A_HSYNC_DAC1在XTALIN线上产生的NEXT耦合噪声最高,约为0.001V。一般信号走线中串扰电平的安全阈值约为信号电平的5%,因此这两根走线在布线上认为是OK的。

Fig40.crosstalkresult

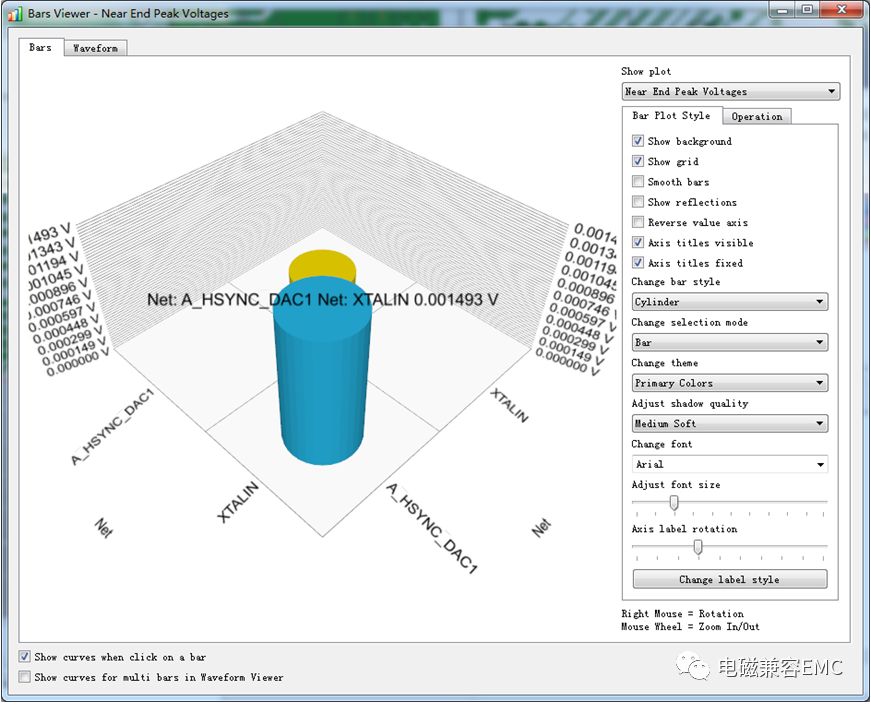

结果中不仅提供了信号线上耦合的波形,而且有峰值柱形图及FEXT/NEXT时域耦合峰值位置,从耦合结构图中可以直观的看到走线中耦合较严重的部位。从下图中可以看出,平行走线中局部耦合较为严重,当结果超过安全阈值时,就需要对其进行处理。

Fig41.Peak Voltage and Time Domain Crosstalk Max Voltages results

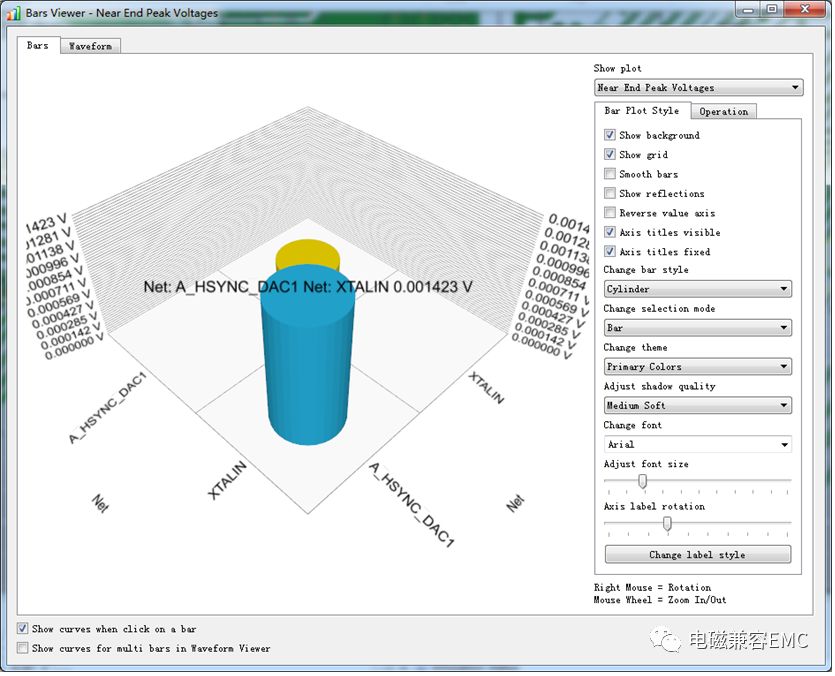

因为走线整体布局已经确定,这里选择在线间加部分伴随GND走线,当优化后再次进行仿真后,可以看出,原先位置的电平已经降下来了。

Fig42.Peak Voltage and Time Domain Crosstalk Max Voltages results

8.2 优化

采用S参数模型仿真时域串扰,因为Time Domain Crosstalk功能并非基于精确的S参数求解,所以为了清晰的认识优化前后的对比,这里用S参数模型,在circuit design内创建串扰电路模型。优化前后的串扰波形如下图所示(_2为初始,_1为优化后)。可以看出,优化后正向电压增加,负向电压减小,整体平缓,但是优化后并未有较为明显的变化,是否可以认为防护线没有作用呢?

Fig43.Results of crosstalk

注意:这里对比不明显的原因在于,第六章中提到防护地孔与信号上升沿之间的关系,实际电路中信号Tr是不变的,多数情况下也不允许添加电容增加Tr时间,对于这种情况,只能尽可能保证线间距大于3W。

9、线缆间的串扰

线缆的设计在EMC设计中,常常会忽略线缆间的串扰。然而实际情况是,有相当一部分产品的设计缺陷来自于线缆间的串扰,这类问题多来自军品、医疗、汽车等标准规范要求严格,结构复杂,存在诸多互连线缆的产品上。

相邻导线间的串扰既可以是由互电容产生的电场耦合引起的,也可以是由互电感产生的磁场耦合引起的,第三种形式的耦合是通过共阻抗引起的。

当遇到线缆接口数据传输错误的情况,未必一定是串扰造成的,还有一种可能是由于线路与负载阻抗不匹配而产生的反射,后者往往会被误认为是串扰。(关于反射下文会详细的进行总结)

那么,当EMI问题出现,该如何确定是否为串扰引起的呢?一种实用方法是把干扰源和敏感导线分开。若这种方法不易实施,那么将干扰源信号上升沿降低或将频率降低,则可能是另一种可行的方法。在产生间歇性EMI并怀疑是串扰引起的情况下,可以用增加干扰源信号的幅度、频率、速率或通过变压器或电容器注入另外的噪声源的方法来加以证实。此时,若EMI趋势是增加的,则可能已经发现有串扰源存在。

当串扰已经发生在PCB线路间,相邻导线时,首先需要确定耦合主要是电场耦合(容性),还是磁场耦合(感性),因为不同的耦合方式决定了不同的处理手段。大卫.A.韦斯顿在《电磁兼容原理与应用》中提出一种简单有效的方法。作者将干扰源和敏感电路之间的特性阻抗和敏感电路与地线之间的阻抗用在串扰预估中,该准则如下:

当干扰源和敏感电路阻抗乘积小于300²Ω,则主要是磁场耦合;

当阻抗乘积大于1000²Ω时,则主要是电场耦合;

当阻抗乘积在300²Ω和1000²Ω之间,则磁场或电场耦合能否起主要作用,要取决于电路的几何尺寸和频率。

看到这里,细心的读者不难发现,磁场耦合或是电场耦合分别发生在特定电路中。产品中电源部分往往是低阻的(磁场耦合),信号往往是高阻的(电场耦合),而电源与信号之间的耦合介于两者之间。

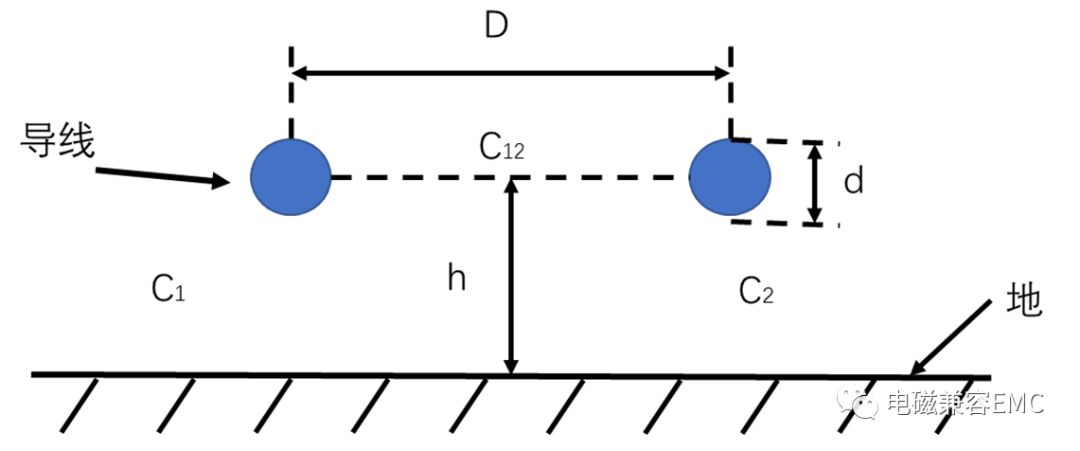

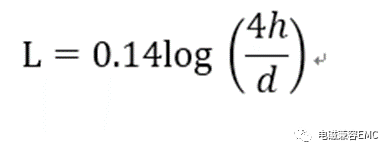

对于直径为d,距离接地面高度为h的单线,如下图所示:

Fig44.Cable model

其导线电感L(Uh/ft)为:

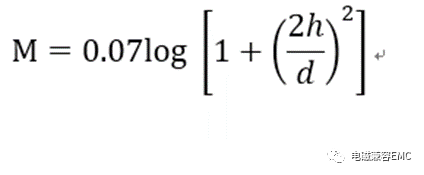

两根导线之间的互电感M(Uh/ft)为:

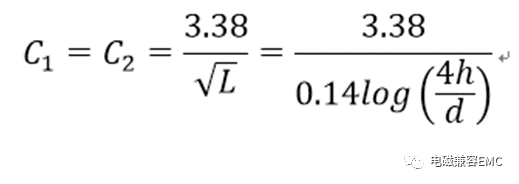

线对地电容为:

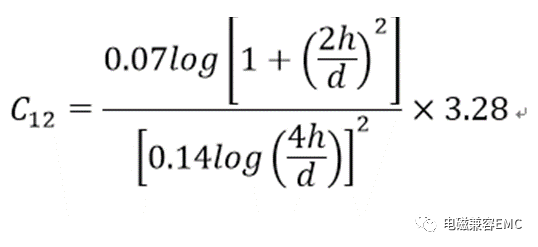

线对线电容(互电容)为:

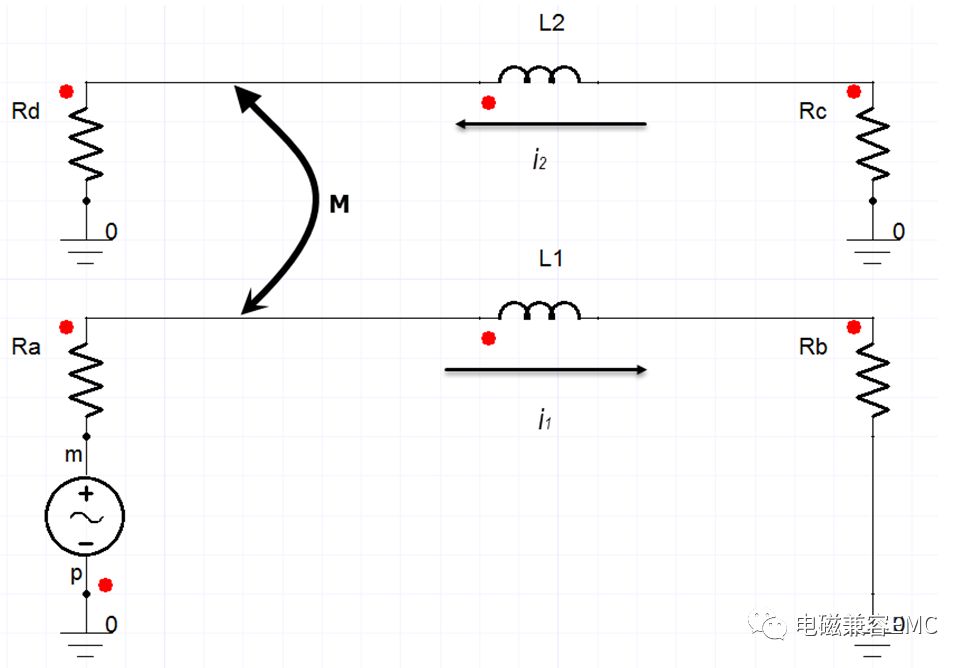

平行双线间串扰模型如下图所示:

Fig45. Cable 耦合模型

受干扰负载Rd两端的电压幅度可由以下公式计算得出:

式中可以看出,当线束与地面距离h下降时,导线电感L和线间的互感M同时下降,当h降低到之前的1/10时,自感L降低0.14(uH/ft)(按照最大距离h为50mm,d为2mm计算,一般情况下产品内部线束的自感约为0.2(uH/ft)左右),互感降低的趋势随h与间距D的比值变化而不同。从Vd的计算公式中可以看出,当受扰线为高阻,或者骚扰线为低阻时,串扰增加。下面采用CST cable studio工具将这种变化描述给读者。

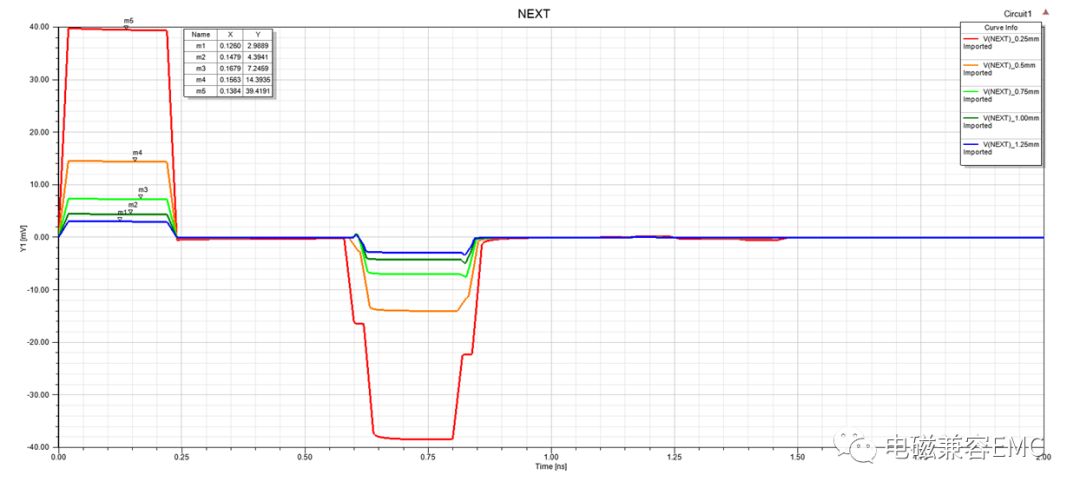

9.1、单线间的串扰

9.1.1建立线缆模型

选择0.2mm线径的单线,长度为100mm,线间距5mm,线与GND间距5mm,driver line的信号Tr为0.1ns,Tf为0.1ns,周期2ns,50%占空比,幅值1V。

Fig46.耦合线模型

查看victim line上近端和远端波形,如下图所示,受扰线上电压幅值约为施扰线电平的2%。即使施扰线信号电平增加到3.3V或者5V(多数信号电平),受扰线上噪声电平也是可以接受的。

Fig47.受扰线噪声电压波形(接地阻抗50R)

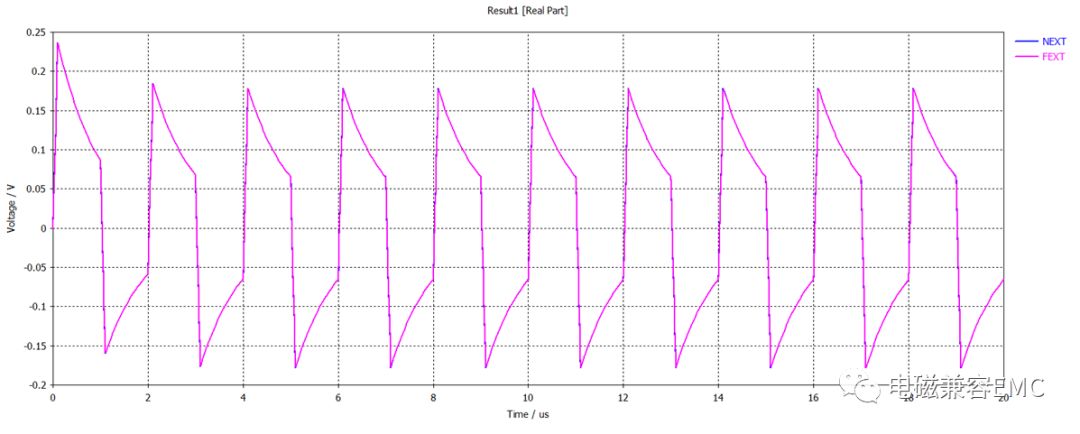

9.1.2线束设计是否一定满足需求?

那么,实际中这样的线束设计是否一定满足需求呢?答案是否定的,因为实际电路中信号线阻抗往往是高阻的,尤其是采样信号线束的阻抗通常在千Ω以上,当受扰线阻抗增加到1MΩ时,线上噪声电平将增加到不能接受的水平。如下图结果中,FEXT,和NEXT电平增加到0.18V,现实产品中往往将线束扎起来(D减小),并且有较长的走线(如EMC测试要求线束长度为2米左右)。这些情况都会增加受扰线上噪声电平,尤其是在做EMS抗扰度测试时,若信号线不做滤波等防护处理,产品是极易被干扰的。对比上下两图,可以看出FEXT与NEXT由开始的反相变为同相,这是为何?这个问题留给读者去思考。

Fig48.受扰线噪声电压波形(接地阻抗1MR)

当信号线整体阻抗变化时,其噪声电平与信号线阻抗间的关系如下图所示。可以看出,将信号线阻抗控制在较小水平,可以有效降低串扰电平幅值。从中也可看出,在信号线上采用电容去偶的效果是最好的,远优于电感(原因在滤波篇中会讲到)。

Fg49.受扰线噪声电平随接地阻抗变化

9.1.3 线缆中的“3W原则”

实际上人们在产品设计中往往只关注PCB中上信号走线,忽略线束设计。线束实际上是PCB的延伸,同样需要在布局上重视。当增加线束间距D,观察串扰幅值的变化,如下图所示,当间距D增加到15mm时(3倍h),噪声电平下降趋于平缓。因此,对于敏感信号,需要严格控制线束的走线,必要时需采用独立走线的方式。

注:改变导线与GND间距h,得出的趋势一致。

Fig50.受扰线噪声电平随线间距变化

9.1.4 GNS距离的影响分析

前面公式中可以看到,降低线束与GND平面的距离,可以降低线束间串扰的幅值。这里采用软件计算出随GND间距h变化,串扰幅值变化的情况。从下图结果中可以看出,随着线束与GND间距增加,串扰幅值增加,在设计允许的间距范围内,整个趋势近似为线性增加。也就是说,当h减小一倍,受扰线上噪声电平幅值便降低3dB。

注:改变导线间距,得出的趋势一致。

Fig51.受扰线噪声电平随GND间距变化

9.2 不同规格线束间的串扰

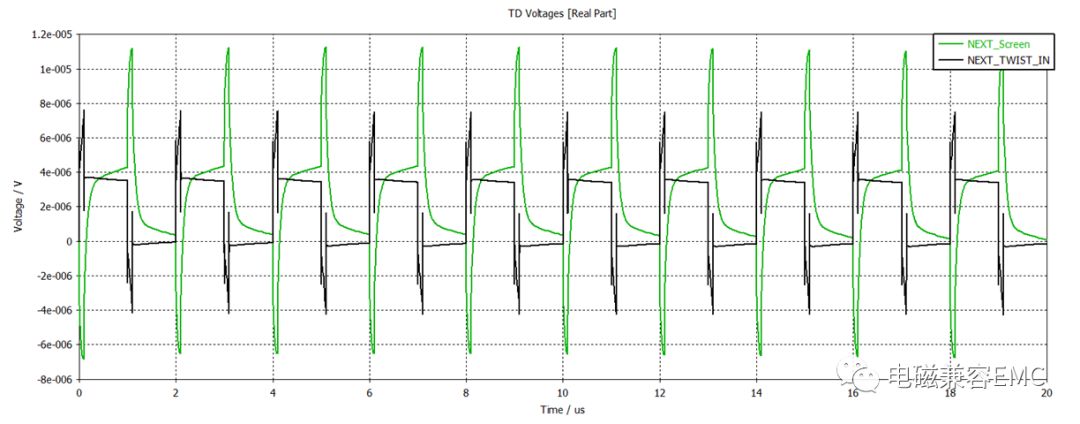

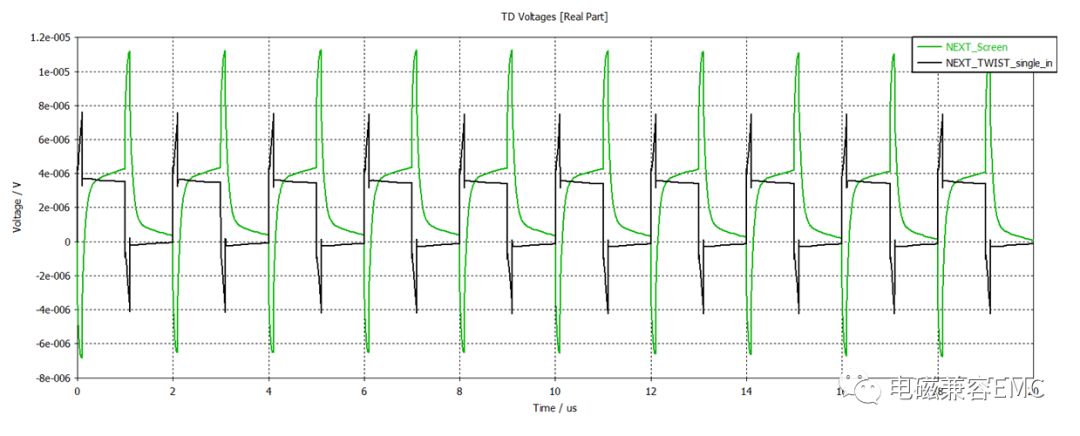

多数产品设计中往往采用了不同种规格的线束,既有单线,也有双绞线,同轴线,屏蔽双绞线,甚至多线束屏蔽线等等。那么,这些线束对串扰的防护能力分别如何呢?下面就对这个问题进行分析。

采用CST cable studio分别建立单线,双绞线,同轴线和屏蔽双绞线模型,如下图所示。

Fig52.仿真线束截面图

线束长度同样设置为100mm,线束间距为5mm,距离GND平面5mm。线束排列为,最下方施扰线(单线),向上每隔5mm以此是单线、双绞线、同轴线、屏蔽双绞线。提取S参数后的模型如下图所示。

注意:这里双绞线指的是差分双绞。

Fig53.线束拓扑图

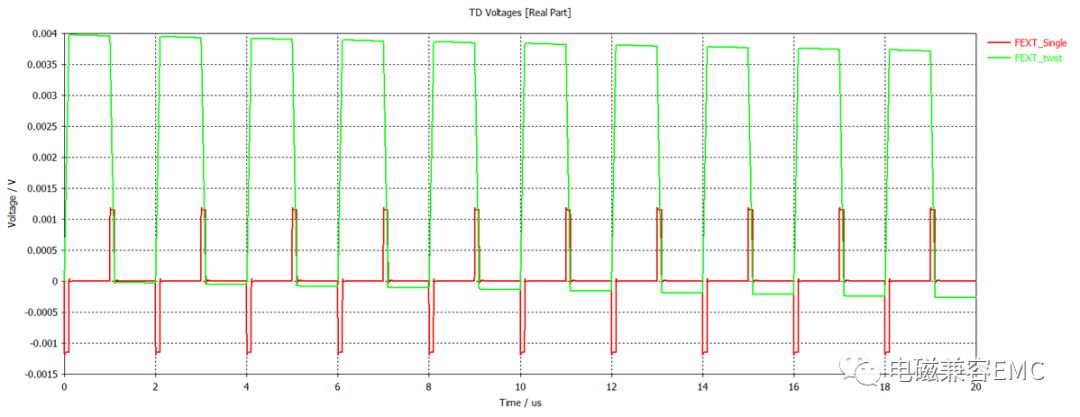

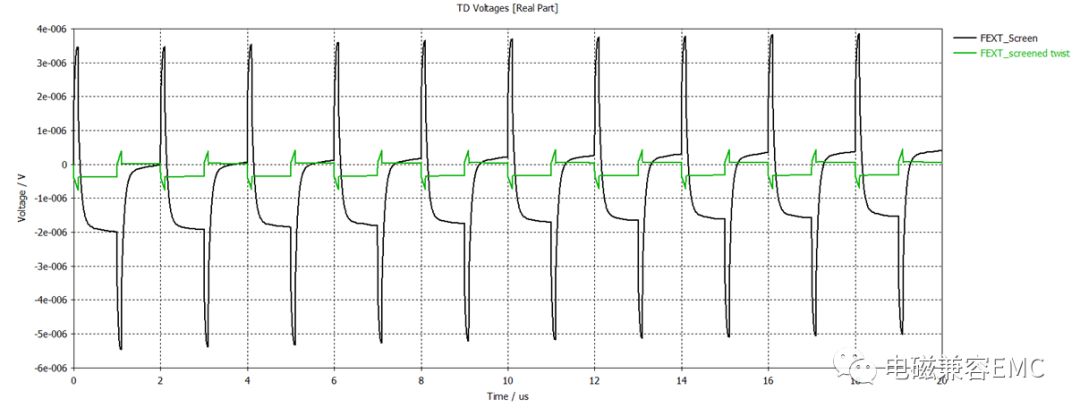

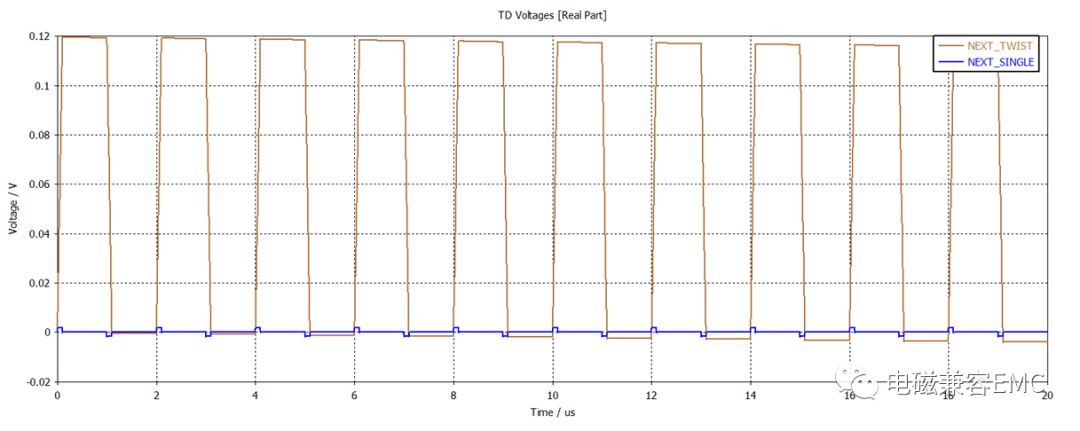

仿真完成后,查看各线束上噪声电压幅值,选择FEXT结果,可以看到相邻线束上噪声电压波形分别如下(数值差距太大,分别进行对比),可以看出,单线和双绞线上的串扰噪声远高于同轴线和屏蔽双绞线,而双绞线上噪声电平最高。多数工程师在产品设计中将线束双绞,这里可以看出双绞做法未必总是有利的,它并不会降低线束上的共模噪声,反而会增加噪声幅值。由互易定理可知,易耦合噪声的线束反过来也容易干扰其它线束,所以对于那些由于设计需要不得不双绞的线束(如非屏蔽网线,视频线,CAN线等),需要与其它线束保持距离(或者直接屏蔽),具体间距可以参考9.1节的结果。

Fig54.不同线束上远端串扰电压波形

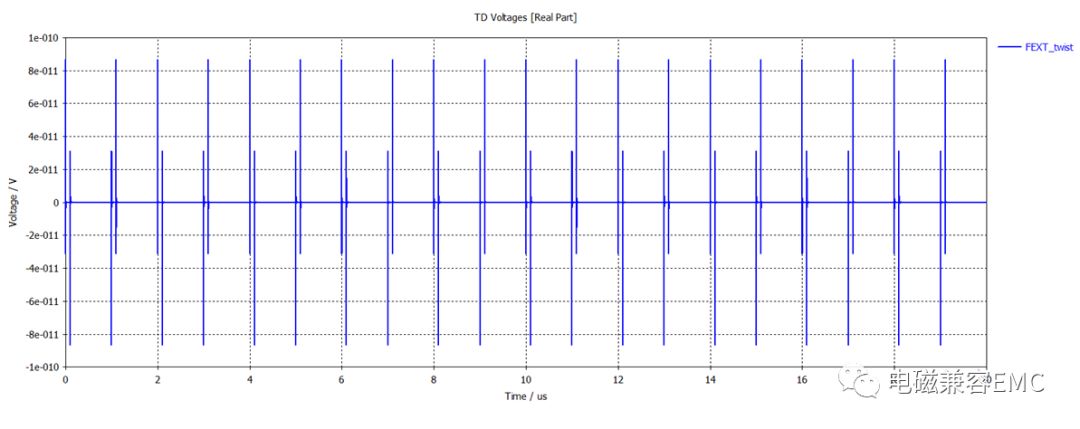

实际中当网线,视频线,CAN线等差分线中工作信号为差模,所以我们需要对差模信号上的串扰进行评估,而非共模。当改变测试探头后,我们可以看到,双绞线上差模噪声幅值是异常小的,小到只能单独拿出来查看。

注意:上图中的双绞屏蔽线结果为共模噪声,若是换为差模噪声,其幅值将会是最小的。

Fig55.双绞屏蔽线差模噪声电压波形

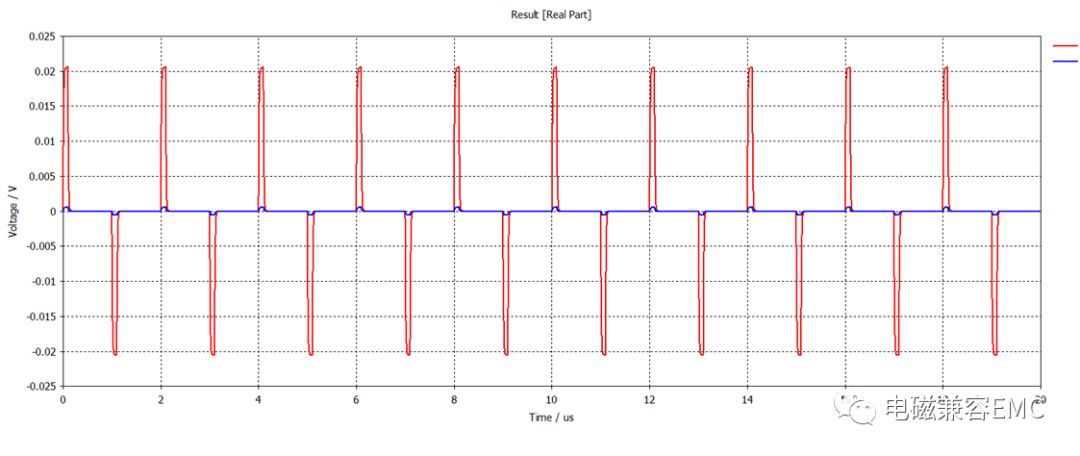

那么,对于那些将单线双绞起来的做法,是否会有差异呢,下图结果中可以直观的发现,将单线双绞后,噪声电平较未做双绞情况下降低了约30倍(假设单线输入阻抗都为10kΩ)。

Fig56.单线双绞前后近端串扰噪声电压波形变化

9.3、同一线束中的不同规格线缆间的串扰

实际产品设计中,我们会遇到各种类型的线束,如CAT5E_STP(超五类屏蔽线),CAT5E_UTP(超五类非屏蔽线),USBr3(USB3.0高速数据线)等等,并且线束厂家会满足客户对于线束设计的要求。那么,如此多种类的线束应该如何去设计呢?下图最后一张为自定义线束,与9.2节相同,一根大的屏蔽线束内包含了单线、双绞、同轴、屏蔽双绞等常见的线型。

Fig57.不同规格线束横截面

当在上图右下角的单线中注入噪声,我们观察其它同在一根线缆内的线束上噪声情况,以此来判断这条线束是否符合要求。首先我们查看其它线束上的共模和双绞线(差分)上的差模噪声。可以明显看出双绞线上差模噪声是最高的,单线次之,噪声最小的是屏蔽双绞线。

Fig58.线束内不同线间近端串扰电压波形

当双绞线为单线而非差分形式,我们关注的噪声模式转换为共模,再来查看线束上噪声情况我们会发现,双绞单线要比单线上噪声幅值低一倍还多。而同轴和屏蔽双绞线似乎没有什么变化。

Fig59.单线双绞后近端噪声电压波形

结论:线束设计中的串扰与线束的布局和处理方式相关,条件允许情况下,线束应该尽量单独屏蔽处理,若产品成本不允许,也可以通过双绞等方式对线束处理,从而降低串扰可能造成的影响。对于有复杂线束要求的设计,需要慎重考虑线束间的串扰可能造成的影响,这个串扰既有可能存在于同一线束内,也可能存在于不同线束间。

-

噪声

+关注

关注

13文章

1070浏览量

47059 -

串扰

+关注

关注

4文章

183浏览量

26776

原文标题:20180825-Crosstalk

文章出处:【微信号:EMC_EMI,微信公众号:电磁兼容EMC】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

串扰几种常见措施的效果及差异

串扰几种常见措施的效果及差异

评论