寄存器概述

寄存器是中央处理器内的组成部分。寄存器是有限存贮容量的高速存贮部件,它们可用来暂存指令、数据和地址。在中央处理器的控制部件中,包含的寄存器有指令寄存器(IR)和程序计数器(PC)。在中央处理器的算术及逻辑部件中,存器有累加器(ACC)。

寄存器的原理组成

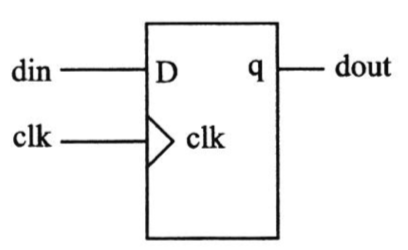

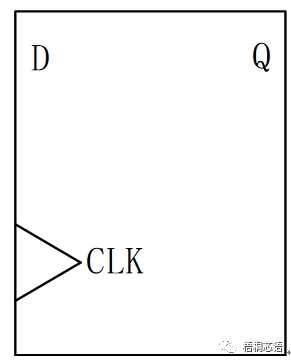

寄存器的基本单元是D触发器,按照其用途分为基本寄存器和移位寄存器。

基本寄存器是由D触发器组成,在CP脉冲作用下,每个D触发器能够寄存一位二进制码。在D=0时,寄存器储存为0,在D=1时,寄存器储存为1。

在低电平为0、高电平为1时,需将信号源与D间连接一反相器,这样就可以完成对数据的储存。

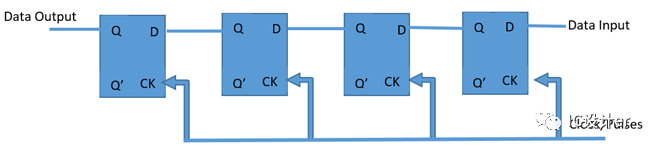

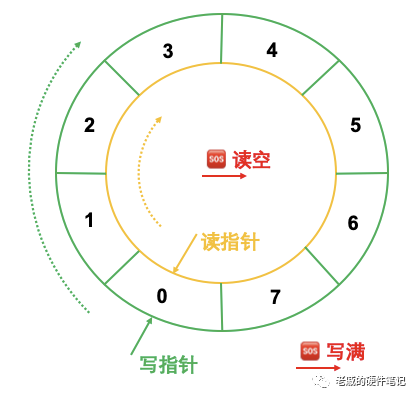

移位寄存器按照移位方向可以分为单向移位寄存器和双向移位寄存器。

单向移位寄存器是由多个D触发器串接而成。在串口Di输入需要储存的数据,触发器FF0就能够储存当前需要储存数据,在CP发出一次时钟控制脉冲时,串口Di同时输入第二个需要储存是的数据,而第一个数据则储存到触发器FF1中。

双向移位寄存器排列,调换连接端顺序,可以控制寄存器向左移位,增加控制电路可以使寄存器右移,这样构成双向移位寄存器。

ARM寄存器组成

在ARM状态,16个通用寄存器(R0-R15)和一个状态寄存器在任意时刻都可见。在特权(非用户)模式下,将切换到指定模式的分组(banked)寄存器。(PS.分组寄存器的概念下文可见)

ARM状态时寄存器被设为包含16个直接可以访问的寄存器:R0到R15。除了R15,其他全部寄存器都为通用寄存器,如可能用于保存数据或地址值。除此之外,还有第17个寄存器用于存储状态信息。

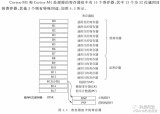

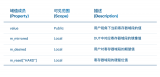

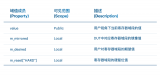

R8~R14、SPSR寄存器则被切换到各个模式下的私有寄存器组上,不同的模式下可以访问相应的私有寄存器。表1显示了在每种模式下,哪些寄存器是有效的(阴影部分的寄存器都是私有寄存器)。

表1 ARM状态下的寄存器组织结构

从表1中我们可以看出:

☆ R0~R7、R15、CPSR寄存器组在任何模式下都是共用的,可访问的;

☆ R8~R12寄存器组在快中断模式下(fiq)对应一套私有寄存器组R8_fiq~R12_fiq,在其他模式下共用另一套寄存器组;

☆ R13、R14寄存器在用户(user)和系统(sys)模式下共用一套;其他模式(管理(svc)、中止(abt)、未定义(und)、中断(irq)、快中断(fiq)模式)下都具有两个私有寄存器R13和R14。这就使得这些模式中的每一种模式都具有各自的堆栈寄存器指针R13和链接寄存器R14,分别用于堆栈处理和异常退出;

☆ SPSR寄存器可用于保存CPSR的值,在用户和系统模式下不能访问,在其他模式下都有私有的SPSR寄存器。

表1中第二列列举了寄存器在汇编语言中的名称,其中括号中的内容是别称。下面我们对这些寄存器的功能进行介绍。

1、一般通用寄存器 R0~R12

寄存器R0~R12为保存数据或地址值的一般通用寄存器。其中寄存器R0~R7为未分组的寄存器,R8~R12为分组寄存器。

未分组的寄存器意味着对于任何处理器模式,他们中的每一个都对应于相同的32位物理寄存器。他们是完全通用的寄存器,

分组寄存器意味着同一个寄存器名对应多个物理寄存器,具体所对应的物理寄存器取决于当前的处理器模式。参照表1,寄存器R8~R12有两个分组物理寄存器。一组用于除FIQ模式之外的所有寄存器模式(R8~R12),另一组用于FIQ模式(R8_fiq~R12_fiq)。、

寄存器R8~R12在ARM体系结构中没有特定的用途。不过对于那些只使用R8~R14来说就足够处理的简单的中断,FIQ所单独使用的这些寄存器可实现快速的中断处理。

2、堆栈指针 R13

寄存器R13(也称为堆栈指针或SP)有6个分组的物理寄存器,见表2-1。一个用于用户和系统模式,其余5个分别用于5种异常模式。

寄存器R13通常作为堆栈指针SP。在ARM指令集中,R13大都用在对各个模式下的堆栈操作。每个异常模式都具备私有的R13寄存器,它通常指向由异常模式所专用的堆栈。在入口处,通常将寄存器值保存到这个堆栈。在模式转换前将当前寄存器的值保存到堆栈中,然后从将要切换的模式堆栈中将这些值从堆栈重装到已切换的模式寄存器中,这种处理方法可确保异常发生时的程序状态不会被破坏。

3、链接寄存器 R14

寄存器R14(也称为链接寄存器或LR)有6个分组的物理寄存器,见表2-1。一个用于用户和系统模式,其余5个分别用于5种异常模式,对应的私有寄存器有R14_svc,R14_irq,R14_fiq,R14_abt和R14_und。寄存器R14有三种用途:

☆ 当发生异常时,它被设置为该异常返回地址;

☆ 在执行分支和链接(BL)指令时,它用于保存子程序的返回地址;

☆ 而在其他时候,可以作为一个通用寄存器来对待。

4、程序计数器 R15

寄存器R15(也称为程序计数器或PC)总是用于特殊用途,它总是指向下一条要读取指令的地址。你可以把R15当作通用寄存器使用,但使用时还有与指令有关的限制或特殊情况。如果R15使用的方式超过了这些限制,那么指令将是不可预测的。

由于ARM7采用3级流水线结构,在ARM状态下,读取R15的值是当前执行指令地址 + 8。ARM指令以字为单位,读取R15结果的bit[1:0]总是为0b00。

对R15进行写时,如果这条写指令没有超过对R15使用的限制,那么写入R15的正常结果值被当成一个指令地址,程序会从这个地址处继续执行(相当于执行无条件跳转指令)。因为ARM指令以字为边界,所以写入R15值的bit[1:0]通常为0b00。

5、CPSR和SPSR

所有模式共享一个程序状态寄存器CPSR。在异常模式中,程序状态保存寄存器SPSR可以被访问,每种异常具有自己私有的SPSR。在进入异常时,它保存CPSR的当前值;在异常退出时,可通过它(SPSR)恢复CPSR。

寄存器的用途

1.可将寄存器内的数据执行算术及逻辑运算。

2.存于寄存器内的地址可用来指向内存的某个位置,即寻址。

3.可以用来读写数据到电脑的周边设备。

-

寄存器

+关注

关注

30文章

5020浏览量

117630 -

D触发器

+关注

关注

2文章

147浏览量

47360

发布评论请先 登录

相关推荐

AFE模拟前端寄存器读取操作

CPU的6个主要寄存器

寄存器的主要组成部分及分类

移位寄存器的工作原理 移位寄存器左移和右移怎么算

CPSR寄存器和APSR寄存器的组成

什么是移位寄存器?数字电路中的寄存器类型有哪些呢?

寄存器由什么组成

寄存器由什么组成

评论