关于人工智能(AI)的报导一直不绝于耳。过去几年来,几乎每个月(有时甚至是每周)都会有一款现有或新创公司的全新AI处理器推出市场。然而,悬而未决的问题是:为什么有这么多的AI处理器?每一款AI晶片的设计是为了解决哪些问题?更重要的是,当今的AI版图中还缺少哪些部份?

Tirias Research首席分析师Kevin Krewell直截了当地说,「AI带来了一种新典范,并改变了整个电脑系统。」现有企业和新创公司都在争夺仍处于混乱中的「AI就绪」(AI-ready )运算领域。以色列Hailo是一家为「边缘装置深度学习」打造专用晶片的新创公司,今年6月宣布完成1,250万美元的A轮融资。Hailo的目标在于「为任何产品带来智慧」(to bring intelligence to any product)。因此,Hailo执行长Orr Danon最近呼吁「彻底重新设计电脑架构的支柱——存储器、控制和运算以及其间的关系。」

这是一个值得称道的目标。然而,Hailo既不打算透露其架构细节——Danon仅表示「可能就在今年底」,其首款AI处理器最快也要到2019年上半年后才会正式推出。

Danon认为,目前还没有一家自动驾驶车(AV)供应商能在无数的新一代AI处理器中找到适用于其AV的晶片。汽车领域正是Hailo看好其新款AI处理器得以发挥的直接目标市场。Danon指出,当今的测试AV实际上都在公共道路上行驶,车后行李箱中还配置了一个资料中心。他说,为了填补这些测试车和自动驾驶车(必须为大量部署而打造)之间的巨大鸿沟,一线(tier one)和汽车OEM需要一种全新的AI处理器,协助其更有效率地执行相同的深度学习任务。

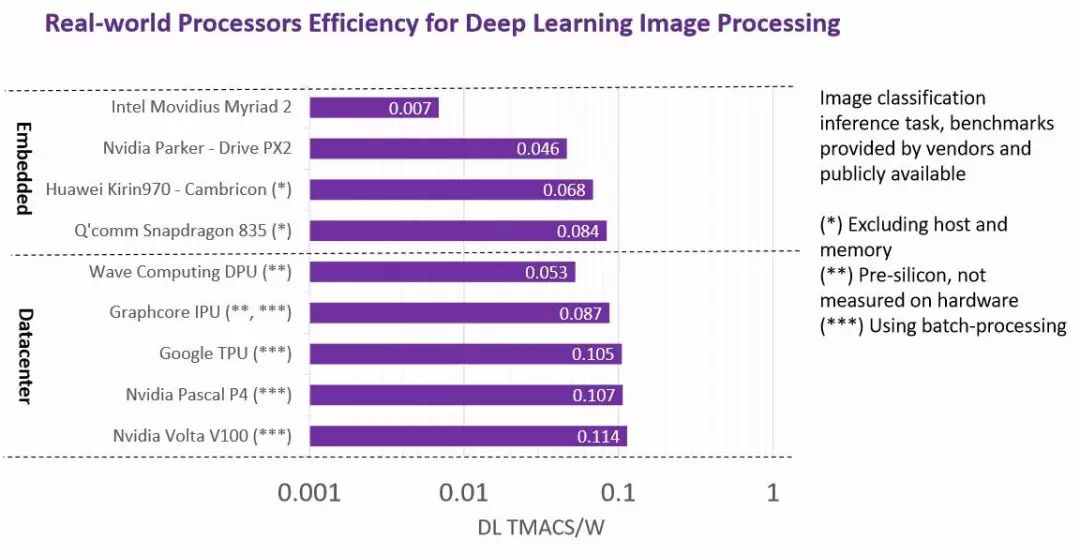

Hailo为此整理了目前每一款AI处理器的每瓦(W)深度学习TMACS。该公司与《EE Times》的读者分享的重点在于深入探讨:AV产业在多大程度上仍无法获得推动高度自动驾驶车所需的高效能AI处理器。

业界分析师和其他AI新创公司高层也针对目前在AI发展道路上的重大障碍发表看法。

现代CPU架构并不适用于AI

大多数业界观察家一致认为,目前基于冯·诺依曼(von Neumann)架构的CPU处理器无法有效因应当今的AI处理任务。The Linley Group首席分析师Linley Gwennap指出,「Von Neumann不适用于AI。」他解释说,每一次的运算都必须撷取并解码指令,以及收集并储存资料于暂存器档案中。「为了提高每瓦运算效能,你必须执行更多的运算和更少的撷取任务。」

Krewell同意这一看法。他说:「Von Neumann架构极其适于控制和循序计算:'If-Then-Else'操作。相形之下,神经网路就像图形一样,是高度平行的,而且依赖于存储器频宽的处理。试图用CPU扩展神经网路是相当昂贵的(包括功耗和成本)。」

典型的冯·诺依曼(von Neumann)电脑架构(来源:Hailo)

Danon说:「尽管Von Neumann架构和现代CPU一般都非常灵活,但在很多情况下,这种灵活性并不是必要的。」它适用于神经网路和其他操作,例如,为未来的许多周期预先确定行为。在这种情况下,他指出,设计系统的更有效方法是「避免以读取指令来指导每个周期的系统行为。保持每个周期改变元素行为的灵活度非常重要。」

在Danon看来,「神经网路将这一概念推向了极致。『结构』——决定运算元素之间连接性——确定整个会话的行为(又称『运算图形』)。」简言之,AI社群需要的不是基于Von Neumann架构的处理器,而是「善于描述神经网路结构的特定处理器」。

重新关注资料流架构

由于CPU和GPU的深度学习性能无法满足需求,引发业界积极寻找基于资料流(dataflow)架构的新解决方案。但为什么是资料流?

根据Gwenapp的说法,业界希望进行更多的运算和更少的撷取,首先尝试开发宽的单指令/多资料(SIMD)架构。「但是你只能将暂存器档案做得很宽。」业界很快地发现,该解决方案是「直接自动地将资料从运算单元移动到运算单元」。他说,「这是一种称为资料流的通用方法,可以大幅降低von Neumann的开销。」

不久前才收购MIPS的Wave Computing,是一家利用资料流技术的AI新创公司。根据该公司执行长Derek Meyer表示,Wave Computing设计了一款新的处理单元,「可以原生支援Google TensorFlow和微软(Microsoft)的CNTK」。

Danon坦承Hailo的新款AI处理器也属于架构的「资料流系列」。他解释说,资料流「通常更适合深度学习」,因为「用于计算的大多数参数都不需要移动。相反地,它们用于描述资料流动时的图形。」

资料流解决方案:典型的平行运算架构(来源:Hailo)

Krewell指出,资料流的概念并不是什么新鲜事儿,也已经成功地在通用电脑硬体实现商用化了。

但是,随着AI改变运算领域,资料流正在寻找机器学习的「新机遇」。Krewell补充说:「透过使用资料流和脉动阵列架构,您可以将神经网路处理设计为从一分层到另一分层,而无需太多控制逻辑。」

这种新转折可说是Wave Computing的天赐良机。该新创公司自2010年以来一直在利用其于资料流技术方面的专业知识以及建立专利组合,积极地专注于机器和深度学习。

存储器频宽面临瓶颈

AI——特别是卷积神经网路(CNN),似乎非常适合资料流设计。但是,Gwenapp强调,这并不表示所有的资料流设计都对AI有利,「系统中还存在着其他瓶颈,如存储器频宽。」

业界开始看到这样的暗示:存储器导向的装置是客制深度学习硬体的未来。例如,新创公司Mythic瞄准了将神经网路映射到NOR存储器阵列。该公司将「存储器处理器」(processor-in-memory;PIM)架构用于AI,使其晶片得以在快闪存储器中储存并处理神经网路权重,而其结果(最终和中间)则储存在SRAM中。因为这样的记忆体阵列无需将资料移入和移出外部存储器,所以,Mythic承诺将在其晶片中实现性能/功耗的巨大进展。

存储器处理器(PIM)(来源:Mythic)

Mythic的设计概念当然具有吸引力,特别是当大多数晶片设计者试图提高存储器频宽时,一般都采用可能造成破坏的方法。然而,Danon抱持谨慎看法,他表示还不确定Mythic的存储器处理器晶片能否正常运作,但很可能「将技术推得太远了」。

Danon说,目前更实际和更现实的方法是「共同定位存储器和运算」。「我们需要让运算结构能以高利用率存取所需的存储器,从而产生非常高的频宽。」他补充说,这对于实现运算元素的高利用率至关重要。

Krewell则解释,「一些挑战是在训练期间保持权重。这就是像GraphCore在晶片上打造大型存储器的原因。」他并补充说:「这也就是为什么GPU和英特尔(Intel)的Nervana使用高频宽存储器(HBM)、Wave Computing使用美光(Micron) Hypercube存储器的原因。」

除了TPU,如何调整软体和硬体?

Danon表示,Google经由其Tensor处理器,「展示了一种样板」,用于从头开始设计高效率的架构,并针对推论任务进行了最佳化。这是个大好消息。然而,坏消息是,如果客户想要使用除了TensorFlow之外的深度学习架构呢?

在这种情况下,他们就需要翻译。虽然许多新兴工具,包括ONNX,都用于翻译几个AI架构,但Danon解释说,在此过程中,即使内容不会在翻译中完全遗失,计算也可能变得「非常低效」。他指出,产生这种困境的原因在于,以简洁方式描述问题的神经网路「结构」必须转换为von Neumann架构的通用处理器所使用的一系列规则操作。

Danon指出,当今的AI处理器在软体和硬体之间缺乏一致性。他说,在理想情况下,软体和硬体二者都使用基于结构的描述方法。Hailo计划将本机描述为「神经网路分层」,从而使其处理器有别于其他处理器。

Danon解释说,Hailo的目标「有点类似于组合语言本身能够在基于规则的系统中描述规则一样——条件叙述和分支的形式。」

实现更高每瓦性能的竞赛

深度学习性能效率是AI处理器竞争对手之间经常引爆的一场大辩论。在辉达(Nvidia)和英特尔/Mobileye之间,两家竞争对手的高层还公开争辩其于Xavier SoC和EyeQ5的主张。

针对深度学习影像进行处理的实际处理器效率比较(来源:Hailo)

Hailo根据每家供应商发布的资料,编制了一份AI处理器比较表——从Nvidia的Volta V100、Pascal P4和Google TPU,到GraphCore IPU和Wave Computing DPU,详细列出每家供应商的深度学习tera级每秒乘积累加(TMAC)运算和功耗资料。Hailo的目标是为每个AI处理器计算深度学习的每瓦TMACS。Hailo并观察到当前的AI处理器可达到每瓦低于0.1TMACS的效能,而在使用批次处理方法时可能略高于此。

神经网路(来源:Hailo)

Danon以处理高解析(HD)视讯为例指出,如果车辆以每秒30格(30f/s)的速度接收全高解析(FHD)视讯,并使用ResNet50网路进行深度学习。处理FHD视讯串流通常需要每个感测器约5TMACS。根据自动驾驶的等级,一般汽车预计将配备4到12个摄影机感测器。

这意味着部署在自动驾驶车的任何现有AI处理器已经让每个感测器消耗约几十瓦功耗,或每辆汽车几百瓦了。Danon认为这已经超出太多了。或者,他怀疑,如果OEM无力应付这么多的电力浪费,他们别无选择,最终将只能在性能上大幅妥协。

理论上,「相较于传统的von Neumann处理器,精心设计的CNN加速器应该能达到更高数十倍的每瓦性能」。但是,Gwenapp说:「即便采用这种方法也不足以满足4/5级自动驾驶车的挑战性要求。」

换句话说,尽管市场上充斥过多的AI处理器,但没有一款能够达到让全自动驾驶车实现商用化可行的性能标准。

但Gwennap仍抱持乐观看法。「幸运的是,我们还处于AI竞赛的早期阶段。预计在未来十年内将能在硬体和软体方面看到大幅的进展。」

-

处理器

+关注

关注

68文章

18240浏览量

222016 -

cpu

+关注

关注

68文章

10428浏览量

206515 -

人工智能

+关注

关注

1776文章

43766浏览量

230552

原文标题:自驾车AI芯片到位了吗?

文章出处:【微信号:Imgtec,微信公众号:Imagination Tech】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

现代CPU架构并不适用于AI,如何调整软体和硬体?

现代CPU架构并不适用于AI,如何调整软体和硬体?

评论