内置分频, 倍频电路超小型PLL时钟发生器

XC25BS8系列是能在低频输入8kHz, 4095倍的范围内倍频工作的PLL时钟发生器IC。

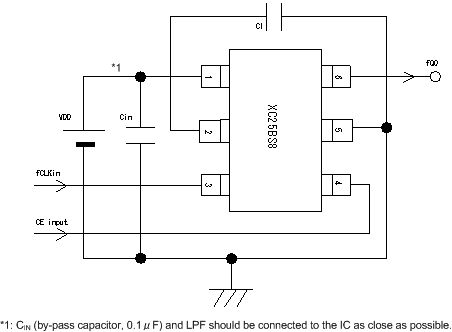

小型化, 同步抖动小, 实现128倍, 256倍, 512倍等高倍频。分频电路, 相位频率比较器, 电荷泵, VCO内置,不需要复杂的滤波因子的计算,只需要加上电源和输入时钟就可简单实现时钟变换。另外,可用于和音频DAC的LR时钟相位同步的噪声修整用的主时钟的生成等,也适用于生成各种必须和输入信号同步的同步信号。

输入端分频因子(M)可从1~2047的分频范围内进行选择;输出端分频因子(N)可从1~4095的分频范围内进行选择。输出频率在1MHz~100MHz的范围内,输入时钟为8kHz~36MHz的标准时钟。在内部可进行微调,在少量外置部件的条件下动作。

从CE端子输入低电平信号,可停止整个芯片动作,抑制消耗电流,此时的输出状态为高阻抗。可以选择SOT-26W和USP-6C封装。

此外,本产品的输入端分频因子(M), 输出端分频因子(N), 以及电压泵电流(Ip)的设定值,均可按客户要求时提供部分的客户定制品。有需要时请提供详细的规格要求(输入输出频率,工作电源电压),并提前向本公司的各分公司询问对应的可能性。

典型电路框图

特点

封装

-

发生器

+关注

关注

3文章

1286浏览量

60766 -

时钟发生器

+关注

关注

1文章

167浏览量

66961

原文标题:可在低频输入8kHz, 4095倍的范围内倍频工作的小型化PLL时钟发生器IC,了解一下!

文章出处:【微信号:gh_454737165c13,微信公众号:Torex产品资讯】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

用于评估AD9576时钟倍频器异步时钟发生器的评估板AD9576/PCBZ

AD9571ACPZPEC时钟发生器销售

时钟发生器AD9577资料分享

低抖动高精度时钟发生器MAX3625B相关资料分享

基于FPGA 的新的DDS+PLL时钟发生器

评估低抖动PLL时钟发生器的电源噪声抑制性能

MAX3625B 抖动仅为0.36ps的PLL时钟发生器

HMC1031:0.1 MHz至500 MHz时钟发生器,带整数N PLL数据表

AD9573:PCI-Express时钟发生器IC,PLL内核,分频器,双输出数据表

评估低抖动PLL时钟发生器的电源噪声抑制

内置分频, 倍频电路超小型PLL时钟发生器

内置分频, 倍频电路超小型PLL时钟发生器

评论