声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ti

+关注

关注

111文章

8136浏览量

210909 -

webench

+关注

关注

19文章

67浏览量

27725

发布评论请先 登录

相关推荐

瑞萨宣布推出一种全新超低25fs-rms时钟解决方案—FemtoClock™ 3

2024 年 4 月 18 日,全球半导体解决方案供应商瑞萨电子(TSE:6723)宣布推出适用于有线基础设施、数据中心和工业应用的全新超低25fs-rms时钟解决方案——FemtoClock™ 3,从而扩展其

UltraScale系列与7系列FPGA的差异

已从该架构中移除BUFMRs、BUFRs、BUFIOs及其相关的路由资源,并被新的时钟缓冲器、时钟路由和全新的I/O时钟架构所取代。

虹科干货 | 适用于基于FPGA的网络设备的IEEE 1588透明时钟架构

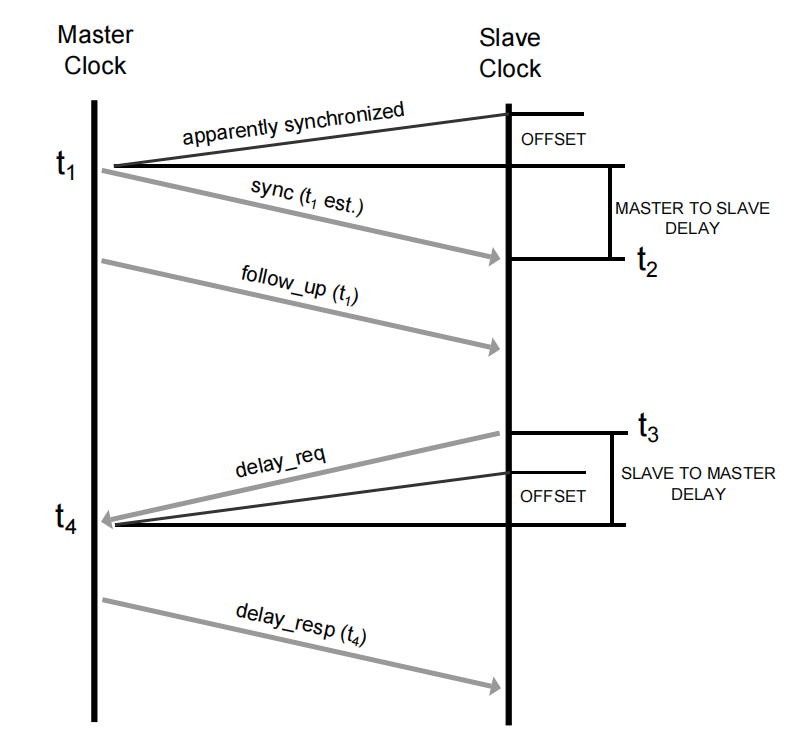

的IEEE 1588透明时钟(TC)架构,帮助您实现精确时间同步和高效通信。 在分布式系统中,传感器/执行器的事件和操作需要进行精确的时间协调,因为时钟差异可能导致操作失败。为了确保时间同步,每个组件都需要具备与其对等组件一致的

适用于基于FPGA的网络设备的IEEE 1588透明时钟架构

的IEEE1588透明时钟(TC)架构,帮助您实现精确时间同步和高效通信。在分布式系统中,传感器/执行器的事件和操作需要进行精确的时间协调,因为时钟差异可能导致操作失败。

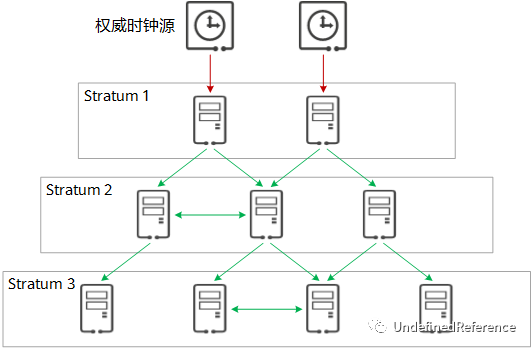

ntp同步原理和时钟层级

。通常将从权威时钟获得时钟同步的ntp服务器的层数设置为Stratum1,并将其作为主时间服务器,为网络中其他的设备提供时钟同步。而Stratum 2则从Stratum 1获取时间,S

驱动开发时钟API的使用

clocks-names = "mmc0" ; // 时钟名,调用devm_clk_get获取时钟时,可以传入该名字 ...... }; 以mmc的设备节点为例,上述mmc0指定了时钟

一键获取逻辑设计中的所有跨时钟路径

之前在玩FPGA时,对于一个系统工程,当逻辑电路设计完成之后,一般会先拿给Vivado/Quartus先去跑一般综合,然后去获取所有的跨时钟路径,在ASIC里,基本也是拿EDA工具去分析获取。今儿个搞个小demo,看在Spina

FPGA设计中动态时钟的使用方法

时钟是每个 FPGA 设计的核心。如果我们正确地设计时钟架构、没有 CDC 问题并正确进行约束设计,就可以减少与工具斗争的时间。

发表于 07-12 11:17

•821次阅读

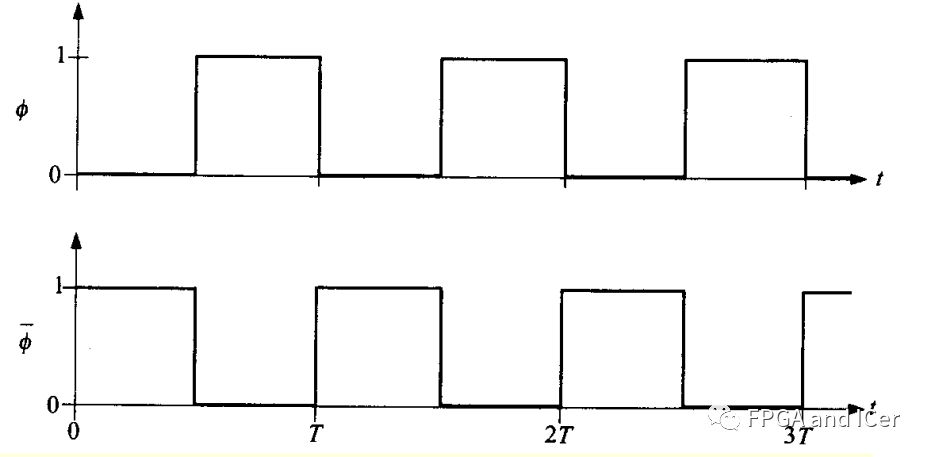

谈谈非理想时钟的时钟偏差

本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。在FPGA和ASIC设计中,时钟信号的好坏很大程度上影响了整个系统的稳定性,本文主要介绍了数字设计中的非理想时钟的偏差来源与影响。

MEMS时钟解决方案创新者Stathera宣布A轮募资达1500万美元

“在同步下一代电子产品方面,使用传统时钟架构的技术扩展遇到了瓶颈。Stathera的技术引入了一种集成和制造时钟器件的新方法。”Stathera首席执行官(CEO)兼联合创始人George Xereas表示,“我们很高兴成为唯一一家拥有最先进DualMode频率技术的公司

WEBENCH® 时钟架构如何获取完整、优化的时钟树解决方案?

WEBENCH® 时钟架构如何获取完整、优化的时钟树解决方案?

评论