前言

在过去的几年里,我们目睹了数据的一系列巨大变化,包括数据如何被生成、处理以及进一步利用以获取额外的价值和智能,而这些变化都受到以深度学习和神经网络应用为基础的新兴计算模式所影响。这种深刻的变化始于数据中心,其利用深度学习技术来提供对海量数据的洞察,主要用于分类或识别图像、支持自然语言处理或语音处理,或者理解、生成或成功学习如何玩复杂的策略游戏。这种变化催生了一批专门针对这些类别的问题而设计的高功效计算设备(基于GP-GPU和FPGA),后来还产生了可完全定制的ASIC,进一步加速并提高了基于深度学习的系统的计算能力。

大数据和快速数据

大数据应用采用专门的GP-GPU、FPGA和ASIC处理器透过深度学习技术来分析大型数据集,并揭示趋势、模式和关联性,从而实现图像识别、语音识别等功能。因此,大数据是基于过去的信息或常驻在云端的静止数据。大数据分析的一个常用的功能是执行特定任务“训练过的”神经网络,例如识别和标记图像或视频序列中的所有面部,语音识别也展示了神经网络的强大功能。

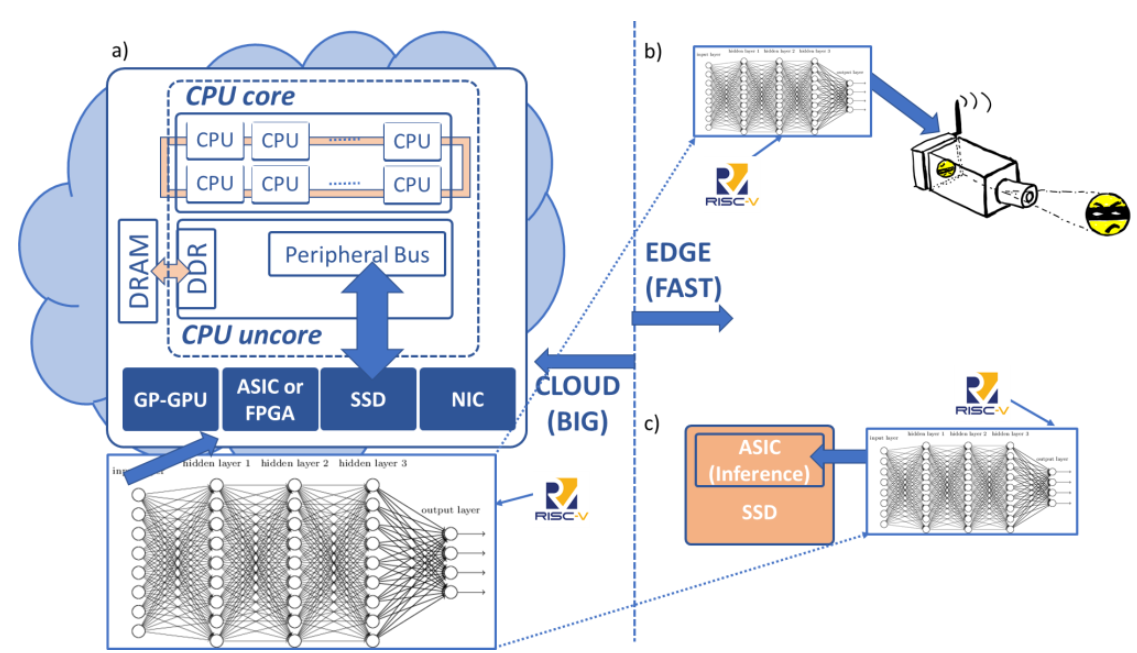

这种任务最好由专门的引擎(或推理引擎)来执行,这种引擎直接驻留在边缘设备上并由快速数据应用程序(图1)来引导。通过在边缘设备上处理本地所捕获的数据,快速数据能够利用来自大数据的算法提供实时决策和结果。大数据提供了从“过去发生了什么”到“将来可能会发生什么”所演绎出的洞察(预测分析),而快速数据则提供了能够改善业务决策、运营并减少低效情形的实时行动,所以这一定会影响最终结果。这些方法可以适用于各种边缘和存储设备,例如照相机、智能手机和固态硬盘。

在数据上进行计算

新的工作负载基于两种场景:(1)针对特定工作负载(例如图像或语音识别)训练大型神经网络;以及(2)在边缘设备上应用经过训练的(或“适合的”)神经网络。两种工作负载都需要大规模并行的数据处理,其中包括大矩阵的乘法和卷积。这些计算功能的最佳实施方式需要在大矢量或数据阵列上运行的矢量指令。RISC-V就是一种非常适合于此类型应用的架构和生态系统,因为它提供了一套由开源软件支持的标准化过程,使得开发人员能够完全自由地采用、修改甚至添加专有矢量指令。图1中概述了一些显而易见的RISC-V计算架构机会。

移动数据

快速数据和边缘计算的出现产生了一个实际的后果,即:与云端之间来回移动所有数据进行计算分析并不是一件有效率的事。首先,在移动网络和以太网中进行远距离传输时,它涉及到相对较大的数据延迟传输,这对于必须实时操作的图像识别或语音识别应用而言并不是理想的。其次,在边缘设备上进行计算需要更易于伸缩的架构,其中,图像和语音处理或者在SSD上进行的内存计算操作都可用一种伸缩的方式来进行。采用这种方式,每一台新增的边缘设备都会带来所需要的增量计算能力,对数据移动方式和时间进行优化是这种架构可伸缩性的一项关键因素。

图1:大数据、快速数据和RISC-V机会

在图1a中,云数据中心服务器利用在大型大数据集上训练的深度学习神经网络来执行机器学习的功能。在图1b中,边缘设备中的安全摄像机采用经过大数据训练的推理引擎来实时识别图像(快速数据)。在图1c中,智能固态硬盘设备采用推理引擎进行数据识别和分类,从而有效地利用了此设备的带宽。图1展示了RISC-V内核的潜在机会,它可以自由地添加专有的及未来标准化的矢量指令,这些指令对于处理深度学习和推理技术相当有效。

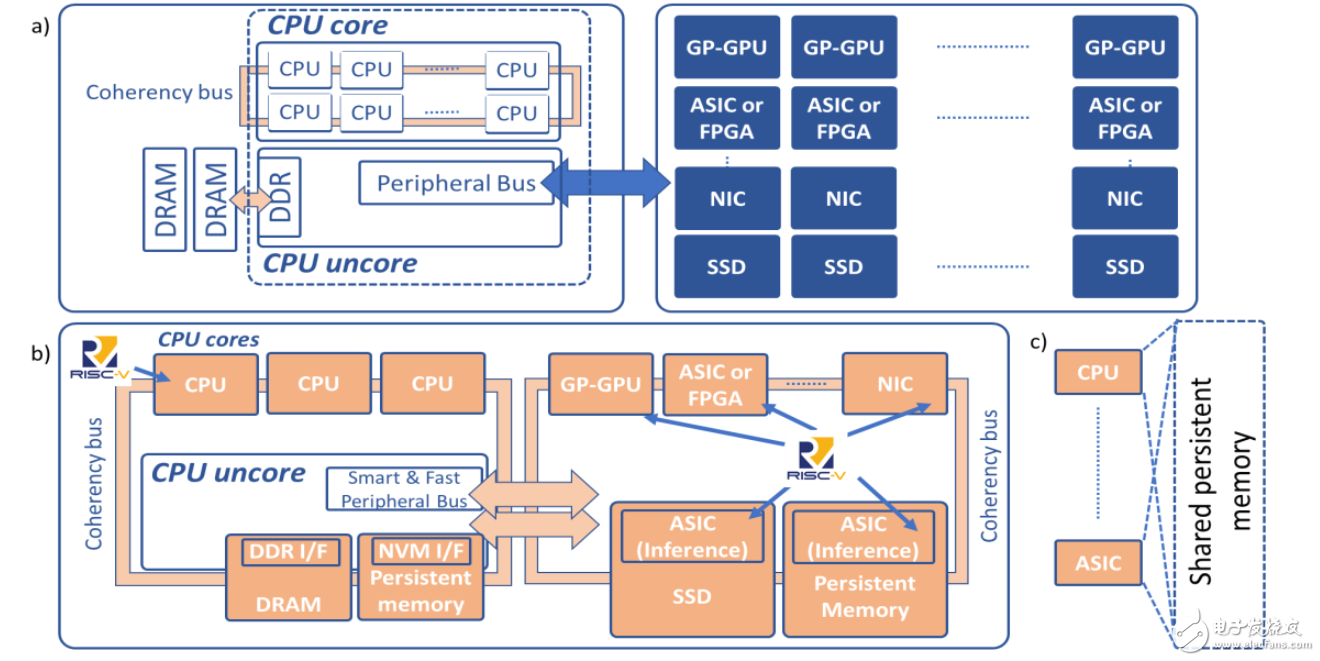

另一个类似且重要的趋势是大数据端和云端上数据的移动及访问方式(图2)。传统的计算机体系结构(图2a)采用慢速外围总线,该总线连接到许多其他设备(例如,专用机器学习加速器、图形卡、高速固态硬盘、智能网络控制器,等等)。低速总线会影响设备的利用率,因为它限制了总线本身、主CPU以及主要的潜在持久内存之间的通信能力。这些新型计算设备也不可能在它们之间或与主CPU共享内存,从而导致在慢速总线上进行徒劳且受限制的数据移动。

关于如何改善不同计算设备(例如CPU和计算机及网络加速器)之间的数据移动,以及如何在内存或快速存储中访问数据,出现了几个重要的行业趋势。这些新趋势集中在开放标准化工作上,能够提供更快、更低延迟的串行结构以及更智能的逻辑协议,从而实现对共享内存的一致访问。

新一代以数据为中心的计算

未来的架构将需要部署开放接口,以连接到持久性内存以及接入计算加速器并支持高速缓存一致性的快速总线(例如TileLink、RapidIO®、OpenCAPI™和Gen-Z),以期大幅度提高性能,而且使所有设备共享内存并减少不必要的数据移动。

图2:计算体系结构中的数据移动和访问

在图2a中,传统的计算体系结构由于把一条慢速外设总线用于快速存储器及计算加速设备,其能力已达到其极限。在图2b中,未来的计算体系结构采用了开放接口,能够为平台上所有的计算资源提供统一并支持高速缓存一致性的访问方式来访问共享持久内存,(这称为以数据为中心的体系结构)。在图2c中,所部署的设备能够使用相同的共享内存,从而减少了不必要的数据复制。

CPU 外围核心及网络接口控制器的作用将成为支持数据移动的关键因素。CPU外围核心组件必须支持密钥内存和永久内存接口(例如NVDIMM-P),也必须支持驻留在CPU附近的内存。还需要实施面向计算加速器、智能网络和远程持久内存的智能快速总线。这种总线上的任何设备(例如CPU、通用或专用计算加速器、网络适配器、存储器或内存)都可以包含其自己的计算资源并具有访问共享内存的能力(图2b和图2c)。

RISC-V技术正是优化数据移动的关键推动因素,因为它能够在所有的计算加速器设备上针对新的机器学习工作负载来执行矢量指令。它实现了多种开源CPU技术,能够支持开放内存和智能总线接口;且实现了以数据为中心具有一致性共享内存的体系结构。

利用RISC-V解决挑战

大数据和快速数据为未来的数据移动带来了挑战,也为RISC-V指令集架构(ISA)铺平了道路。这种架构开放的、模块化的方法非常适合用作以数据为中心的计算体系结构的基础。它提供了以下功能:

扩展边缘计算设备的计算资源

添加新的指令,例如用于机器学习工作负载的矢量指令

寻找非常接近于存储器和内存介质的小型计算内核

支持新型计算范式以及模块化芯片设计方法

支持新型以数据为中心的体系结构,其中所有的处理单元都可以透过一致的方式访问共享的持久内存,从而优化数据移动

RISC-V由超过100个组织机构的众多成员共同开发,这其中包含一个由软件和硬件创新者组成的协作性社区。这些创新者能够对ISA进行改编,使其适应特定的目的或项目。任何加入该组织的人都可以根据一份“Berkeley Software Distribution”(BSD软件发布)许可证来设计、制造和/或销售RISC-V芯片和软件。

结语

为了实现其价值和可能性,数据需要捕获、保存、访问并转换,以发挥其全部潜力。含有大数据和快速数据应用的环境已经使通用计算体系结构的处理能力相形见绌。未来以数据为中心的极端应用将需要针对特定用途设计的处理能力,以便以开放的方式支持数据资源的独立扩展。

拥有一套以在持久内存中存储的数据为中心的通用开放计算机体系结构,同时又能够让所有的设备发挥一定的计算作用,这是由新类型机器学习计算工作负载所推动的这些新型可扩展体系结构得以出现的关键因素。跨越云端及边缘设备各个部分的下一代应用都需要这种新型的低能耗处理方式,因为专门的计算加速处理器将能够专注于处理其手边的任务,从而能够减少来回移动数据所浪费的时间,或者能够执行与数据无关的额外计算。通过发挥数据的力量、潜力和可能性,人类、社会以及我们的星球都能够蓬勃发展。

作者:Zvonimir Bandic博士

西部数据公司, 研发工程部

新一代平台技术高级总监

-

asic

+关注

关注

34文章

1150浏览量

119255 -

大数据

+关注

关注

64文章

8643浏览量

136585 -

深度学习

+关注

关注

73文章

5235浏览量

119893 -

RISC-V

+关注

关注

41文章

1897浏览量

45044

发布评论请先 登录

相关推荐

以数据为中心的计算如何以RISC-V解决问题

以数据为中心的计算如何以RISC-V解决问题

评论