2018年6月4日,国内ADAS公司Maxieye智驾科技对外宣布,公司已推出第二代前装量产前视产品IFVS-400,该产品基于低成本的ASIC芯片进行开发,采用深度学习算法,支持L2/ L3级的自动驾驶方案。

ADAS公司使用ASIC芯片,在业内并不多见,目前大部分初创的公司,在一些量产项目中,使用的大都是FPGA的方案,这主要是出于灵活、成本、车规等因素。

之所以选择ASIC的方式,MaxieyeCEO周圣砚表示:ASIC先期开发周期较长,但FPGA或GPU+FPGA异构只是整个市场在2017年之前的“权宜之计”。到了2018年,FPGA的成本和计算优势相对减弱, ASIC的成本大约是其20%-30%左右。

随着高通、TI、瑞萨、NXP等汽车电子巨头均在2014年前后着手研发基于深度学习的处理器单元,他们普遍选择ASIC路线。未来随着ASIC的产销量上升,价格、成本的优势会凸显出来。

ASIC的长与短

ASIC(Application Specific Integrated Circuit)为专用集成电路,是泛指面向特定功能的芯片,比如专用的音频、视频处理器,具有体积小、功耗低、高可靠性、保密性强、计算性能高、计算效率高等优势。

在汽车行业,ASIC的传统应用领域是三电控制、制动、加速、转向控制,ABS、TSC、 ESP,以及各传感器、传感器接口等,主要的供应商由NXP(Freescale)、瑞萨、TI、ST等传统巨头提供。

ASIC更多的是面向特定用途或用户的特定要求的全定制、半定制集成电路,研制成本比较高,从设计到流片的时间流程比较长(一般在半年以上)。

但是对于使用芯片的最终客户来说,具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检验等优点。

设计并生产一颗ASIC的流程,大致为系统设计,详细设计,RTL级编码,RTL级仿真,利用综合工具生成网表和SDF文件进行前仿真,布局布线,后仿真,样片生产,协同软硬件调试。

FPGA与之不同的是,在进行完综合和编译,生成网表后,如果没有问题即可在FPGA母片上进行烧录测试,进行系统级验证。

相比较而言,FPGA实现比用ASIC实现可以节省一次后仿真和样片的生产2个步骤,根据不同的设计和工艺厂家这2个步骤通常需要6周或更长时间,如果需要量产那么如果使用ASIC那么第一批量产芯片还需要5周或更长时间。

但如果样片出错就至少还需要6周或更长时间,所以从产品的时间成本上来看FPGA具有比较大的优势,它大量用于生产至少可以比ASIC快3个月的时间。

当然这一点的不同,也会造成另外一个问题:如ASIC一旦出错,改动成本较高,需要推倒重来,这无论从成本还是在时间上,都需要耗费更多。

而FPGA则在没有较大的改动下,只需要通过重新烧录升级即可,在新产品推出的过程中,比ASIC拥有更多的灵活性。也因此,ASIC一般都是用于市场上已经成熟稳定的技术。

门阵列和标准单元

ASIC芯片主要由半导体厂家采用半定制的方法制造,常用的有门阵列(Gate Array)和标准单元(Standard Cell)两种类型。门阵列和标准单元的内部结构不同,使用的制造技术也不一样,因而他们的成本,生产时间,效率也不一样。

门阵列是一种用掩膜版编程的集成电路设计技术,包括COMS门阵列,射极耦合逻辑(ECL)门阵列,BiCMOS门阵列,数字和模拟兼容门阵列。半导体厂家预先在芯片上制备逻辑门或元件的规则阵列,一直加工到互连线光刻之前一道工序,这样的半成品芯片被称为门阵列母片。

然后,厂家根据客户的要求,设计互连线版图并进行制版及光刻加工,芯片就成为一个满足用户要求的专用集成电路。

门阵列母片可以大量生产,只需改变互连线版图,即可适应多品种的要求。通常编程的工艺层只限于最后的互连线(单层或多层布线层)。门阵列设计技术的优点是周期短,成本低,成功率高,可靠性好;但也存在着设计不够灵活,门的利用率低,功耗较大等缺点。

标准单元是目前使用较多的一种半定制芯片。半导体厂家预先设计好具有一定逻辑功能的单元电路(如触发器,加法器,计数器和RAM等),并且这些单元电路的布局布线工作已经完成,经过严格的测试,能保证逻辑功能和良好的时序功能,然后以标准单元库的形式提供给设计者。

ASIC设计者能把这些已经具有一定功能的单元连接到一起实现所需要的功能,尽可能以最优化的方式布局布线到晶片上。

与门阵列不同的是,尽管这些标准逻辑单元已经预先设计好,但并不预先放到晶片中(因为厂家事先不知道设计者的设计情况,没有一种通用的方式决定各种逻辑单元使用的数量和具体的摆放位置)。因而标准单元设计没有母片的概念。每块晶片都是根据设计者的需求临时制作的,晶片内部最基本的晶体管都是现场刻制的。

所以,标准逻辑单元的生产周期较门阵列较长。由于标准单元的每一层掩膜都是根据不同用户的需求定制的,用户不能共享开发成本,因而标准单元专用集成电路的试制费比门阵列专用集成电路要高。

标准单元结构的优点是晶片体积小,可以支持很复杂的设计,批量生产单片成本低,用户定制性好。对于门阵列来说,母片是事先生产好的,晶片尺寸已经固定下来,片内的资源均匀分布在片内,许多资源可能得不到充分利用。

但是,对于标准单元来说,只有需要的标准单元才会被放置到晶片中,所以晶片的尺寸越小,每块晶圆能够切割的晶片数量就越多,单片的成本越低。这是在大批量生产时标准单元结构专用集成电路的优势。

ASIC还站在前哨

2017年底,蔚来汽车在发布的第一款自动驾驶量产车型ES8上,选择了Mobileye EyeQ4芯片,其最高运算速率为2.5万亿次/秒,功耗为3W,该芯片属于ASIC芯片。

EyeQ4使用了一组工作在1GHZ的工业级四核MIPS处理器,以支持多线程技术对数据的控制和管理;多个专用的向量微码处理器(VMP),用来应对ADAS相关的图像处理任务;一颗军工级MIPS Warrior CPU位于次级传输管理中心,用于处理片内片外的通用数据。

同年,马斯克在一个场合透露了“特斯拉正在造自己的芯片”的消息,马斯克明确称”吉姆正在开发专门的AI硬件。而这个“专门的AI硬件”指的很可能就是ASIC芯片。

地平线也在2017年年底推出了ASIC人工智能专用芯片,其中针对中自动驾驶专用芯片征程1.0,由晶圆代工伙伴台积电先进工艺制程生产。NPU(Neural Processing Unit)能效可以提升2-3个数量级(100-1000倍左右),具有高性能、低功耗、低成本等特点。

国内外厂商在零星的推出自动驾驶的ASIC芯片,而传统的汽车芯片厂商,却并没有急于宣布进入这个蓝海。

在芯片行业内工作多年的人士告诉《高工智能汽车》,ASIC的优势,主要在于应用于成熟稳定的技术,不需要不断升级更新,同时在使用使用量上要有保证,才会体现出成本、可靠性的优势。

在目前技术条件下,用于自动驾驶的算法、控制类ASIC芯片还尚处早期,这主要是源于自动驾驶的算法在一直更新,演进,尚未定型。

而未来自动驾驶的应用中,更强调的是集成性,各个固定的自动驾驶算法可能会以IP核的形式嵌入到中央处理系统中。

FPGA的力挺者

为了重申其于汽车产业的长期投入,以及看好FPGA将在自动驾驶领域发挥重要作用,全球最大的FPGA供应商之一赛灵思(Xilinx)近年来不断加大市场的培育力度。

尽管在此之前,FPGA更多用于车载信息娱乐系统,但赛灵思坚定认为,FPGA最适合用于处理越来越复杂的ADAS和自动驾驶。

而在在ADAS领域,赛灵思的FPGA也到了不少初创公司的采用,并用于处理来自各种车身传感器(包括摄像头、毫米波雷达等)的数据。FPGA可利用其DSP与平行架构,提供极其适合神经网路加速的运算能力。

赛灵思曾经对外宣称自己在车用视觉处理市场占有率排名第二,仅次于Mobileye,尽管双方的市场份额存在着巨大差距。不过,赛灵思表示,目前公司与Bosch、Magna和Continental等多家汽车一级零部件供应商都有合作。

在中国市场,赛灵思也在开拓ADAS初创公司的市场。

近日,AI初创公司深鉴科技宣布已经完成面向自动驾驶/高级辅助驾驶领域的技术整合及商业布局,实现了方案落地及订单转化,其推出的正是基于赛灵思FPGA的车载深度学习处理器平台DPhiAutoTM。

而在今年初的CES展上,另一家ADAS初创公司MINIEYE发布了基于赛灵思FPGA的前装产品X1,目前已经进入多家车厂、Tier1的供应商体系,今年将于量产车型上搭载。

MINIEYE表示,选用FPGA芯片是因为其具有高计算性能,更适合深度学习;同时也是车规级已量产的芯片,研发更加成熟,成本具有竞争力,功耗也能大幅降低。

同时,为了弥补单一FPGA的限制,除了此前推出的集成ARM处理器的车规级级Zynq UltraScale+ MPSoC系列,赛灵思还在近期推出了继FPGA之后另外一种全新的产品类型:ACAP(Adaptive Compute Acceleration Platform,自适应计算加速平台)。

赛灵思表示,它将远远突破FPGA的极限,并将能够与 CPU、GPU 以及FPGA相并列。ACAP 的核心是新一代 FPGA 架构,它结合分布式存储器和硬件可编程的 DSP 模块、一个多核 SoC 以及一个或多个软件可编程而又具备硬件灵活性的计算引擎,并通过片上网络(NoC)实现互连。

当然,现在要对FPGA和ASIC作出什么结论还为时过早,对于各大芯片公司来说,这是一场围绕成本、功耗和性能的硬仗。

-

FPGA

+关注

关注

1600文章

21286浏览量

592883 -

asic

+关注

关注

34文章

1142浏览量

119246

原文标题:FPGA,ASIC之争:一场围绕成本、功耗和性能的硬仗 | GGAI深度

文章出处:【微信号:ilove-ev,微信公众号:高工智能汽车】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

fpga和asic的区别

科普 | 一文了解FPGA技术知识

为你的AI芯片从FPGA走向ASIC?

FPGA和ASIC的优劣势 FPGA和ASIC的应用场景及前景

FPGA和ASIC的区别与联系

FPGA和ASIC的概念、基本组成及其应用场景 FPGA与ASIC的比较

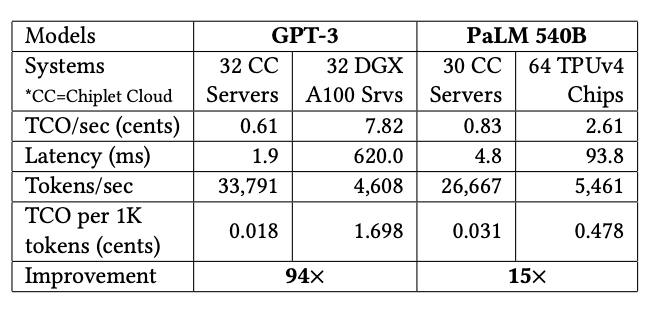

用Chiplet解决ASIC在LLM上的成本问题

FPGA与ASIC在打一场围绕成本、功耗和性能的硬仗

FPGA与ASIC在打一场围绕成本、功耗和性能的硬仗

评论