一、差分平衡参数测试的应用背景

随着信息产业的高速发展,对网络带宽的需求越来越高,就需要信息设备(如大型服务器、超级计算机和交换机等)能够承载的数据速率越来越快。目前,信息设备中均采用差分平衡方式进行高速数据的传输,信息设备生产商对这类高速互连通道的信号完整性问题也愈发重视,差分平衡参数是其中一个重要测试项。

二、差分平衡参数测试原理

1、平衡器件的定义

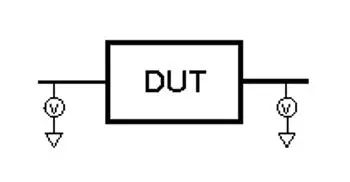

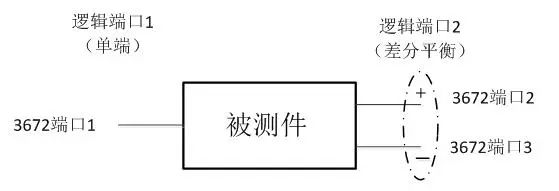

传统的射频微波器件是单端的,即单输入单输出,且输入输出接口上的信号有共同的参考地平面,如图1所示。

图1 单端器件

但随着先进的MMIC集成电路的出现,越来越多的射频电路开始使用差分平衡形式来设计。计算机、服务器中背板的差分平衡时钟速率已到达上百吉比特每秒,速率如此之高也必须按照射频和微波器件来考虑。

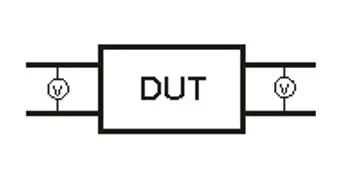

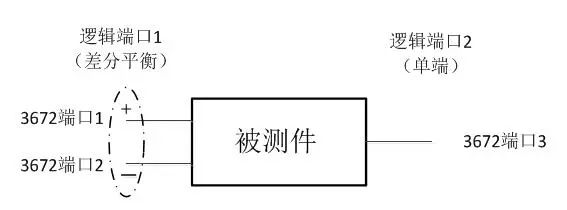

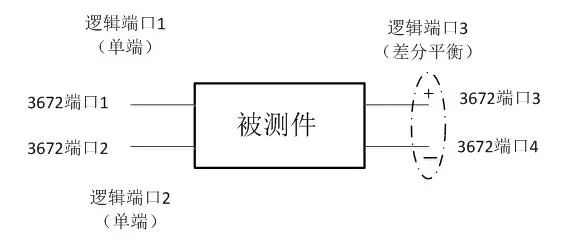

图2 平衡器件

平衡器件的输入或输出都是两端口的。平衡器件所传输的信号是两个端口之间电平的差值或平均值,输入的两端口或输出的两个端口之间互为参考,而不是以地为参考,如图2所示。

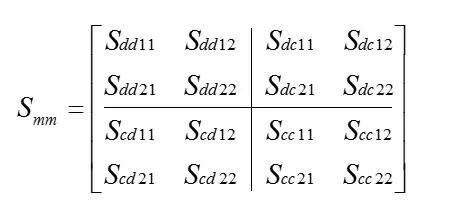

理想情况下,当差分平衡器件的输入端加上幅度相等、相位相差180度的差模信号时,输出端得到的也是差模信号,这种工作模式称为“差模/差模”模式。理想差分传输线不会传输幅度相等相位相同的信号,即共模信号,对共模干扰有很好的抑制作用。实际上差分传输线输入和输出的信号都不可能是理想的,输入和输出信号中都有以地为参考的共模信号存在。由差模信号激励得到共模信号的工作模式称为“差模/共模”模式。如果输入信号中含有共模信号,同样也会激励得到差模和共模信号,对应的工作模式分别为“共模/差模”和“共模/共模”模式。其中“共模/差模”模式会在输出的差模信号中引入噪声,于是差分传输线抑制由共模信号激励产生差模信号的能力将是判断一个该器件性能优劣的重要指标。传统的S参数并不能区分差模信号和共模信号,更不能反映差分传输线各模式的传输和不同模式的转化特性,因此无法准确衡量一个差分平衡器件的性能。为完整表征一个差分平衡器件的特性,需要知道它在差模和共模激励下的响应,以及在这两种激励下的模式转换信息,以4端口的平衡参数为例,混合模S参数矩阵可以完整表征其特性指标。

其中,混合模S参数用Sabxy的形式表示,前面两个下标分别表示响应和激励信号的模式,d代表差模信号,c代表共模信号,后两位数字下标分别表示响应和激励的端口。矩阵的左上象限表示传输线在差模激励下的差模响应,右下象限表示传输线在共模激励下的共模响应;矩阵的左下象限表示传输线在差模激励下的共模响应,右上象限表示传输线在共模激励下的差模响应,这两个象限描述了差分传输线的模式转换信息。

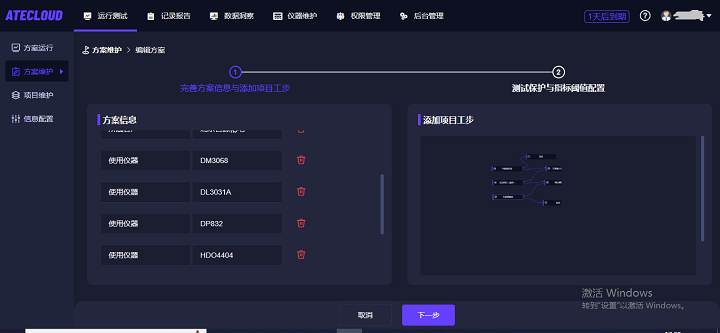

2、3672差分平衡参数设置

任何差分平衡参数测试,首先需要创建相应的混合模S参数的轨迹。

1) 设置轨迹运算的方法

菜单路径:[轨迹]→[新建轨迹]→[平衡参数],显示新建轨迹对话框。

2) 平衡器件拓扑设置方法

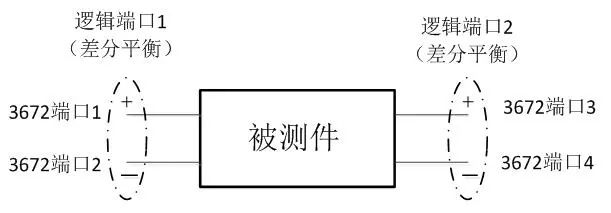

路径: [新建轨迹]对话框→[改变]按钮,显示被测件配置对话框;逻辑端口是用来描述矢量网络分析仪物理测试端口新的平衡测试中的映射关系,具体如下。

1)任意两个物理测试端口可以被映射成一个平衡逻辑端口;

2)任意一个物理测试端口可以被映射成一个单端逻辑端口

图3 平衡参数拓扑设置对话框

四端口矢量网络分析仪支持四种平衡器件拓扑形式,可在图所示对话框进行设置,具体如下:

1)平衡/平衡(2个平衡逻辑端口和四个物理端口)

2)单端/平衡(2个逻辑端口和三个物理端口)

3)平衡/单端(2个逻辑端口和三个物理端口)

4)单端-单端/平衡(3个逻辑端口和三个物理端口)

三 、差分平衡参数测量示例

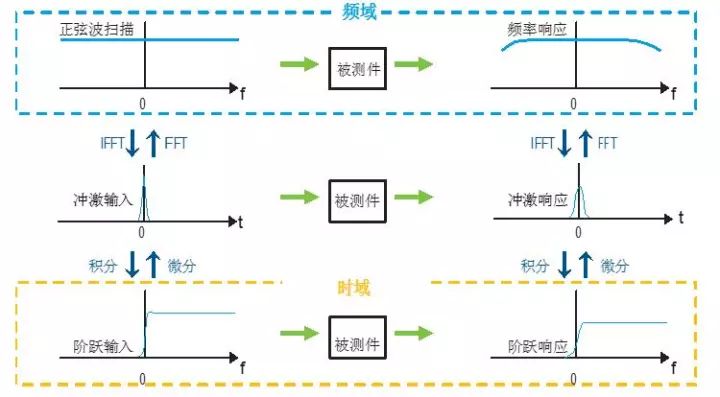

1、TDR差分阻抗测试方法

传统上,TDR差分阻抗测试是一种通过使用时域反射计 (TDR) 示波器来评估传输线路的常见方法。而基于矢量网络分析仪 (VNA) 的 TDR 测量作为一种这种时域分析的替代方法,越来越受到人们的关注。两种方法的测试原理如下图所示。

基于采样示波器的时域反射计(TDR)测试方法噪声相对较大,同时实现高动态范围和快速测量具有一定难度,虽然通过取平均法可以降低噪声,但是这会影响测量速度。示波器上用于测量时序偏差的多个信号源之间的抖动,也会导致测量误差。此外,给TDR示波器设计静电放电(ESD)保护电路非常困难,因此TDR示波器容易被ESD损坏。这些都可以通过基于VNA的TDR测试方案得以避免。

2、测试步骤

步骤1: 复位3672矢量网络分析仪,进入下图界面。

步骤2:设置所需要的起始和终止频率。

步骤3:点击右侧时域按钮,进入时域设置状态。

步骤4:点击时域变换按钮,弹出时域变换对话框后,在变换模式中选择低通阶跃,然后选中时域变换。

图4 时域变换设置

步骤5:接上一步,将时域变换勾除掉。

图5 去掉时域变换

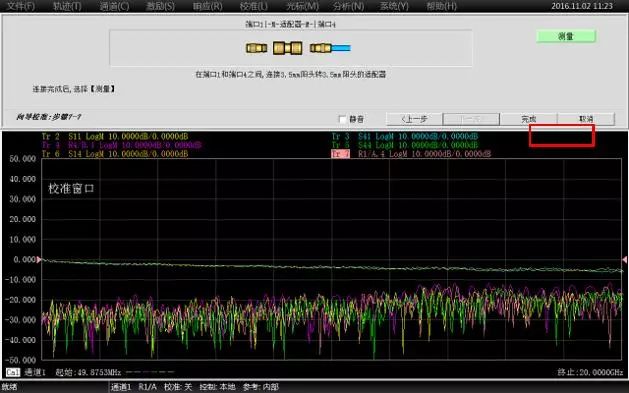

步骤6:进行全四端口校准。

首先根据校准件和被测件选择校准方式和连接方式;接着进行校准件和被测件选择;随后按照向导步骤进行四端口校准,最后点击完成。

图6 全四端口校准

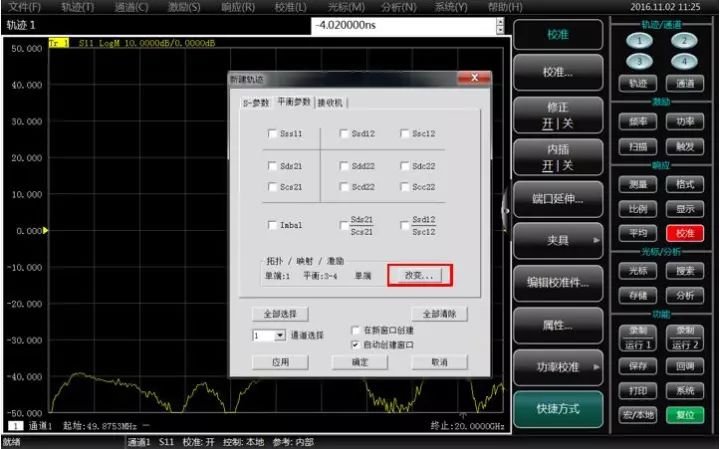

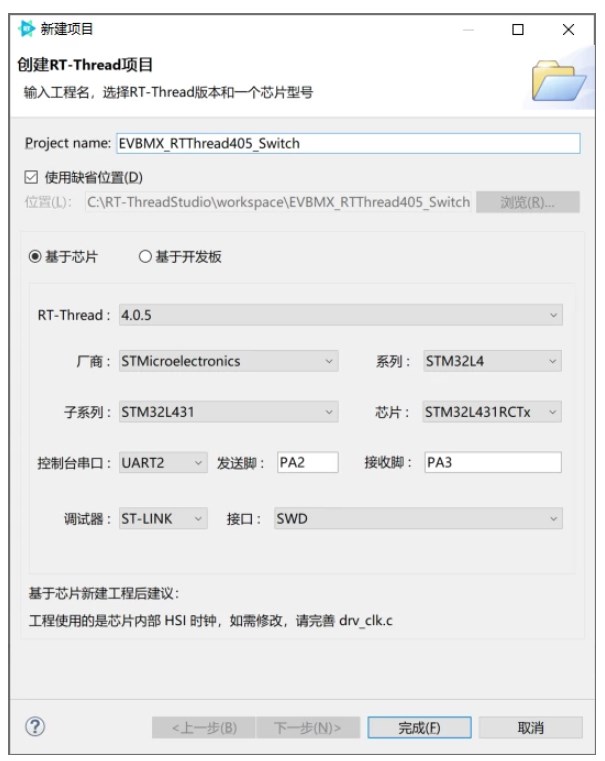

步骤7:点击新建轨迹,建立差分测试轨迹Sdd11。

图7 新建差分测试轨迹

步骤8:在平衡参数页,点击改变按钮进行平衡拓扑设置。

图8 平衡拓扑设置

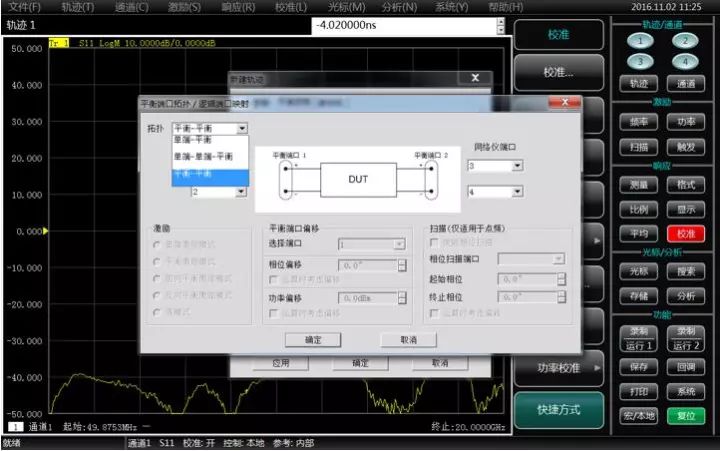

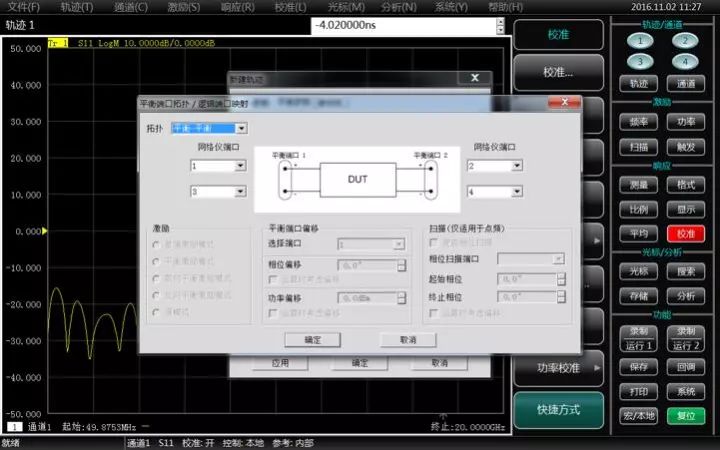

步骤9:修改平衡拓扑设置,选择平衡到平衡。

图9 平衡拓扑设置对话框

步骤10:根据被测件连接情况设置平衡端口和网络仪端口的关系,如下两个图。

图10 端口映射设置

图11 实际的物理连接关系

步骤11:选择轨迹Sdd11,点击确定。

图12 测试轨迹选择

步骤12:选择阻抗格式。

图13 选择阻抗格式

步骤13:【分析】→【时域】→【时域变换】→[低通阶跃],并勾选时域变换,同时根据被测件长度设置起始和终止时间。

图14 时域变换设置

步骤14:设置光标等观察阻抗曲线。

图15 观察曲线的设置

附录 1

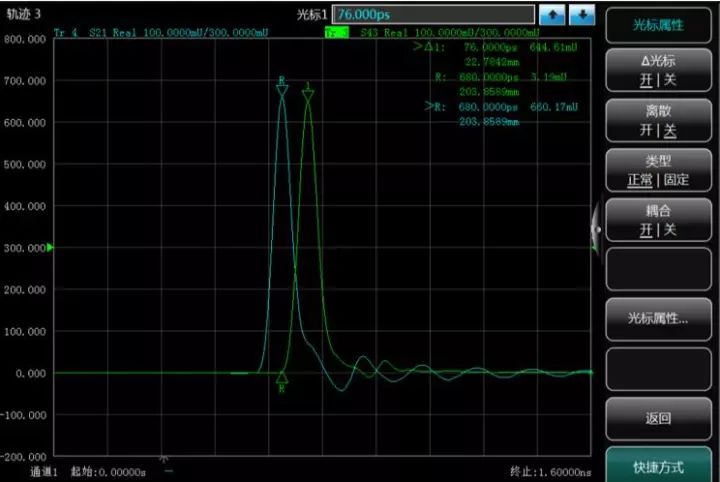

采用3672的时域功能+差分参数测试功能+Delta光标计算功能还能得到对内延时(Intra-pair skew)和对间延时(Inter-pair skew)。

测试连接

对内延时(Intra-pair skew)

对间延时(Inter-pair skew)

-

MMIC

+关注

关注

3文章

411浏览量

24145 -

网络带宽

+关注

关注

0文章

33浏览量

8076 -

射频微波器件

+关注

关注

0文章

8浏览量

6854

原文标题:差分线及巴伦变压器用网分怎么测?AV3672告诉你

文章出处:【微信号:eda365wx,微信公众号:EDA365电子论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

永磁同步电机全速域矢量控制的全过程介绍

IGBT动态测试参数有哪些?

RT-Thread启动进入就绪态最高优先级线程的全过程与栈帧分析(上)

芯片电学测试是什么?都有哪些测试参数?

IC测试的分类介绍

原位拉曼系统--实时监测半导体薄膜生长全过程

差分平衡参数测试的介绍和原理以及测试全过程图片详解

差分平衡参数测试的介绍和原理以及测试全过程图片详解

评论