声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

凌力尔特

+关注

关注

19文章

506浏览量

117178 -

adc

+关注

关注

95文章

5646浏览量

539410 -

分辨率

+关注

关注

2文章

989浏览量

41558 -

LTM9001

+关注

关注

0文章

1浏览量

1508

发布评论请先 登录

相关推荐

关于LTM4644使用12V和3.3V混合输入源的应用问题

当前我的应用场景是,PCB设计面积较小,可用的输入源为12V/1A 和 3.3V/3A两种。想要实现三种输出:

①12V→3.8V/1.1A;②12V→2.4V/1.85A;③3.3V→1.3V

发表于 01-05 07:27

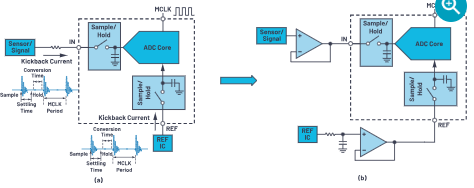

高速ADC模拟输入架构类型介绍

低Q电感或铁氧体磁珠)

图6中,通过在模拟输入的每一侧串联一个低Q电感或铁氧体磁珠,实现了输入匹配。这是降低进入模拟输入端的噪声量的一种方法

发表于 12-18 07:42

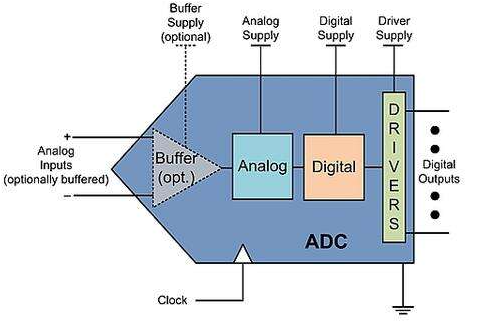

ADI-高速差分ADC驱动器设计指南

作为应用工程师,我们经常遇到各种有关差分输入型高速模数转换器(ADC)的驱动问题。事实上,选择正确的ADC驱动器和配置极具挑战性。为了使鲁棒性ADC

发表于 11-27 08:31

•2次下载

在高速ADC中增加SFDR的主要限制是什么?

同时也面临一些挑战。其中最有意义的是如何提高高速ADC的SFDR,这可以提高信号的精度和准确性。 SFDR即“串扰自由动态范围”,代表着ADC在高频输入信号下输出第一个谐波之后的最高谐

什么是阻抗匹配?高速PCB设计为什么要控制阻抗匹配?

非常重要,因为在高速数字和模拟电路中,信号频率通常在数兆赫或甚至更高的范围内运行。如果信号阻抗不匹配,就会导致信号反射、串扰、噪声等问题,从而影响信号稳定性和可靠性。 阻抗匹配的定义是在不同电路元件之间

什么是ISO 9001?

ISO 9001是Perforce静态代码分析器Helix QAC 和 Klocwork 的开发和维护的核心。我们的质量管理体系已通过LRQA的ISO 9001认证。

IISO 9001有助于

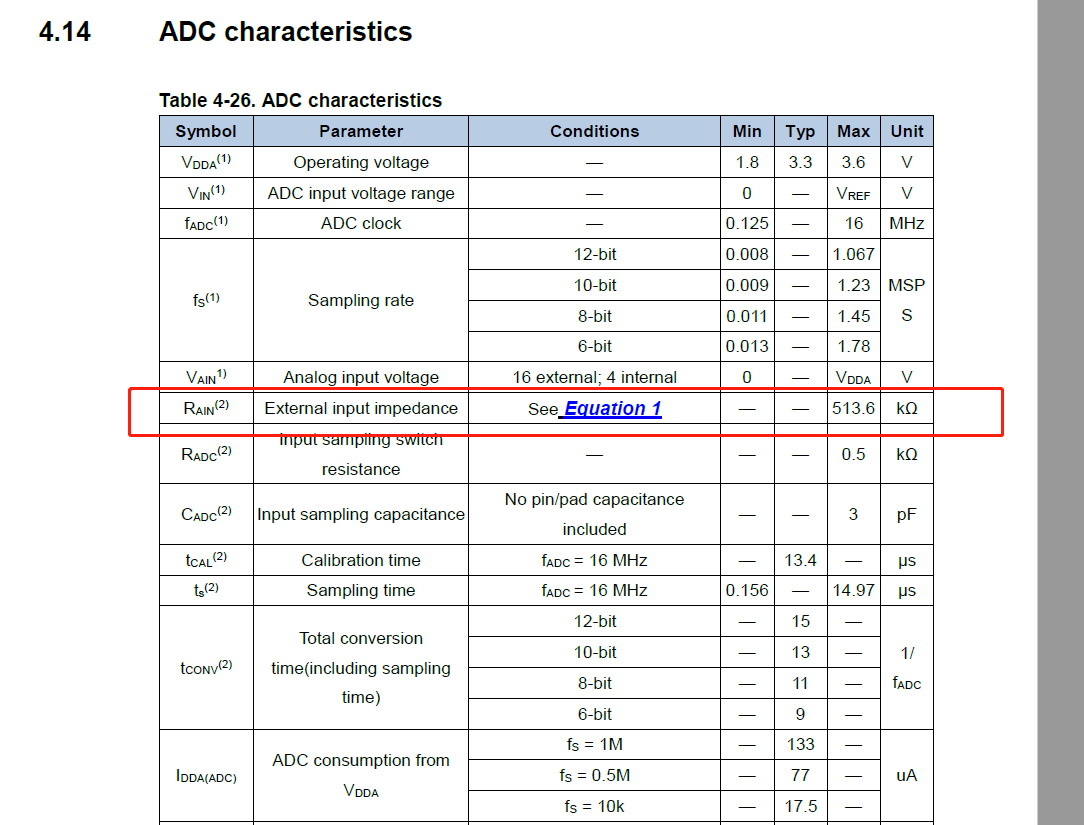

CTSD精密ADC:轻松驱动ADC输入和基准电压源,简化信号链设计

本文重点介绍新型连续时间Sigma-Delta (CTSD)精密ADC最重要的架构特性之一:轻松驱动阻性输入和基准电压源。实现最佳信号链性能的关键是确保其与ADC接口时

【小眼睛科技紫光盘古50K开发板试用体验】+高速ADC模块硬件连接

ADC,这样存在的问题就是时钟抖动很大,无法充分实现ADC高速200M采集性能。

ADI提供的手册中有如下的图:

10.3M是的单信号输入

发表于 05-26 15:22

高频高速PCB设计中的阻抗匹配,你了解多少?

挑战。

在高速PCB设计中,阻抗匹配显得尤为重要,为减少在高速信号传输过程中的反射现象,必须在信号源、接收端以及传输线上保持阻抗的匹配。

一般而言,单端信号线的阻抗取决于它的线宽以及与

发表于 05-26 11:30

用 LTM9001 实现与高速 ADC 输入匹配

用 LTM9001 实现与高速 ADC 输入匹配

评论