作者:德州仪器 Emrys Maier, Tim Claycomb

摘要

大多数德州仪器(TI)超小外形无引脚(X2SON)器件的电路板布局和钢网信息均在其数据表中提供。本文档帮助印刷电路板(PCB)设计人员理解并更好地使用这些信息来优化设计。

由于采用X2SON的小封装尺寸,使用X2SON封装让用户能够压缩PCB布局并实现极小空间的设计。在使用这种节省空间的封装时,了解一些关键的PCB制造与组装限制可以降低最终产品的复杂性。本应用报告将讨论制造和组装包含X2SON封装的PCB时的一些限制。有三个主要因素影响制造印制电路板(PCB)的封装尺寸和间距。它们是:PCB制造、焊料应用和元件布局。

引言

大多数德州仪器(TI)超小外形无引脚(X2SON)器件的电路板布局和钢网信息均在其数据表中提供。本文档帮助印刷电路板(PCB)设计人员理解并更好地使用这些信息来优化设计。

由于采用X2SON的小封装尺寸,使用X2SON封装让用户能够压缩PCB布局并实现极小空间的设计。在使用这种节省空间的封装时,了解一些关键的PCB制造和组装限制可以降低最终产品的复杂性。本应用报告将讨论制造和组装包含X2SON封装的PCB时的一些限制。有三个主要因素影响制造印制电路板(PCB)的封装尺寸和间距。它们是:PCB制造、焊料应用和元件布局。

2 PCB制造

PCB的设计必须符合PCB制造商的制造规格。PCB的可制造性取决于所需的间隙规格。更紧密的间隙规格会导致复杂性增加,限制可用制造商的数量。

大多数成熟的印刷电路板制造商可以生产间距和布线为0.1 mm(〜4 mil)的铜层,并可钻出小至0.1 mm(〜4 mil)的孔。X2SON系列封装的基础PCB尺寸仅需0.208 mm(8.2 mil)间距——这完全在制造范围内。

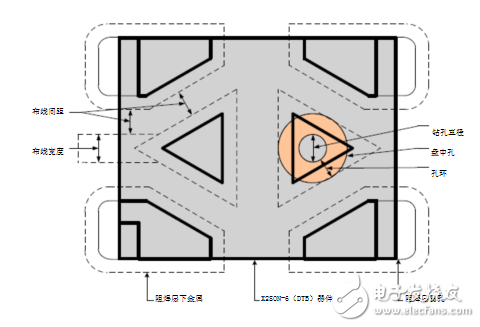

用这些封装制造的主要问题来自用于连接中心引脚的方法。PCB的可制造性将受到四个主要间隙规格的影响:布线间距、布线宽度、钻孔直径和孔环直径。图3可视化呈现了每个规格。

图3.间隙规格

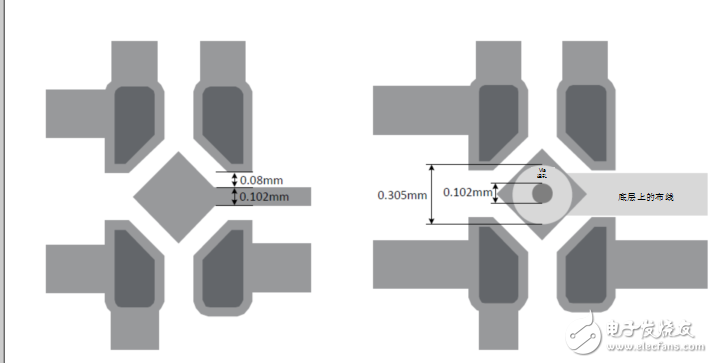

图4显示了连接中心引脚的第一个选项。此选项用于X2SON-5(DPW)封装的同一层的两个引脚之间进行布线。这将引入布线间距和布线宽度限制。角焊盘之间的最大间距为0.26 mm(10.2 mil),并假设在不增加复杂性的情况下允许制造的最小布线宽度为0.1 mm(〜4 mil),布线最小间距为0.08 mm(3.15 mil)。布线间距要求小于0.1 mm(〜4 mil)将增加制造的复杂性,某些PCB制造厂家可能无法制造。在撰写本文时,主要PCB制造商可以实现0.05 mm(〜2 mil)的细节精度。

图5显示了布线到中心引脚的第二个选项。此选项在X2SON-5(DPW)封装焊盘的单独信号层上布线,并使用通孔连接到中心引脚。通过在底层上布线,可以避免在顶层上紧密的布线间距和布线宽度。这种布局方法将导致与钻孔尺寸和孔环相关的其他限制。为了避免增加复杂性和可能的制造问题,钻孔直径必须保持大于0.1 mm(〜4 mil)。此外,通孔直径必须小于0.35 mm(13.78 mil),以便通孔小于中心引脚。这需要0.125 mm(〜5 mil)的最小孔环规格。因为大多数PCB制造厂可轻易实现0.125 mm的孔环规格,此选项提供了最有效的解决方案。

图4.X2SON-5(DPW)封装中心引脚布局选项1 图5.X2SON-5(DPW)封装中心引脚布局选项2

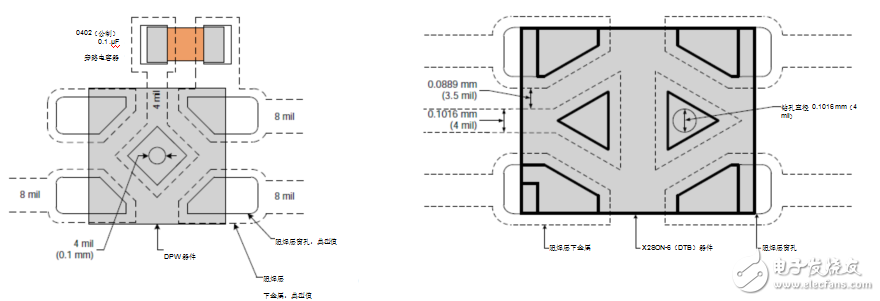

在中心焊盘上设置通孔时,必须考虑钻孔尺寸限制。使用直径为0.1 mm(〜4 mil)或更小的钻孔将通孔直接设置在中心焊盘中。图7显示了一个0.1 mm的通孔,用于在中心焊盘上缩放。请注意,如果使用这种方法,建议在焊接钢网上使用稍大的焊料孔径,因为有些焊料会吸入通孔。即使焊料稍微放置在焊盘外面,只要焊盘不与任何其他焊盘或焊料接触,它就会被拉到焊盘上。

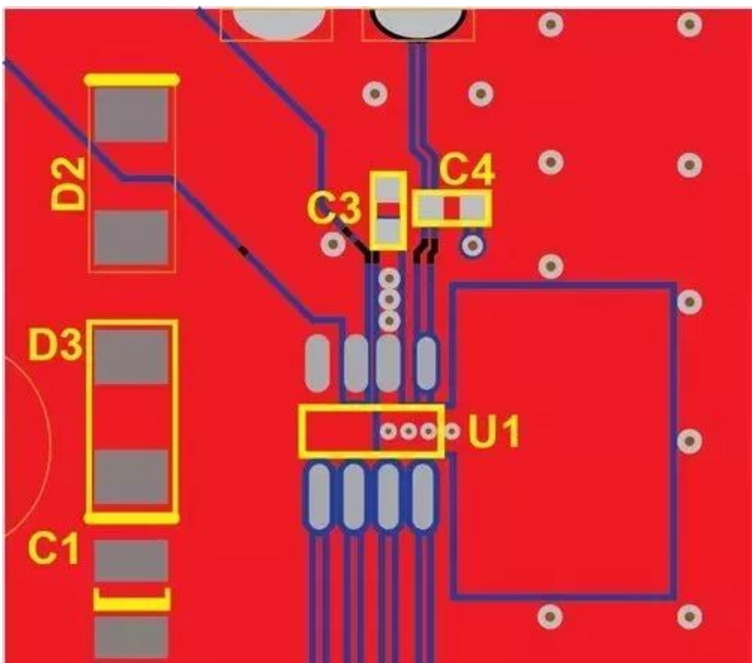

图6和图7显示了覆盖有适当器件的布局示例。请注意,阻焊层窗孔大于外部焊盘,这允许对这些焊盘进行视觉焊接检查。此外,焊盘金属在阻焊层下方延伸,以特别增加焊盘的物理强度。准确的测量值在每个器件数据表的机械制图部分提供。

图 6.X2SON-5(DPW)封装PCB完整的封装示例,显示旁路电容器 图 7.X2SON-6(DTB)封装PCB封装示例,不显示旁路电容器

3 焊锡膏应用

由于涉及的问题很多,焊锡膏应用是微小部件最关注的领域。需要在焊盘上放置正确数量的焊料。焊料量受钢网厚度、焊料类型以及孔径大小和形状的影响。这对于间距小于0.4 mm(15.7 mil)的封装来说变得更加困难。TI的X2SON封装保持了0.4 mm(15.7 mil)的间距,同时减小了整体封装尺寸,从而使得在组装过程中出现更多误差也不会对产量产生显著影响。

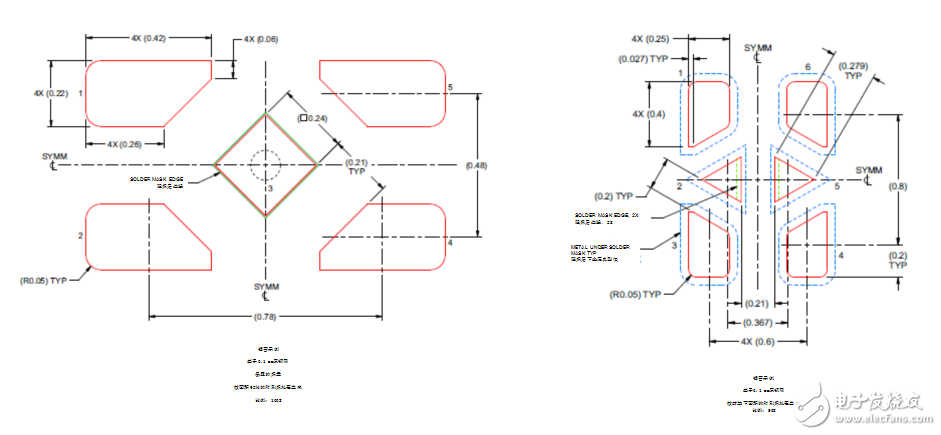

TI建议使用0.1 mm(〜4 mil)厚的焊料钢网,孔径尺寸在焊盘尺寸的92%至100%之间,以进行适当的焊料沉积。当使用盘中孔方法时,这应该增加10%。图8和图9分别展示了TI的X2SON-5(DPW)和X2SON-6(DTB)封装的焊锡膏建议。

焊料钢网孔径尺寸与焊锡膏选择有关。今天,用于SMT焊接的锡膏主要有两种类型:III型和IV型。III型焊锡膏现在已经成为标准,当需要更一致和更精细的颗粒时,使用IV型锡膏。III型锡膏含有直径为25-45μm(0.98-1.77 mil)的颗粒,IV型焊料含有直径为20-38μm(0.79-1.50 mil)的颗粒。典型的经验法则是孔径宽度应该至少是焊球尺寸的5倍。考虑到图8所示的0.24 mm(9.45 mil)孔径,焊锡球直径必须小于0.048 mm(1.89 mil),这意味着可以使用III型焊锡膏。

图8.X2SON-5(DPW)封装焊料钢网示例图9.X2SON-6(DTB)封装焊料钢网示例

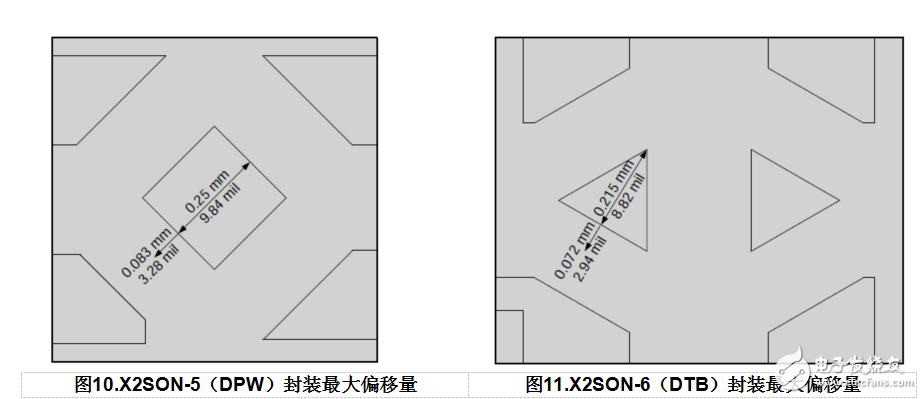

元件布局

贴片机的元件布局通常非常准确,精度约为±30μm。图10和图11显示了X2SON封装的三分之一焊盘布局错误。为了正确安装部件,X2SON-5封装需要±83μm(3.28 mil)或更高的精度,而X2SON-6封装需要±72μm(2.94 mil)的精度。这样可以使所有引脚与焊锡膏良好接触,并防止它们与焊盘对齐超过三分之一。在焊接过程中,来自熔化焊料的表面张力将使部件对齐。由于很多贴片机都比所需的精度值要好,所以这个问题不应成为主要PCB组装公司的问题。

图10.X2SON-5(DPW)封装最大偏移量图11.X2SON-6(DTB)封装最大偏移量

-

pcb

+关注

关注

4219文章

22466浏览量

385645 -

ti

+关注

关注

111文章

8257浏览量

210920 -

封装

+关注

关注

123文章

7264浏览量

141077

发布评论请先 登录

相关推荐

典型封装的电机驱动器 IC,PCB如何布局?

基于X2SON封装的PCB布局限制

基于X2SON封装的PCB布局限制

评论