据外媒报道,今天,沉寂已久的计算技术界迎来了一个大新闻。劳伦斯伯克利国家实验室的一个团队打破了物理极限,将现有最精尖的晶体管制程从14nm缩减到了1nm。晶体管的制程大小一直是计算技术进步的硬指标。晶体管越小,同样体积的芯片上就能集成更多,这样一来处理器的性能和功耗都能会获得巨大进步。

多年以来,技术的发展都在遵循摩尔定律,即当价格不变时,集成电路上可容纳的元器件的数目,约每隔18-24个月便会增加一倍,性能也将提升一倍。换言之,每一美元所能买到的电脑性能,将每隔18-24个月翻一倍以上。眼下,我们使用的主流芯片制程为14nm,而明年,整个业界就将开始向10nm制程发展。

不过放眼未来,摩尔定律开始有些失灵了,因为从芯片的制造来看,7nm就是物理极限。一旦晶体管大小低于这一数字,它们在物理形态上就会非常集中,以至于产生量子隧穿效应,为芯片制造带来巨大挑战。因此,业界普遍认为,想解决这一问题就必须突破现有的逻辑门电路设计,让电子能持续在各个逻辑门之间穿梭。

此前,英特尔等芯片巨头表示它们将寻找能替代硅的新原料来制作7nm晶体管,现在劳伦斯伯克利国家实验室走在了前面,它们的1nm晶体管由纳米碳管和二硫化钼(MoS2)制作而成。MoS2将担起原本半导体的职责,而纳米碳管则负责控制逻辑门中电子的流向。

眼下,这一研究还停留在初级阶段,毕竟在14nm的制程下,一个模具上就有超过10亿个晶体管,而要将晶体管缩小到1nm,大规模量产的困难有些过于巨大。

不过,这一研究依然具有非常重要的指导意义,新材料的发现未来将大大提升电脑的计算能力。

据白宫官网报道,美国东部时间22日,2015年美国最高科技奖获奖名单公布,包括9名国家科学奖获得者(National Medal of Science)和8名国家技术和创新奖(National Medal of Technology and Innovation)获得者。其中美籍华人科学家胡正明荣获年度国家技术和创新奖。

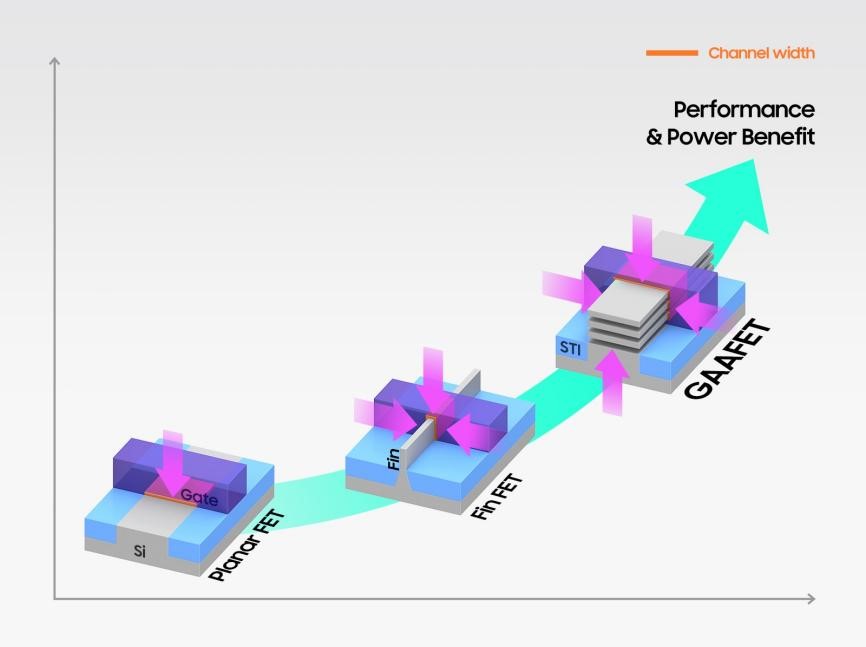

胡正明教授是鳍式场效晶体管(FinFET)的发明者,如今三星、台积电能做到14nm/16nm都依赖这项技术。他1947年出生于北京豆芽菜胡同,在***长大,后来考入加州大学伯克利分校。

在华为海思麒麟950的发布会上,胡正明教授曾现身VCR,据他介绍,FinFET的两个突破,一是把晶体做薄后解决了漏电问题,二是向上发展,晶片内构从水平变成垂直。

胡认为,FinFET的真正影响是打破了原来英特尔对全世界宣布的将来半导体的限制,这项技术现在仍看不到极限。

2010年后,Bulk CMOS工艺技术在20nm走到尽头,胡教授的FinFET和FD-SOI工艺发明得以使摩尔定律在今天延续传奇。

-

集成电路

+关注

关注

5320文章

10725浏览量

353329 -

英特尔

+关注

关注

60文章

9413浏览量

168787 -

晶体管

+关注

关注

76文章

9053浏览量

135176

原文标题:1nm晶体管诞生!华人胡正明获美国最高技术奖!

文章出处:【微信号:CSF211ic,微信公众号:中国半导体论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

台积电1nm进展曝光!预计投资超万亿新台币,真有必要吗?

苹果欲优先获取台积电2nm产能,预计2024年安装设备生产

台积电回应1nm制程厂选址传闻:不排除任何可能性

消息称台积电1nm制程厂选址确定

台积电宣布斥资逾万亿新台币,在嘉义科学园区设立1nm制程代工厂

台积电1.4nm制程工艺研发持续,预计2027-2028年量产

全球首颗3nm电脑来了!苹果Mac电脑正式进入3nm时代

2nm芯片什么时候出 2nm芯片手机有哪些

2nm芯片是什么意思 2nm芯片什么时候量产

华为发布首款5nm 5G SoC,集成153亿晶体管

请问NM1200 UART1可以使用吗?

中芯国际下架14nm工艺的原因 中芯国际看好28nm

麻省理工华裔研究出2D晶体管,轻松突破1nm工艺!

麻省理工华裔:2D 晶体管,轻松突破 1nm !

最精尖的晶体管制程从14nm缩减到了1nm

最精尖的晶体管制程从14nm缩减到了1nm

评论