声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Altera

+关注

关注

37文章

771浏览量

153306 -

Cyclone

+关注

关注

0文章

54浏览量

29965

发布评论请先 登录

相关推荐

【干活分享】Cyclone V FPGA技术精选十问十答

是?A6.Quartus II v12.0 SP1Q7.Cyclone V Memory Controller的特性都有哪些?A7.1)最高支持400MHz硬核DDR3接口;2)最高支持300MHz软核DDR3接口;

发表于 12-04 16:11

如何提高DDR3的效率

现在因为项目需要,要用DDR3来实现一个4入4出的vedio frame buffer。因为片子使用的是lattice的,参考设计什么的非常少。需要自己调用DDR3控制器来实现这个vedio

发表于 08-27 14:47

cyclone V控制DDR3的读写,quartusII配置DDR3 ip核后,如何调用实现DDR3的读写呢,谢谢

DDR3的IP核配置完毕后,产生了好多文件,请问如何调用这些文件实现DDR3的读写呢?看了一些文章,说是要等到local_init_done为高电平后,才能进行读写操作。请问DDR3的控制命令如

发表于 01-14 18:15

Xilinx DDR3 资料

Achieving High Performance DDR3 Data Rates in Virtex-7 and Kintex-7 FPGAs。Xilinx官方DDR3资料。

发表于 05-27 16:39

DDR3的CS信号接地问题

CPU的DDR3总线只连了一片DDR3,也没有复用总线将DDR3的CS直接拉到地的话,DDR3初始化不成功所以说DDR3的CS信号是通过沿采

发表于 11-25 09:41

665x的DDR3配置

命令时,DDRA[10]会被拉高,以确保所以的bank处于不活化状态(Deactivation)。2.3.5. 读命令图2所示为DDR3内存控制器从DDR3 SDRAM中执行一个读操作。读命令初始化一个

发表于 01-18 22:04

FPGA输出的DDR3差分时钟左右抖动很厉害,请问是怎么回事呢?

各位专家,我使用altera的cyclone5的DDR3硬核控制器,输入时钟是国产的125兆50PPM有源晶振,现在调试时发现对DDR3的读写偶尔出错。我们测试DDR3接口的差分时钟,

发表于 05-11 06:50

DDR3 SDRAM的简单代码如何编写

嗨,我是FPGA领域的新手。现在我正在使用Genesys2。我必须控制DDR3内存。我在Digilent网站上找到了一些使用micrlaze处理器的DDR3示例。但是,在我的情况下,我不必

发表于 05-05 15:29

Gowin DDR3参考设计

本次发布 Gowin DDR3参考设计。Gowin DDR3 参考设计可在高云官网下载,参考设计可用于仿真,实例化加插用户设计后的总综合,总布局布线。

发表于 10-08 08:00

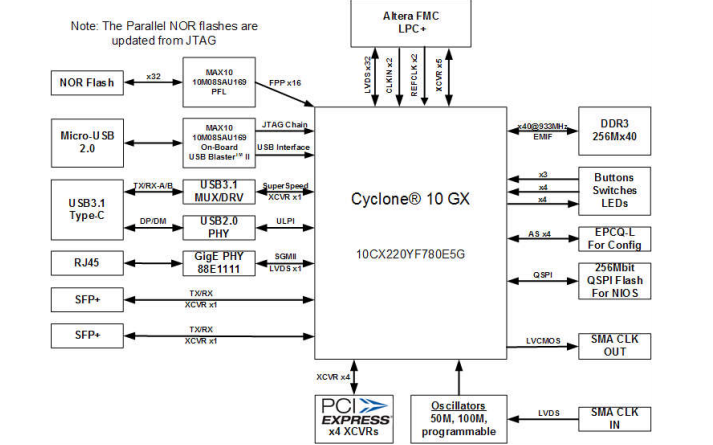

简述 Cyclone 10 GX DDR3 设计的步骤

简述 Cyclone 10 GX DDR3 设计的步骤

评论