声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

LabVIEW

+关注

关注

1918文章

3619浏览量

316962 -

NI

+关注

关注

19文章

1117浏览量

99511 -

程序

+关注

关注

114文章

3630浏览量

79525 -

状态机

+关注

关注

2文章

486浏览量

27161

发布评论请先 登录

相关推荐

Verilog状态机+设计实例

在verilog中状态机的一种很常用的逻辑结构,学习和理解状态机的运行规律能够帮助我们更好地书写代码,同时作为一种思想方法,在别的代码设计中也会有所帮助。 一、简介 在使用过程中我们常说

基于队列的灵活状态机——WTYKAMC@2023框架

本帖最后由 yk74110 于 2024-4-18 16:48 编辑

WTYKAMC@2023框架

【简介】

这是一个基于队列的灵活状态机,可以满足队列元素先进先出,先进后出,后进后出

发表于 11-03 16:11

嵌入式软件设计之状态机编程开发方案

那么状态机的引入解决了哪些问题呢?

当程序有多个状态时,规范了程序的状态转换,避免了一些引入一些复杂的判断逻辑。

规范了

发表于 10-27 12:33

•279次阅读

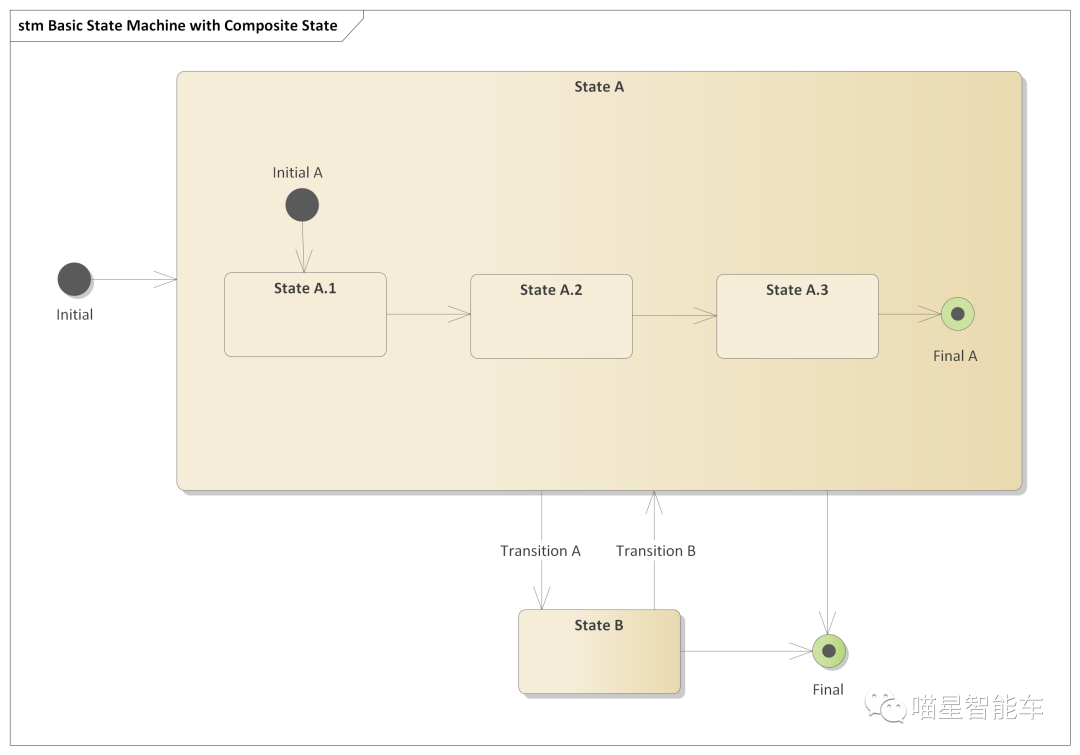

什么是状态机?状态机的种类与实现

状态机,又称有限状态机(Finite State Machine,FSM)或米利状态机(Mealy Machine),是一种描述系统状态变化的模型。在芯片设计中,

如何生成状态机框架

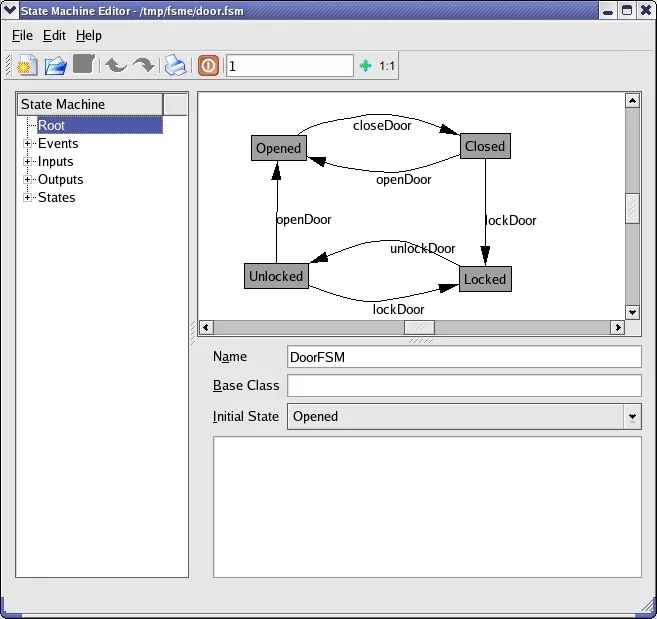

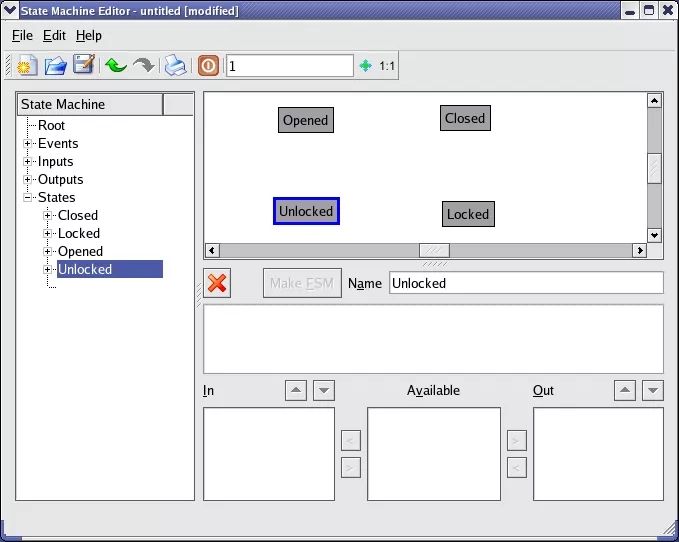

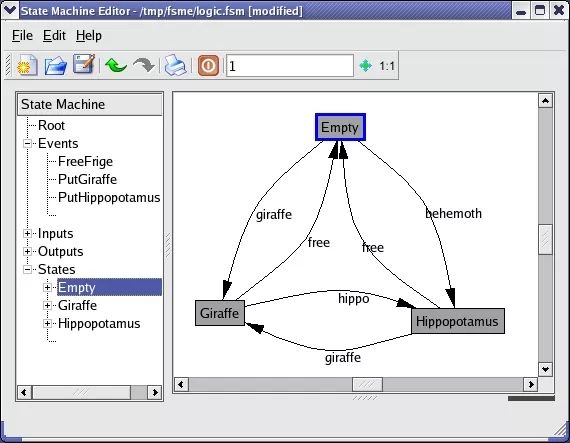

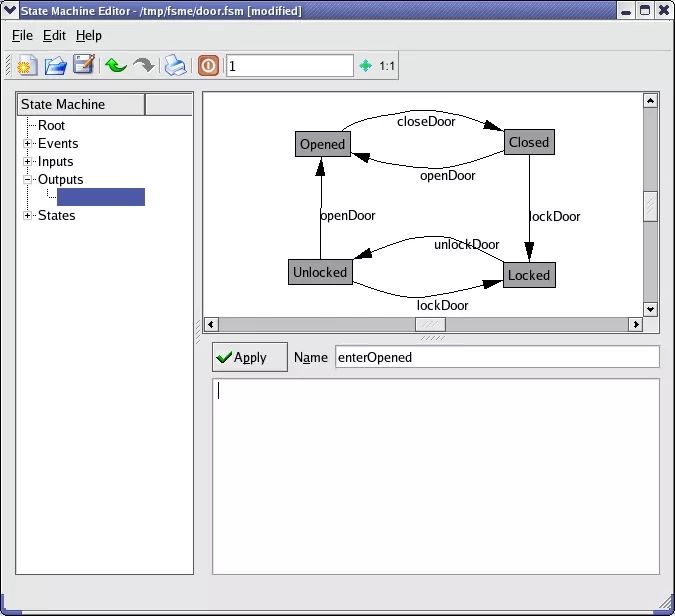

生成状态机框架 使用FSME不仅能够进行可视化的状态机建模,更重要的是它还可以根据得到的模型自动生成用C++或者Python实现的状态机框架。首先在FSME界面左边的树形列表中选择"R

自动生成程序状态机代码状态机建模方法

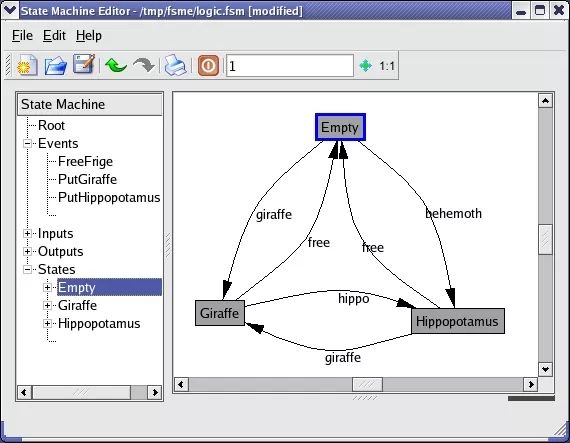

首先运行fsme命令来启动状态机编辑器,然后单击工具栏上的“New”按钮来创建一个新的状态机。FSME中用于构建状态机的基本元素一共有五种:事件(Event)、输入(Input)、输出(Output

状态机自动生成工具FSME

为实用的软件系统编写状态机并不是一件十分轻松的事情,特别是当状态机本身比较复杂的时候尤其如此,许多有过类似经历的程序员往往将其形容为“毫无创意”的过程,因为他们需要将大量的时间与精力倾注在如何管理

分享一款状态机自动生成工具

为实用的软件系统编写状态机并不是一件十分轻松的事情,特别是当状态机本身比较复杂的时候尤其如此,许多有过类似经历的程序员往往将其形容为"毫无创意"的过程,因为他们需要将大量的时间与精力倾注在如何管理好

如何对状态机的程序进行灵活修改

如何对状态机的程序进行灵活修改

评论