声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1600文章

21281浏览量

592866 -

DDR3

+关注

关注

2文章

268浏览量

41770 -

存储器

+关注

关注

38文章

7120浏览量

161925 -

Altera

+关注

关注

37文章

771浏览量

153288

发布评论请先 登录

相关推荐

基于FPGA的DDR3 SDRAM控制器的设计与优化

[2-4]。DDR SDRAM是同步动态随机存储器,其采用双倍速率存取,数据在工作时钟的上升沿和下降沿采样,有效提升了存储速率。DDR SD

发表于 08-02 09:34

基于FPGA的DDR3多端口读写存储管理的设计与实现

作者:吴连慧,周建江,夏伟杰摘要:为了解决视频图形显示系统中多个端口访问DDR3的数据存储冲突,设计并实现了基于FPGA的DDR3

发表于 08-02 11:23

基于FPGA的DDR3用户接口设计

互联设计[6]。因此,在FPGA中使用DDR3进行大容量数据的存储是一种趋势。本文基于Xilinx 公司的Virtex-6芯片,针对高速实时

发表于 08-30 09:59

DDR3存储器接口控制器IP助力数据处理应用

了设计的一大挑战。FPGA可通过在单个FPGA中实现多个视频处理器来提供强大的处理能力。那么现在的挑战就变成了要使数据尽快且高效地从FPGA

发表于 05-24 05:00

基于DDR3存储器的数据处理应用

了设计的一大挑战。FPGA可通过在单个FPGA中实现多个视频处理器来提供强大的处理能力。那么现在的挑战就变成了要使数据尽快且高效地从FPGA

发表于 05-27 05:00

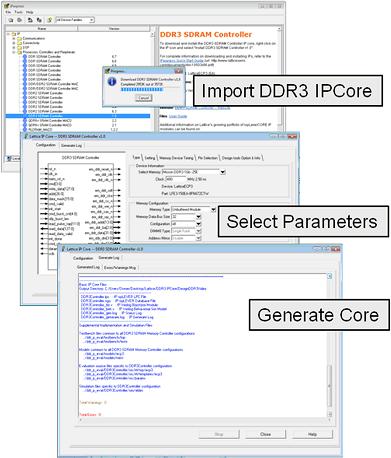

如何用中档FPGA实现高速DDR3存储器控制器?

的工作时钟频率。然而,设计至DDR3的接口也变得更具挑战性。在FPGA中实现高速、高效率的DDR3控制器是一项艰巨的任务。直到最近,只有少数高端(昂贵)的

发表于 08-09 07:42

与Kintex 7的DDR3内存接口

& 14用于DDR3内存接口,但由于我使用的是3.3V的fash存储器IC,我必须使用bank 14进行闪存存储器接口。原因是需要的资源仅在Bank 14中可用.

发表于 04-17 07:54

用中档FPGA实现高速DDR3存储器控制器

用中档FPGA实现高速DDR3存储器控制器

引言

由于系统带宽不断的增加,因此针对更高的速度和性能,设计人员对存储技术进行了优化

发表于 01-27 11:25

•899次阅读

DDR3存储器接口控制器IP核在视频数据处理中的应用

DDR3存储器系统可以大大提升各种数据处理应用的性能。然而,和过去几代(DDR和DDR2)器件相比,D

发表于 07-16 10:46

•1738次阅读

基于FPGA的DDR3多端口读写存储管理的设计与实现

为了解决视频图形显示系统中多个端口访问DDR3的数据存储冲突,设计并实现了基于FPGA的DDR3存储

发表于 11-18 18:51

•6490次阅读

Stratix III FPGA的特点及如何实现和高速DDR3存储器的接口

DR3 在高频时数据出现了交错,因此,高速DDR3存储器设计有一定的难度。如果FPGA I/O 结构中没有直接内置调平功能,那么连接DDR3

FPGA如何与DDR3存储器进行正确的数据对接?

FPGA如何与DDR3存储器进行正确的数据对接?

评论