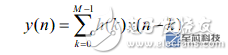

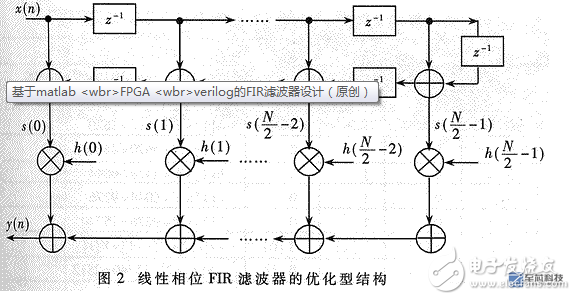

本例程实现8阶滤波器,9个系数,由于系数的对称性,h(0)=h(8),h1(1)=h(7),h(2)=h(6),h(3)=h(5),h(4)为中间单独一个系数。根据公式:

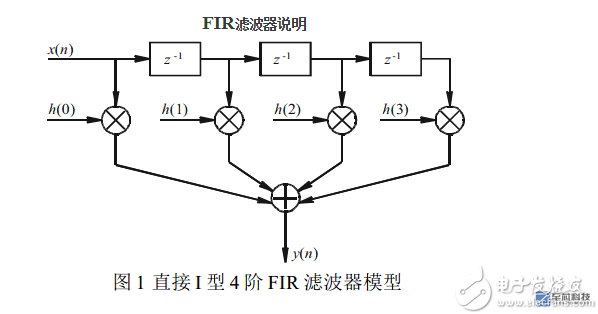

实现框图:

推导出当系数N为偶数时,例如N=4:y(n)=h(0)*{x(0)+x(n-3)}+h(1)*{x(n-1)+x(n-2)}

当系数N为奇数时,例如N=5:

y(n)=h(0)*{x(0)+x(n-1)}+h(1)*{x(n-1)+x(n-3)}+h(2)*x(n-2)

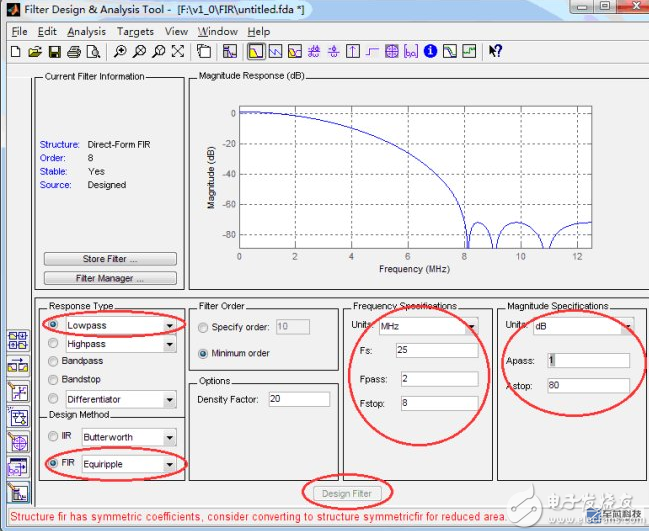

1、用matlab生成和量化滤波器系数

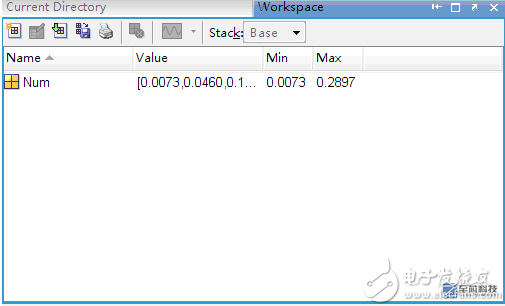

设置参数后,点击“Design Filter”按钮,“file”—“export”,把滤波器系数导出到workspace,如下图:

执行命令:Num=Num’ ,把滤波器系数拷贝到文件COFFICIENT.dat中。

量化系数:在matlab中运行quantization.m

2、说明

用matlab程序sin_1MHz_gen.m生成正弦波波形表,改变变量f0 = 1.5e6可以生成不同频率的波形。把第一个周期的波形数据存入signal_1m.dat文件中,存入的数据个数为Fs/Fo的最小正整数之比的分子,比如Fs=25MHz,Fo=0.3MHz,Fs/Fo=250/3(Fs=25/24MHz),则存入文件signal_1m.dat的波形数据个数为开头的250个数据。相应的signal_gen0.v中的语句if(i0<50)相应的改为if(i0<250)。仿真时signal_1m.dat放在仿真目录下

3、滤波器的multisim仿真

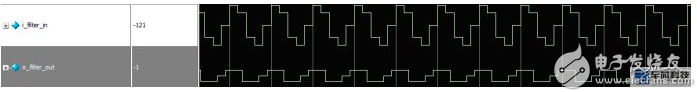

运行matlab,用sin_1MHz_gen.m产生5MHz(f0 =5e6)正弦波信号,Fs/Fo=5,把数据hex_sin_data的前5个数据存入signal_1m.dat文件,相应的signal_gen0.v中的语句if(i0<50)相应的改为if(i0<5)。

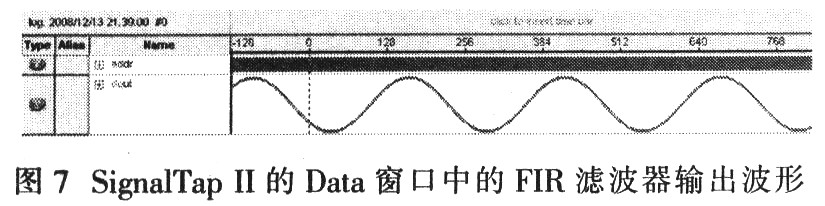

仿真的波形如下图(fir滤波器的输入输出信号):

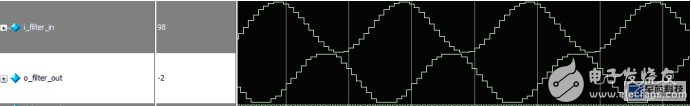

运行matlab,用sin_1MHz_gen.m产生1MHz(f0 =1e6)正弦波信号,Fs/Fo=25,把数据hex_sin_data的前5个数据存入signal_1m.dat文件,相应的signal_gen0.v中的语句if(i0<5)相应的改为if(i0<25)。

仿真的波形如下图(fir滤波器的输入输出信号):

由此可见FIR对带外信号起到衰减的作用。

部分代码:

//Date :2012-5-27

//Description : 8 阶FIR滤波器 ,通带2MH,阻带8MHz ,带外衰减80dB,通带波动1dB

//Uesedfor

//Taobao :

//E-mail :2352517093@qq.com

//==========================================================================

`timescale 1 ns / 1 ns

module fir_filter

(

i_fpga_clk ,

i_rst_n ,

i_filter_in,

o_filter_out

);

input i_fpga_clk ; //25MHz

input i_rst_n ;

input signed [7:0] i_filter_in ; //数据速率25Mh

output reg signed [7:0] o_filter_out; //滤波输出

//==============================================================

//8阶滤波器系数,共9个系数,系数对称

//==============================================================

wire signed[15:0] coeff1 = 16'd239 ;

wire signed[15:0] coeff2 = 16'd1507;

wire signed[15:0] coeff3 = 16'd4397;

wire signed[15:0] coeff4 = 16'd7880;

wire signed[15:0] coeff5 = 16'd9493;

//===============================================================

//延时链

//===============================================================

reg signed [7:0] delay_pipeline1 ;

reg signed [7:0] delay_pipeline2 ;

reg signed [7:0] delay_pipeline3 ;

reg signed [7:0] delay_pipeline4 ;

reg signed [7:0] delay_pipeline5 ;

reg signed [7:0] delay_pipeline6 ;

reg signed [7:0] delay_pipeline7 ;

reg signed [7:0] delay_pipeline8 ;

always@(posedge i_fpga_clk or negedge i_rst_n)

if(!i_rst_n)

begin

delay_pipeline1 <= 8'b0 ;

delay_pipeline2 <= 8'b0 ;

delay_pipeline3 <= 8'b0 ;

delay_pipeline4 <= 8'b0 ;

delay_pipeline5 <= 8'b0 ;

delay_pipeline6 <= 8'b0 ;

delay_pipeline7 <= 8'b0 ;

delay_pipeline8 <= 8'b0 ;

end

else

begin

delay_pipeline1 <= i_filter_in ;

-

FPGA

+关注

关注

1600文章

21281浏览量

592869 -

matlab

+关注

关注

175文章

2917浏览量

228412 -

滤波器

+关注

关注

158文章

7314浏览量

174718

发布评论请先 登录

相关推荐

基于FPGA的FIR滤波器设计与实现

基于FPGA的FIR滤波器IP仿真实例

数字滤波器-IIR滤波器原理介绍&Verilog HDL设计

fir滤波器的设计和实现

基于MATLAB与QUARTUS II的FIR滤波器设计与验

基于MATLAB与QUARTUS II的FIR滤波器设计与验

基于MATLAB及FPGA的FIR低通滤波器的设计

基于MATLAB与FPGA的FIR滤波器设计与仿真

基于matlab FPGA verilog的FIR滤波器设计

基于matlab FPGA verilog的FIR滤波器设计

评论