我们经常在某手机发布会现场听到,“××处理器采用了最先进的10nm工艺制造”,那么究竟这个10nm代表着什么意思呢?纳米制程对于CPU、SoC而言到底多重要?又与晶体管、FinFET以及EUV有什么关系呢 ?一颗CPU诞生过程,其中第七步的紫外线曝光就是最重要的光刻技术,而光刻工艺是集成电路制造过程中最直接体现其工艺先进程度的技术,其中光刻技术的分辨率是指光刻系统所能分辨和加工的最小线条尺寸,决定了CPU中的晶体管最小特征尺寸。

根据ITRS《国际半导体技术蓝图》里面的相关规定,我们平常说说的16nm、14nm、10nm就是用来描述半导体制程工艺的节点代数,而它应在不同半导体元件上,所描述的对象可能有所不一样,比方说在DRAM中,可能是描述在DRAM Cell中两条金属线间最小允许间距Pitch值的一半长度Half-Pitch半节距长度;而用在CPU上时,可能描述的则是CPU晶体管中最小栅极线宽。

总的来说,××nm制程描述了该工艺代下加工尺度的精确度,但它并非指半导体器件中某一具体结构的特征尺寸,而是加工精度的尺寸的最小值。这里我们主要讨论的是关于CPU的制程问题,因为制程对于CPU性能、功耗、发热来说有着比较重要地位,制程的改变对于CPU性能的影响也是非常之大的。之前我们也讲到,14nm通常就是用来描述晶体管的栅极线宽。

为什么要用栅极线宽而不是其他的线宽来表征工艺节点?

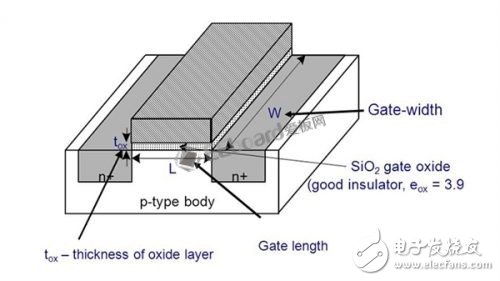

这个主要是涉及到晶体管结构问题,一般来说CPU内部逻辑门电路都是使用MosFET,它有三个电极,栅极(Gate)、源极(Source)、漏极(Drain),其中栅极与源极之间的电压差可以控制从源极流向漏极的电流大小,因此栅极起到了控制作用。

同时诸如晶体管电子迁移率等等特性是完全依赖于掺杂离子以及生产工艺所决定,基本上是不能动,不过其中的晶体管栅极的长宽比还是可以做做文章,电压一样的情况下,栅极宽度越小,电子就有可能通过晶体衬底从负极向正极流动,造成漏电,而漏电问题会带来静态功耗的上升。

因此栅极线宽作用是非常重要,栅极线宽通常都是考量超大规模集成电路设计的最重要参数,也因此以它作为半导体工艺的节点划代,这个是传统意义上工艺制程的规范。

那么意思是制程越小越好咯?

确实是这样,你想,线宽越小,那么单个晶体管的尺寸就越小,那么做出来的CPU die面积就越小啦,同一块晶圆就能生产出更多的CPU die,那么无形中就增加了厂商收入(成片越多)。反过来,你也可以在相同的die面积下集成更多的晶体管,那么CPU性能也会得到提升(当然这不是绝对的)。

其次由于栅极线宽变小了,那么工作电压会相应降低,CPU的功耗也会随之降低,此外在更先进的工艺下,晶体管截止频率上会有更好表现,CPU也自然能工作在更高的频率上。所以我们经常看到某某SoC、CPU说,我们采用了更先进的10nm,功耗下降了××%,频率提升了××%,性能提升了××%。

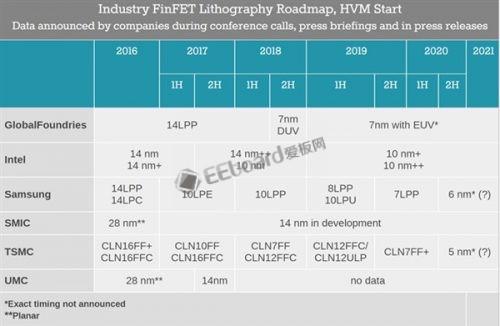

台积电的10nm都量产已久,Intel却还没出货,Intel的无敌工艺不行了?

前几年Intel从22nm进入14nm时代,大家都在说Intel在工艺制程上起码领先于其他家3-5年以上,但是好景不长,大家发现却发现Intel 14nm居然打磨了一遍又一遍,从Skylake(14nm)、Kaby Lake(14nm+)、Coffee Lake(14nm++),历经三代依然在用,据说还会有14nm+++,原本说好的10nm遭遇大量技术问题而难产。

反观对手台积电、三星在代工路上风生水起,16/14nm节点上追赶上了Intel的进度,令人惊讶的是,台积电、三星的10nm工艺量产远远早于Intel,相关产品(例如高通骁龙835)甚至在市场上已经卖了整整一年,台积电甚至在今年量产7nm芯片,这又是怎么回事?

普罗大众都认为10nm肯定比14nm先进,12nm都比14nm好,就在Intel被消极舆论声音即将淹没的时候,Intel点破了纳米制程工艺数字背后“奥秘”,因为台积电、三星的工艺数字都经过不同程度的“美化”,在命名上耍小聪明,也就是“数字”压制,虽然Intel在“数字”上输了,但是从工艺各个层面在一些关键技术参数上来说,Intel其实更胜一筹。之前的14nm就曾经出现过这种情况,××nm制程已经开始脱离原先的范畴,大家开始“造假”。

14nm时代,Intel已经踢爆过一次幕后的秘密

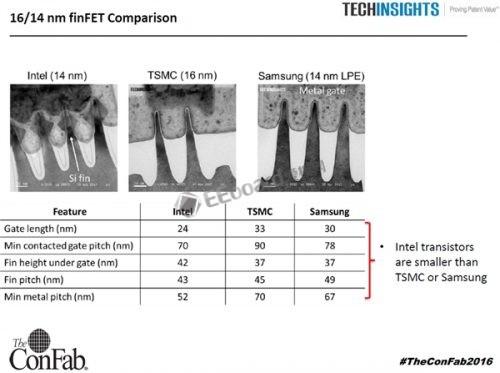

Techinsights也做过对比,Intel 14nm确实优于三星的14nm LPE

Intel表示线宽仅仅代表工艺节点,但要衡量这个工艺的好坏,Gate Pitch栅极间距、Fin Pitc鳍片间距、Fin Pitch最小金属间距、Logic Cell Height逻辑单元高度的参数更具参考意义。同时Intel处理器架构与集成部门主管、高级院士Mark Bohr提出以Transistor Density晶体管密度来衡量半导体工艺水平,并提出了以下公式:

比如在去年9月,Intel举办的Technology and Manufacturing Day上,主动公布出三家10nm工艺相关技术参数指标,我们看到Intel在这些关键性技术指标上都是吊打其余两家,例如Intel的10nm光刻技术制造出来的鳍片、栅极间隔更小(注意Intel公布的是间隔对比,不是线宽,更有比较意义)。因此在晶体管密度上几乎是台积电、三星的两倍,达到了每平方毫米1亿个晶体管,同时保持了逻辑单元高度低的优良传统,在3D堆叠上更有优势。

最近Semiwiki报道了三星的10nm、8nm以及7nm工艺晶体管密度情况,其10/8/7nm工艺的晶体管密度分别是是55.10/64.4/101.23 MTr/mm2。可以看到,三星的7nm工艺在晶体管密度上才追勉强上Intel的10nm,谁在玩小把戏,你不会不知道吧?

那工艺的极限在哪里?

当制程低于20nm时候,由于二氧化硅绝缘层太薄了,只有几个原子那么厚,那么这个时候对于晶体管来说是十分不稳定的,会导致电子随意穿过壁垒导致漏电,导致芯片功耗增加。不过这个还算是小问题,Intel弄出了高介电常数薄膜和金属门集成电路,以及耳熟能详的FinFET鳍式场效晶体管结构,通过增加绝缘层表面积来增加电容值,以此降低漏电流大小的问题。同时为了制造出7nm线宽,行业共识是采用EUV极紫外作为光刻光源,具有曝光次数少、不要进行克服衍射效应产生的光学邻近修正特点,不过目前依然有大量问题,因此EUV光刻技术尚未完全成熟。

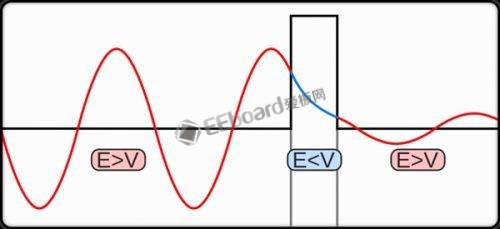

当工艺进步到7nm的时候,半导体企业更加不淡定了,因为在硅基半导体上,晶体管的线宽下降到7nm,一个不可避免的问题发生了,那就著名的量子隧穿效应。

在经典物理中,宏观粒子的能量小于势垒高度时,这个粒子是不可能穿过这个势垒,但是对于微观粒子,此时具有波粒二象性,神奇的量子效应就出现了,即便是能量低于势垒高度,仍有一定的概率可以突破势垒。这要就造成一个大问题,这个电子到底过去了没有,监测到没有,逻辑门该输出0还是1,答案不知道,那么CPU就不能正常工作,因此要杜绝这个问题发生。

Intel、台积电、三星等半导体制造前沿企业均已经针对这个问题进行了研究,依然有一些措施可以防止量子隧穿效应的出现。对于硅基半导体,Intel是展望的工艺极限是5nm或者3nm;三星的话后续会有8/7/6/5/4nm LPP工艺,并且在4nm会引入Multi Bridge Channel FET结构(简称MBCFET,多沟道场效应管),独特GAAFET(逻辑门环绕场效应晶体管)技术,使用二维纳米片晶克服物理扩展以及FinFET架构带来的局限性。

而媒体上低于3nm工艺的报道都不是基于硅氧化物,而是石墨烯等新型复合半导体材料,而且全都是实验室技术突破,无法短时间内量产的。但寻找新材料代替硅制作更低制程的晶体管是一个行之有效的解决方法之一。

纳米制程工艺背后的虚与实

通读全文,你就知晓目前半导体制程所谓的10nm 、7nm已经偏离最初的范畴,不再是严格意义上线宽,16nm“优化”一下可以叫12nm,10nm“优化”还可以叫8nm。作为摩尔定律拥护者的Intel当然是气不过,多次点评批评三星、台积电的“数字美化”行为。实际从晶体管密度参数上看,三星的7nm≈Intel 10nm,如此看来Intel的10nm难产也是情有可原,目标定得太高,却被友商狡猾地换了个名字所取胜,普罗大众却因为不懂工艺制程的虚实而相信厂商的一面之词。Intel的制造工艺技术其实并没有那么不堪,仍然处于世界领先地位。

-

英特尔

+关注

关注

60文章

9383浏览量

168624 -

三星电子

+关注

关注

34文章

15596浏览量

180085 -

台积电

+关注

关注

43文章

5242浏览量

164755 -

纳米制程

+关注

关注

0文章

21浏览量

9064

发布评论请先 登录

相关推荐

7纳米制程竞争激烈 台积电3月领先量产

决战7纳米制程,台积电拼足了劲!

电子行业人士带你入行之纳米制程小白篇

电子行业人士带你入行之纳米制程小白篇

尔必达40纳米制程正式对战美光

英特尔推出32纳米制程工艺的酷睿i7

英特尔开始研发7纳米和5纳米制程工艺

传台积电、三星电子10纳米制程量产卡关

高通骁龙670首次曝光 10纳米制程工艺

台积电:7纳米制程已大量生产,5纳米制程预计明年初风险性试产

为追赶台积电,三星宣布携手ARM进一步优化7纳米及5纳米制程芯片

揭秘纳米制程工艺背后的虚与实

揭秘纳米制程工艺背后的虚与实

评论