设计背景:

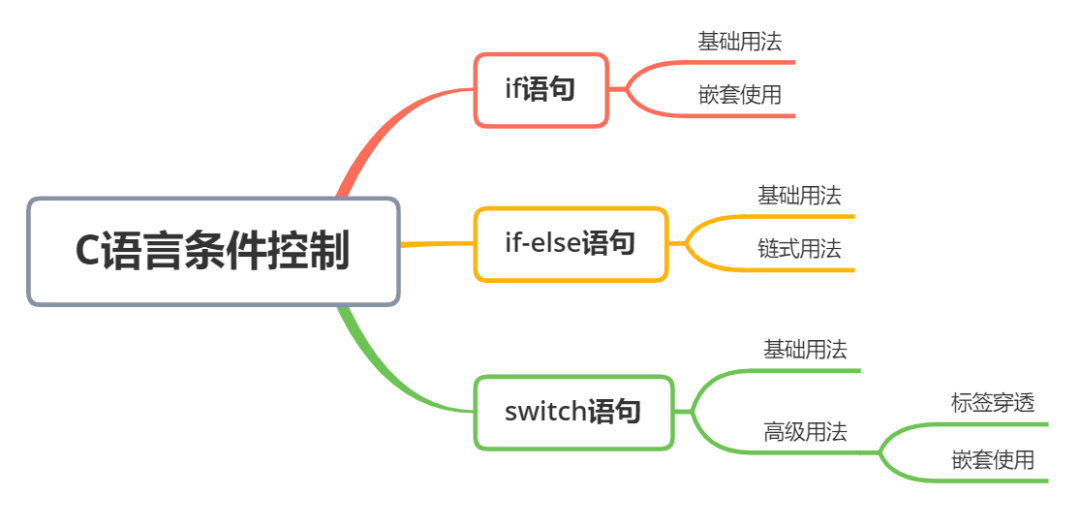

不管是在什么软件和硬件语言,我们在我们的代码中都或多或少的用到这两条语句,if..else与case语句,今天我们将学习verilog中的这两条语句,其实不管在什么语言中这两个语句都是一样的逻辑。

设计原理:

if...else 条件语句的作用是根据指定的端盘条件是否满足来确定下一步要执行的操作他们的书写格式如下

(1)if (条件语句) (2)if(条件语句) (3)if(条件语句)

语句 语句 语句

else else if(条件语句)

语句 语句

else

语句

(1)语句是if(条件语句)满足则条件成立,也就是这个逻辑执行结果为1,则执行条件语句成立执行的语句,如果不满足,就执行else给出的条件语块,然后才推出这个条件语句。

(2)语句是if(条件语句)满足则条件成立,也就是这个逻辑执行结果为1,则执行条件语句成立执行的语句,如果不满足则直接推出条件语句。

(3)语句是if(条件语句)满足则条件成立,也就是这个逻辑执行结果为1,则执行条件语句成立执行的语句,如果不满足,就判断else if(语句块)是否满足,如果满足就就执行else if 条件给出的语句,如果也不满足这个条件就执行else 给出的语句,然后执行完就退出条件语句。

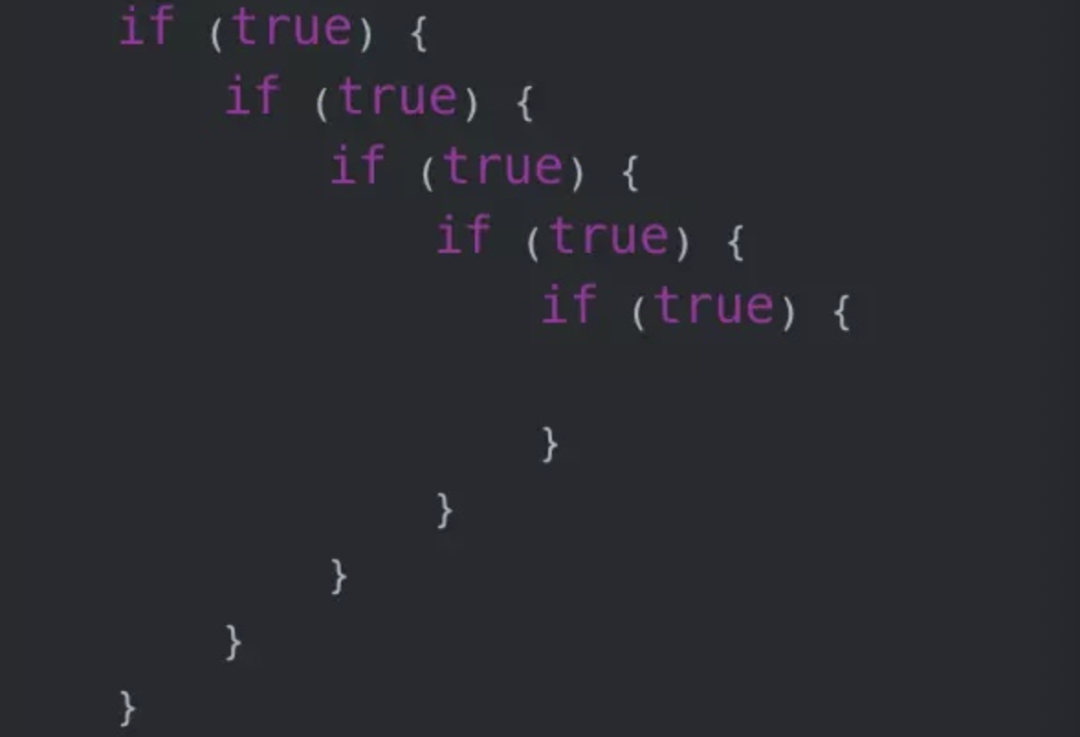

if ... else 条件语句也允许语句的嵌套也就是

if(...)

..

else

if()

...

else

等语句块

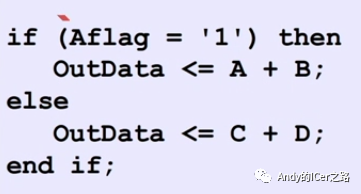

代码演示 :

module led_run (a, b, c);

input a, b; //定义输入输出

output reg c;

always @ (*)

if(a) //判断a是否为1

c = b; //如果是1的话,就是b的值给c

else

c = ~b; //如果不是1的话,就把b的反值给c

endmodule

仿真图:

仿真中我们可以看到和我们写的分析逻辑一样,a = 1 的时候。b = 0, c = 0 ,a = 0的时候, b = 0,c = 1 ........

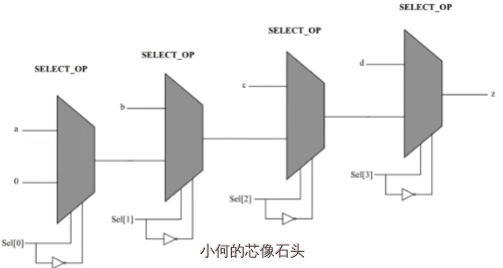

case 语句是另一种可以实现多路分支控制的分支语句,和使用if - else 相比,采用case 语句实现多路控制看起来代码逻辑看起来更加清楚明了。

case (控制表达式)

<分支表达式1> : 语句块 1

<分支表达式2> : 语句块 2

<分支表达式3> : 语句块 3

...............

default : 语句块;

endcase

控制表达式代表着对程序流向进行控制的控制信号,各个分支语句表达式代表着控制表达式的状态取值,通常分支表达式都是一些常量表达式,各个语句在分支表达式满足的情况下执行相应的语句块语句,最后有一个关键字default 分支项,这个项可以缺失,在case语句中分支语句的值各不相同,如果相同就会出现矛盾的现象,这应该不是我们想要的。

代码演示 :

0moduleled_run (a,b,sel,c);

1

2 inputa,b; //定义输入输出

3 input[1:0]sel;//输入选择位

4 outputregc;

5

6 always@(*)

7 case(sel)

8 2'b00 :c =a;//选择位为0,把a值给c

9 2'b01:c =b; //选择位为1,把b值给c

10 2'b10:c =~a;//选择位为2,把a反值给c

11 2'b11:c =~b;//选择位为3,把a反值给c

12 default:c =0;//否则c =0

13 endcase

14

15endmodule

仿真图:

仿真中我们可以看到和我们写的分析逻辑一样,a = 1 的时候。b = 0,sel = 1;c = 0 ,a = 1的时候, b = 0,sel = 0,c = 1 ........

-

Case

+关注

关注

0文章

24浏览量

13304

发布评论请先 登录

相关推荐

oracle case when 语法介绍

java switch case的语法规则

Verilog代码:if-else和case的电路结构和区别

Switch case中的case顺序

嵌入式软件架构表驱动方法介绍

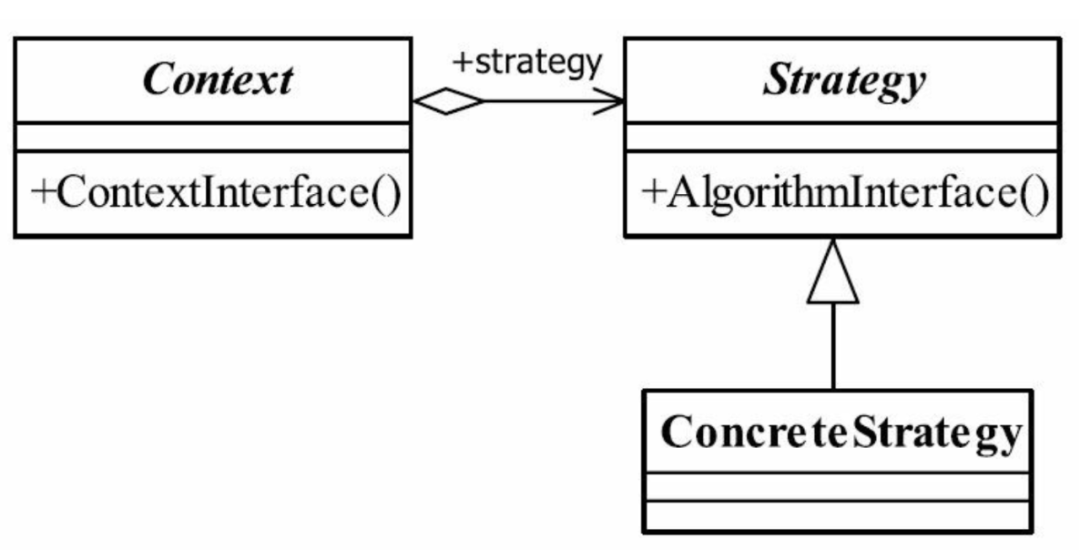

如何通过策略模式简化if-else

如何解决冗长的if...else条件判断(上)

【verilog每日一练】if_else语句优先级

CASE:创建多路分支

代码如何优化掉多余的if/else?

FPGA学习系列:if-else与case

FPGA学习系列:if-else与case

评论