设计原理:

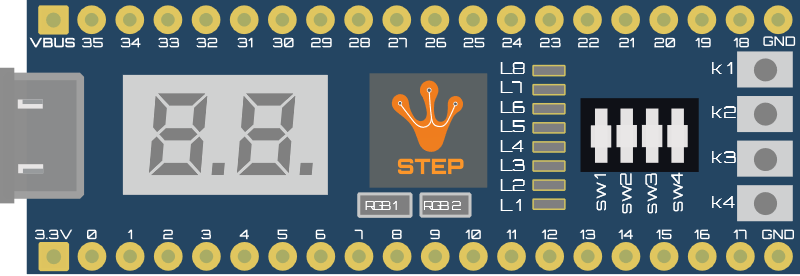

在以后的设计中,用的开发板都将是我们至芯科技自主设计的开发板,我们的芯片用的是Cyclone4系列的EP4CE10F17C8,在以后的设计中我们将不再讨论我们的开发板

今天的设计是流水灯,在单片机中我们也了解到流水灯的点亮,不就是高电平或者低电平亮或者灭,然后通过依次的点亮LED灯,就形成了流水

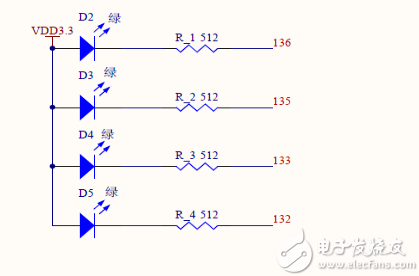

我们用的开发板的电路图如下

在点图中我们可以了解到我们的点亮电路,几个灯都是公用的是高电平也就是3.3V,所以只要给一个低电平就可以点亮我们的流水灯

我们的开发板提供的晶振是50M的,50M一个周期是20ns,我们人眼能够分辨的的速度是45ms左右,也就是物体如果45ms移动一次我们看清它是停一下走一下的,如果快于这个时间的话,那么我们看到的物体的移动就是连贯的。我们要设计出人眼可以分辨的流水就需要我们设计出大于这个时间灯亮灭,然后形成人眼可以分辨的流水。

本次我们的设计流水灯的流水时间是1s,那么我们就需要一个时间寄存器,当计数到1s的时候我们点亮一个灯,等下一个1s来的时候,我们点亮下一个等,然后形成流水,50M是20ns,1s是1hz,那么我们需要计数50 000 000

值得提的是我们算计数的时间是一面的等式 :计数 = 晶振 / 需要的频率 ,计数的时间就是我们1hz的周期,那么计数到一半的时候就是半个周期,我们可以在计数一半的时候clk 翻转,那么当技计数到的时候就是占空比50%的1hz的周期

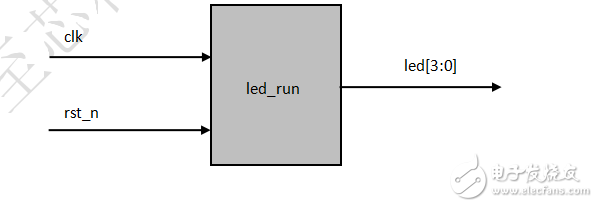

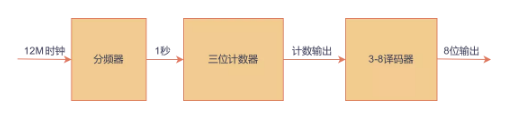

设计架构图:

设计代码:

设计模块

0moduleled_run (clk,rst_n,led);

1

2 inputclk,rst_n;

3

4 outputreg[3:0]led;

5

6 reg[25:0]count;

7 regclk_1hz;

8

9 always@(posedgeclk)

10 if(!rst_n)

11 begin

12 clk_1hz <=1;

13 count <=0;

14 end

15 elseif(count <(50_000_000/1/2-1))//计数

16 count <=count +1'd1;

17 else

18 begin //当计数到的时候,得到1hz的时钟

19 count <=26'd0;

20 clk_1hz <=~clk_1hz;//~时钟翻转

21 end

22

23 always@(posedgeclk_1hz)

24 if(!rst_n)

25 led <=4'b0111; //复位点亮第四个灯,熄灭1 2 3 灯

26 else

27 led <={led[0],led[3:1]};//当时钟上升沿来的时候把led的第一位 放在

28 //第四位,2 -- 4位放在 3 -- 1位,依次的移位,也就是把复位中的低电平 不停的

29 //移动在4 --1 位之中的某一位,从而实现流水

30endmodule

测试模块

0`timescale1ns/1ps

1

2moduletb();

3

4 regclk,rst_n;//定义模块的端口

5 wire[3:0]led;

6

7 initialbegin

8

9 clk =1;

10 rst_n =0;

11

12 #200.1rst_n =1;

13

14 #20000$stop;//延迟20000 Ns后 停止计数

15

16 end

17

18 always#10clk =~clk;//产生一个50M的时钟

19

20 led_run dut( //例化设计模块

21 .clk(clk),

22 .rst_n(rst_n),

23 .led(led)

24 );

25

26endmodule

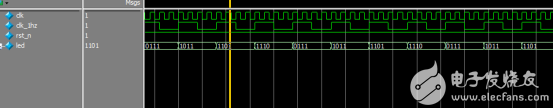

仿真图:

在仿真中我们可以调下我们设计模块的中的计数值,这样在仿真中我们可以我们可以快速的等到仿真结果,要不然你仿真几个小时可能才会出结果

在仿真中我们可以可以看到在我们的1hz时钟的上升沿,我们led的4位中的一位将有一位变化为0,从而实现流水

大家可以下板测试

-

FPGA

+关注

关注

1600文章

21284浏览量

592883 -

流水灯

+关注

关注

21文章

432浏览量

59094

发布评论请先 登录

相关推荐

基于FPGA的音乐流水灯控制系统设计

基于Verilog FPGA 流水灯设计_流水灯源码_明德扬资料

如何上手FPGA实现简单的流水灯效果

FPGA零基础学习:LED流水灯设计

详解基于FPGA的数字电路对流水灯的实验

51单片机学习笔记———8.点亮流水灯的一种奇葩算法

【FPGA Vivado】基于 FPGA Vivado 的流水灯样例设计

【STM32学习】(3)流水灯的实现

基于FPGA开发板流水灯的设计实现

FPGA学习系列:8. 流水灯的设计

FPGA学习系列:8. 流水灯的设计

评论