中国异构计算标准研究多项成果有望加速落地

2018年5月29日,中国异构系统架构标准(CSH)暨全球异构系统架构标准(HSA CRC)研讨会在湖南理工学院圆满召开。本次会议由中国电子技术标准研究院、全球异构系统架构联盟中国区域委员会(HSA CRC)主办,中国异构系统架构标准工作组(CSH)和湖南理工学院承办。来自HSA联盟会员单位、中国异构系统架构标准工作组成员单位、相关高校、科研院所及企事业单位的50余名专家学者出席了本次会议。

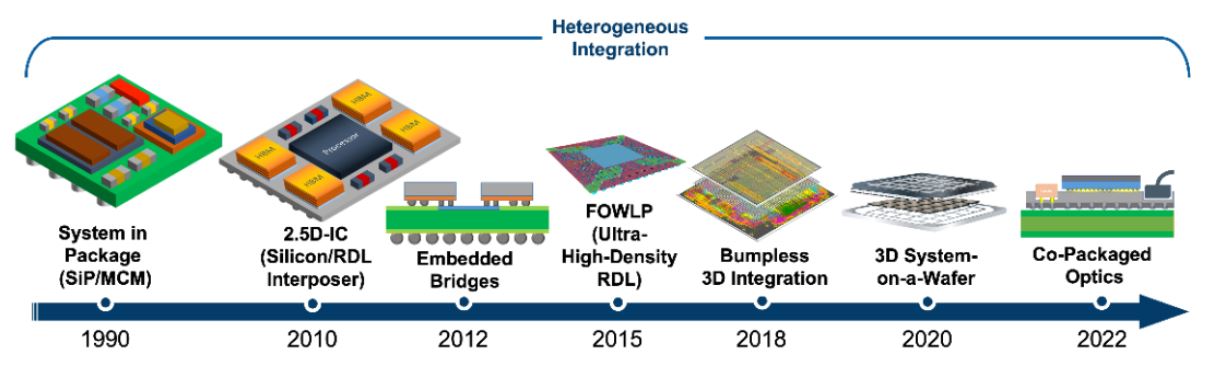

近年来,异构计算作为高端可编程芯片、低功耗软件定义芯片、嵌入式计算、高性能计算等领域的研究热点和主流计算机体系架构的发展方向,受到国内外广泛关注。本次会议围绕国内和国际异构计算标准研究的最新进展及异构计算在人工智能、智能安防、智能机器人、智能辅助驾驶/无人驾驶、智能物联网、商业卫星星载平台等领域的应用进行了技术研讨与提案建议,为相关产业的产品研发、产业分工、生态形成以及一致性检测提供了关键接口定义与支撑。中国异构计算标准是我国在下一代可编程异构计算系统芯片领域的第一个国家标准研究项目,标准的制定对于我国在大数据和人工智能时代抢占高端处理器架构设计主导权和推动相关产业链的快速完善意义重大、影响深远,将有望彻底打破国外巨头垄断高端芯片的产业格局。

本次会议重点讨论了第一版系列标准提案,以及对若干新增标准提案进行审议。会上,中国异构系统架构标准工作组组长张小东博士介绍了2018年中国异构计算标准工作组的工作目标、工作进展和行动规划,各工作组就形成的异构系统架构第一版系列标准提案进行了充分的讨论与解读,针对草案的整体框架、内容重点、新增板块等给予了积极建议。随后,国家电网、华夏芯、复旦大学、江苏软件定义无线电中心、京微齐力、国民技术、中山大学等标准工作组成员单位分别就标准应用评估、指令架构、系统架构、安全防护和网络互连等领域进行了标准提案和审议报告。

本次会议是中国异构系统架构标准工作组本年度的第一次会议,标准工作组至成立以来成员规模不断加大,目前已经超过50家企事业、高校、科研院所单位加入,陆续成立了应用与评估、虚拟指令架构、系统架构、编译与库、操作系统与多厂商、网络互连、安全与系统防护及一致性测试在内的8个工作组,已经成为了中国异构计算标准制定、实施和生态建设的核心平台。

后续,中国异构系统架构标准工作组将于6月在南京就中国异构计算标准进展和在人工智能、物联网、机器人等领域的技术应用和成果推广继续开展系列研讨和交流活动,欢迎各届对异构系统架构有兴趣的企业单位、高校、科研院所等参与到异构系统架构国标的制定工作中来,垂询方式:E-mail:hsacrc@hxgpt.com

-

异构系统架构

+关注

关注

1文章

4浏览量

7183 -

华夏芯

+关注

关注

1文章

7浏览量

3113

发布评论请先 登录

相关推荐

2024 ETAP 电气系统数字孪生平台技术研讨会(深圳站)

第一届中欧计算机架构研发与RISC-V机遇与合作研讨会成功举办

启明信息参加“工业互联网平台”系列团体标准启动会暨首次研讨会

IEEE标准大会无线短距通信技术与标准化研讨会圆满落幕

一座难求!国产嵌入式处理器工业研讨会-广州站,圆满落幕!

新一代计算架构超异构计算技术是什么 异构走向超异构案例分析

异构计算场景下构建可信执行环境

航顺芯片提供ARM+RISC-V异构多核MCU

2018中国异构系统架构标准(CSH)暨全球异构系统架构标准(HSA CRC)研讨会在湖南召开

2018中国异构系统架构标准(CSH)暨全球异构系统架构标准(HSA CRC)研讨会在湖南召开

评论