随着电子行业技术的发展,特别是在传输接口方面,从PCI到PCI Express、从ATA到SATA、从并行ADC接口到JESD204、从RIO到Serial RIO等等,无一都证明了传统并行接口的速度已经达到瓶颈,取而代之的是速度更快的串行接口,于是原本用于光纤通信的SerDes技术成为了高速串行接口的主流。串行接口主要应用了差分信号传输技术,具有功耗低、抗干扰强,速度快的特点,诸如PCI Express®(PCIe®)Gen4等串行链路接口的数据传输率将达到双位千兆级传输速率。由此,器件建模、互连建模和分析方法必须不断发展,以应对不断减小的设计余量和当今工程师面临的更具挑战的合规标准。本系列文章将从各方面深入分析探讨,为了降低风险并优化设计,将分析尽可能地推向上游至关重要,以实现权衡、可行性研究、元件选择和约束获取。

自动合规性检查

有了详细的布局后互连以及IBIS-AMI模型的正确执行,您可以关注特定的、感兴趣的接口(本例中为PCI Express Gen 4)的合规性检查。

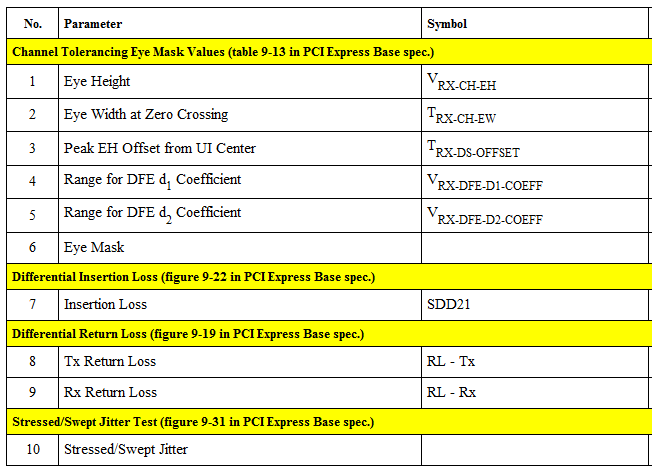

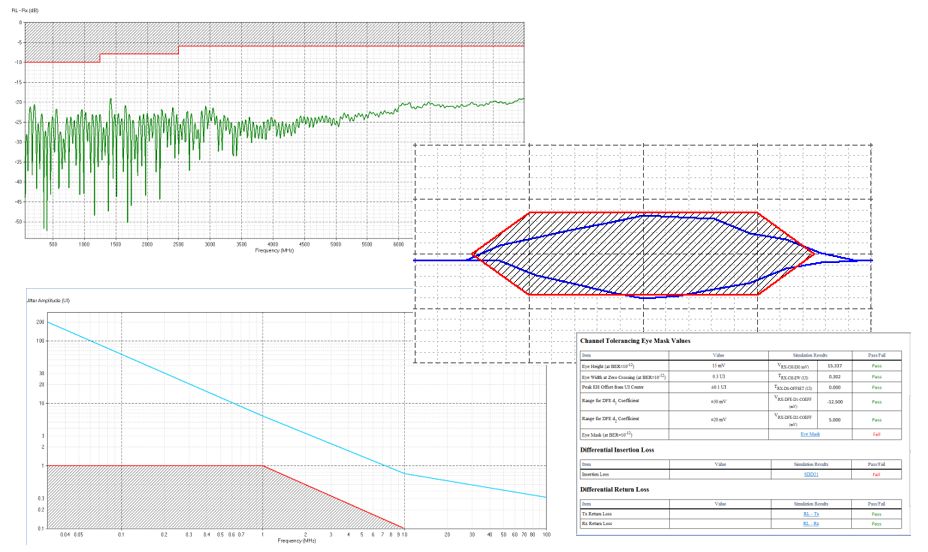

每个接口都有自己的特定标准。在这种情况下,PCI Express确定了许多眼图相关的时域标准、无源互连通道的频域标准以及满足特定抖动容限范围的能力。

单独评估这些标准可能会非常耗时,特别是,如果需要多次运行来扫描设计范围和多个通道模型的情形。用于通用串行链路标准的自动合规工具包通常会提供一些仿真工具,可帮助大幅加快合规性检查速度并缩短签收时间。

图:PCI Express合规性检查

自动扫描关键参数,并标记合规性故障,可以更好地覆盖您的串行链路设计,并可帮助检查您所关心的其他领域。

图:PCI Express合规性检查结果

使用合规性工具包的另一个主要好处是能够在预布局阶段使用相关的模板。正如前面所讨论的那样,为可行性权衡建立早期测试平台至关重要。但是在这个阶段通常缺乏一些必要模块的真实模型,有时需要使用“占位符”模型。随自动合规套件提供的模板通常会预先填充实际的拓扑和模型,包括发射器和接收器的SerDes IBIS-AMI模型的规范级模型,并根据该特定标准的规范中描述的参考参数进行构建。这些模板以及与它们相关的模型为您的布局前测试平台开发提供了一个很好的起点,有助于最大限度地减少启动和运行所需的时间,避免设计返工。

总结

本文总结了该系列的8篇文章,内容是关于“多千兆位串行链路接口的SI方法”。本系列中之前的博客文章主题为:

通过“自上而下”的方法将SI推向上游

PCB互连的预布局建模

IBIS-AMI建模

启用约束驱动设计

高效的互连提取

使用IBIS-AMI模型进行仿真

反向信道训练

两位数的千兆数据速率的串行链路接口有其独特的设计挑战。从预设计阶段开始,自上而下的分析方法可减轻相关风险、并可避免高代价、费时间的重新设计。这项工作的成果是为了确定约束驱动物理布局所需的布线规则。需要特别注意过孔结构来控制插入损耗和回波损耗;将已知良好的过孔结构导入布局的方法至关重要。需要IBIS-AMI模型来表示在这些数据速率下看到的自适应均衡和反向信道功能,并且可以根据需求快速构建规范。“切割和缝合”(“Cut& stitch”)技术可以运用在需要提取布线后互连提取,在获得全波仿真精度的同时,避免端到端全波3D提取的计算损失。自动合规工具包可促进串行链路设计的成功签收,同时为预布局分析阶段提供有价值的起点。

-

PCI

+关注

关注

4文章

608浏览量

129573 -

串行接口

+关注

关注

3文章

307浏览量

42265

原文标题:Ken的博客系列之八 | 千兆位串行链路接口的SI方法

文章出处:【微信号:CadencePCB,微信公众号:CadencePCB和封装设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

深入分析探讨多千兆位串行链路接口的SI方法

深入分析探讨多千兆位串行链路接口的SI方法

评论