大家好,到了每日学习的时间了。今天我们来聊一聊FPGA的片内资源相关知识。

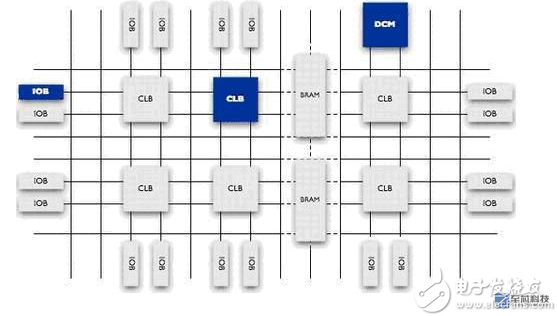

主流的FPGA仍是基于查找表技术的,已经远远超出了先前版本的基本性能,并且整合了常用功能(如RAM、DCM和DSP)的硬核(ASIC型)模块。如图所示,FPGA芯片主要由7部分组成,分别为:可编程输入输出单元(IOB)、基本可编程逻辑单元(CLB)、完整的时钟管理(DCM)、嵌入式块RAM、丰富的布线资源、内嵌的底层功能单元和内嵌专用硬件模块。

1.可编程输入输出单元(IOB)

可编程输入/输出单元简称I/O单元,是芯片与外界电路的接口部分,完成不同电气特性下对输入/输出信号的驱动与匹配要求。FPGA内的I/O按组分类,每组都能狗独立地支持不同的I/O标准。通过软件的灵活配置,可是配不通电气标准与I/O物理特性,可以调整驱动电流的大小,可以改变上、下拉电阻。I/O口的频率也越来越高。

为了便于管理和适应多种电气标准,FPGA的IOB被划分为若干组(bank),每个bank的接口标准由其接口电压VCCO决定,一个bank只能有一种VCCO,但不同的bank可以有不同的VCCO,只有相同电气标准的接口才能连接在一起。

2.可配置逻辑块(CLB)

CLB是FPGA内的基本逻辑单元,CLB的实际数量和特性会因为器件的不同而不同,但是每个CLB都包含一个可配置开关矩阵,此矩阵由4或6个输入、一些选型电路(MUX)和触发器组成。开关矩阵是高度灵活的,可以对其进行配置以组成组合逻辑、移位寄存器或RAM。在Xilinx公司的FPGA器件中,CLB有多个相同的Slice和附加逻辑组成,每个CLB模块不仅可以用于实现组合逻辑、时序逻辑,还可以配置为分布式RAM和分布式ROM。

Slice是Xilinx公司定义的基本逻辑单位,一个Slice由两个4输入的函数发生器(LUT)、进位逻辑、算数逻辑、存储逻辑和函数复用器组成。

3.数字时钟管理模块(DCM)

业内大多数FPGA均提供数字时钟管理(Xilinx全部FPGA都有这种特性)。Xilinx推出最先进的数字时钟管理和相位环路锁定。DCM可以完成对时钟的分频倍频功能,并能维持各时钟之间的相位关系,即零时钟偏差。

4.嵌入式块RAM(BRAM)

BRAM有很高的灵活性,可以被配置位单端口RAM、双端口RAM、内容地址存储器(CAM)以及FIFO等常用存储结构。在实际应用中,芯片内部BRAM数量是芯片选型的一个重要因素,单片块RAM的容量是18kbits,即位宽为18比特、深度为1024。也可以根据需要更改其位宽与深度(位宽不得大于36bits)。亦可以将多块BRAM级联起来形成更大的RAM。

5.丰富的布线资源

布线资源连通FPGA内部所有单元,而连线长度和工艺决定着信号在连线上的驱动能力和传输速度。FPGA芯片内部有着丰富的不限资源,根据工艺、长度、宽度和分布位置而划分为4类不同的类别。第一类是全局布线资源,用于芯片内部全局时钟和全局复位/置位的布线;二、长线资源,用以完成芯片bank之间的高速信号和第二全局时钟信号的布线;三、是短线资源,用于完成基本逻辑单元之间的逻辑链接和布线;四、分布式的布线资源,用于专有时钟、复位等控制信号线。

6.底层内嵌功能单元

内嵌功能模块主要是指DLL(Delay Locked Loop)、PLL(Phase Locked Loop)、DSP和CPU等软处理核。

7.内嵌专用硬核

内嵌专用硬核是相对底层迁入的软核而言的,等效于ASIC电路。为了提高FPGA性能,芯片生产商在芯片内部集成了一些专用的硬核。例如:专用乘法器,串并收发器(SERDES)可以达到数十Gbps收发速度。

今天就聊到这里,各位,加油。

-

FPGA

+关注

关注

1599文章

21278浏览量

592839

发布评论请先 登录

相关推荐

聊一聊FPGA的片内资源相关知识

聊一聊FPGA的片内资源相关知识

评论