如果处理器和现场可编程门阵列FPGA全部由同样的电压供电运行,并且不需要排序和控制等特殊功能的话,会不会变的很简单呢?不幸的是,大多数处理器和FPGA需要不同的电源电压,启动/关断序列和不同类型的控制。

幸运的是,电源管理IC集成电路 (PMIC) 能够控制目前的高级处理器、FPGA和系统,并为它们供电,从而大为简化了整个系统设计。

现在,你也许想知道哪一款PMIC可以为你的片上系统 (SoC) 供电,还有就是要这么做的话,该从哪里入手。为你的SoC和系统选择合适的电源解决方案是系统设计人员最常见的挑战之一。所以,TI推出了数款全新工具,在使用我们的PMIC时,这些工具能够简化器件选型、评估和设计。

在这些工具中,有一些是TI Designs参考设计,它们可以帮助设计人员开始、验证和加快设计。多个TI Designs已经发布,给出了可由TI PMIC供电的很多不同SoC—以下是当前列表:

-

TIDA-00478使用TPS65218为Xilinx Zynq 7010供电。

-

TIDA-00551使用TPS65911 为Xilinx Zynq 7015供电。

-

TIDA-00604使用TPS65023为Altera Cyclone III供电。

-

TIDA-00605使用TPS65023为Altera Cyclone IV供电。

-

TIDA-00607使用TPS65218为Altera MAX 10供电。

-

TIDA-00621使用TPS65911。

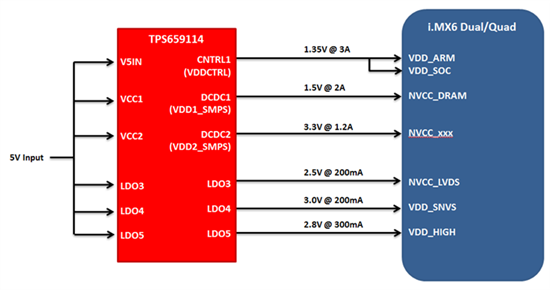

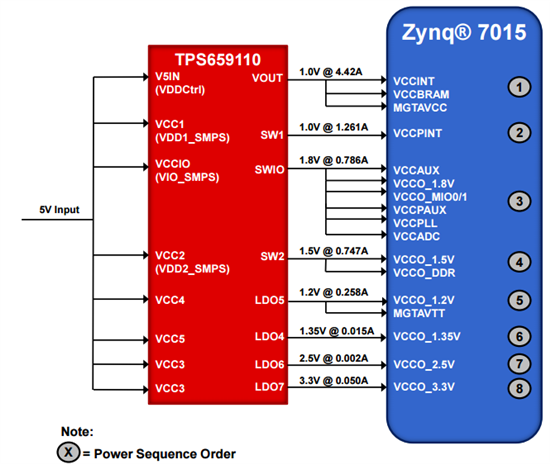

图1是为ARM处理器供电的TPS65911的方框图。与所有TI PMIC一样,TPS65911非常灵活,并且可被用于数款器件。图2显示的是为Xilinx Zynq 7015 FPGA供电的TPS65911。

图1:TPS65911的方框图

图2:为Xilinx Zynq 7015供电的TPS65911的方框图

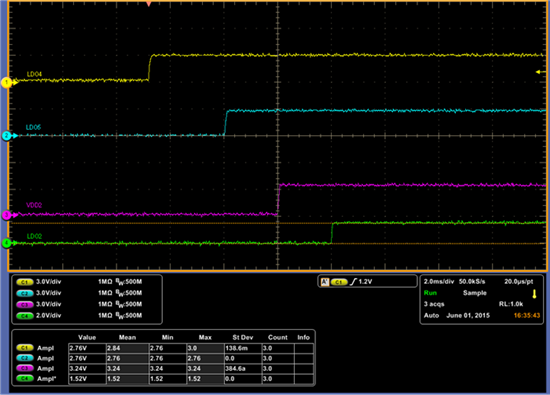

随这些设计一同提供的还有电路原理图、方框图、印刷电路板 (PCB) 文件和测试结果。这些测试使得设计人员能够评估他们正在尝试用于特定SoC的PMIC的性能,并且为他们提供可以在他们自己的设计中使用的示例设计文件。测试结果包括启动排序、负载瞬态、效率测试,以及图3中显示的其它内容。

图3:TPS65911的示例启动时序

-

FPGA

+关注

关注

1602文章

21309浏览量

593130 -

电源管理

+关注

关注

112文章

6013浏览量

141101

发布评论请先 登录

相关推荐

FPGA与AISC的差异

什么是FPGA原型验证?FPGA原型设计的好处是什么?

FPGA管教分配需要考虑因素

fpga验证及其在soc验证中的作用有哪些

虹科分享 | 6种方式,ValSuite报告帮助改善您的验证过程!

多片FPGA原型验证的限制因素有哪些?

从SoC仿真验证到FPGA原型验证的时机

多片FPGA原型验证系统互连拓扑分析

FPGA原型验证中分割引擎的重要性解析

如何利用FPGA设计来验证和加快你的设计过程

如何利用FPGA设计来验证和加快你的设计过程

评论