在DDR的PCB设计中,一般需要考虑等长和拓扑结构。等长比较好处理,给出一定的等长精度通常是PCB设计师是能够完成的。但对于不同的速率的DDR,选择合适的拓扑结构非常关键,在DDR布线中经常使用的T型拓扑结构和菊花链拓扑结构,下面主要介绍这两种拓扑结构的区别和注意要点。

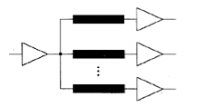

T型拓扑结构,也称为星型拓扑结构,星型拓扑结构每个分支的接收端负载和走线长度尽量保持一致,这就保证了每个分支接收端负载同时收到信号,每条分支上一般都需要终端电阻,终端电阻的阻值应和连线的特征阻抗相匹配。星形拓扑结构可以有效地避免时钟、地址和控制信号的不同步问题。

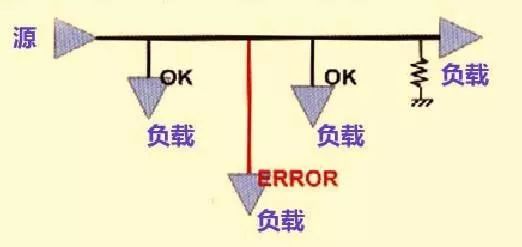

菊花链拓扑结构,和星型拓扑结构不同,菊花链拓扑结构没有保持驱动端到各个负载走线长度尽量一致,而是确保各个驱动端到信号主干道的长度尽量短。菊花链拓扑结构走线的特点,牺牲了时钟、地址和控制信号的同步,但最大的特点是尽可能降低各负载分支走线长度,避免分支信号对主干信号的反射干扰。

在信号频率低于800MHz的情况下,上面两种拓扑结构均能满足系统性能需要。但是当信号速率到达1000MHz甚至更高,T型拓扑结构就不能满足性能需要。原因就在于T型拓扑结构过长的支路走线长度,在不添加终端电阻的情况下很难和主干道实现阻抗匹配,而为了实现各个支路的阻抗匹配添加终端电阻,又加大了电路设计的工作量和成本,是我们不愿意看到的。因此高速信号使用T型拓扑结构,特别是Stub>4的时候,支路信号对主干信号的反射干扰是很严重的。通常DDR2使用和速率要求不高的DDR3使用T型拓扑结构。

菊花链拓扑结构主要在DDR3中使用,菊花链拓扑结构的主要优势是支路走线短,一般认为菊花链支路走线长度小于信号上升沿传播长度的1/10,可以有效削弱支路信号反射对主干信号的干扰,不同的书本上说法也不一样,大体上走线长度小于上升沿传播长度的1/6-1/10都是可以的,实际设计中我们肯定希望这个长度越短越好。菊花链拓扑结构可以有效抑制支路的反射信号,但相对于T型拓扑结构,菊花链拓扑结构的时钟、地址和控制信号并不能同时到达不同的DDR芯片。

为了解决菊花链拓扑结构信号不同步的问题,DDR3的新标准中加入了时间补偿技术,通过DDR3内部调整实现信号同步。当信号频率高达1600MHz的时候,T型拓扑结构已经无能为力,只有菊花链或其衍生的拓扑结构能满足这样的性能需求。一般的DDR3都会建议采用菊花链拓扑结构的改进型拓扑结构,Fly-by拓扑结构要求支路布线长度Stub=0,Fly-by具有更好的信号完整性。

在菊花链拓扑的实际应用中,为了抑制Stub过长和分支太多对主干信号的反射干扰,以及加强主干信号驱动能力,一般在末端预留端接电阻电路。末端下拉电阻会增大IO口驱动功耗,所以采用末端上拉电阻的方式进行端接。计算信号驱动部分的戴维南等效电压作为上拉电压Vtt,Rt为驱动部分的等效电阻,通常上拉电压取值为IO驱动电压的一般,即Vtt=Vddr/2。

-

DDR

+关注

关注

9文章

676浏览量

64221 -

PCB设计

+关注

关注

392文章

4568浏览量

83183

原文标题:干货|DDR布线要求及拓扑结构

文章出处:【微信号:PCBTech,微信公众号:EDA设计智汇馆】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

方波与电平两种状态如何区别的问题

案例分享之DDR拓扑结构的选择

PCB中常见的两种传输线结构

请问TPS74201和TPS74301这两种LDO的主要区别是什么?

两种可消除励磁电流失配和失配漂移影响的方法

两种不同结构的永磁同步电机特点说明

干货 | 如何快速掌握11种开关电源拓扑结构?看这篇就够了!

BOOST电路拓扑结构介绍

常见的ARM架构分为两种一种是M系列另外一种是A系列,这两种有什么区别啊?

ddr3菊花链拓扑结构是什么

两种拓扑结构的区别和注意要点

两种拓扑结构的区别和注意要点

评论