由于在裸板或者在uboot存在的情况烧写kernel以及yaffs2 fs的时候 Nand 中oob、bbt、ecc很大程度上影响了烧写的成功率,所以我们下面进行没含义进行了解:

芯片内部存储布局及存储操作特点:

一片Nandflash为一个设备(device), 其数据存储分层为:

1 (Device) =4096 (Blocks)

1 (Block) -= 32 (Pages/Rows)页与行是相同的意思,叫法不一样

1(Page) = 528 (Bytes) =数据块大小(512Bytes) + OOB 块大小(16Bytes)

在每一页中,最后16个字节(又称OOB)用于NandFlash命令执行完后设置状态用,剩余512个字节又分为前半部分和后半部分。可以通过NandFlash命令00h/01h/50h分别对前半部、后半部、OOB进行定位通过

Nand Flash内置的指针指向各自的首地址。

存储操作特点:

1.擦除操作的最小单位是块。

2. NandFlash芯片每一位(bit)只能从1变为0,而不能从0变为1,所以在对其进行写入操作之前要一定将相应块擦除(擦除即是将相应块得位全部变为1).

3.OOB部分的第六字节(即517字节)标志是否是坏块,如果不是坏块该值为FF,否则为坏块。

4.除OOB第六字节外,通常至少把OOB的前3个字节存放Nand Flash硬件ECC码。

BBT:bad blocktable,即坏块表。各家对nand的坏块管理方法都有差异。比如专门用nand做存储的,会把bbt放到block0,因为第0块一定是好的块。但是如果nand本身被用来boot,那么第0块就要存放程序,不能放bbt了。

有的把bbt放到最后一块,当然,这一块不能为坏块。

有的bbt中用2个bits表示1个block的状态,所以1个字节可以表示4个blocks。

bbt的大小跟nand大小有关,nand越大,需要的bbt也就越大。

所以具体代码具体分析。

ECC:

NANDFlash出错的时候一般不会造成整个Block或是Page不能读取或是全部出错,而是整个Page(例如512Bytes)中只有一个或几个bit出错。一般使用一种比较专用的校验——ECC。ECC能纠正单比特错误和检测双比特错误,而且计算速度很快,但对1比特以上的错误无法纠正,对2比特以上的错误不保证能检测。

ECC一般每256字节原始数据生成3字节ECC校验数据,这三字节共24比特分成两部分:6比特的列校验和16比特的行校验,多余的两个比特置1.

当往NANDFlash的page中写入数据的时候,每256字节我们生成一个ECC校验和,称之为原ECC校验和,保存到PAGE的OOB(out-of-band)数据区中。其位置就是eccpos[]。

校验的时候,根据上述ECC生成原理不难推断:将从OOB区中读出的原ECC校验和新ECC校验和按位异或,若结果为0,则表示不存在错(或是出现了ECC无法检测的错误);若3个字节异或结果中存在11个比特位为1,表示存在一个比特错误,且可纠正;若3个字节异或结果中只存在1个比特位为1,表示OOB区出错;其他情况均表示出现了无法纠正的错误。

-

芯片

+关注

关注

446文章

47653浏览量

408561 -

嵌入式

+关注

关注

4975文章

18225浏览量

287643 -

存储

+关注

关注

12文章

3843浏览量

84618

原文标题:嵌入式 Nand 中oob、bbt、ecc含义小结

文章出处:【微信号:gh_c472c2199c88,微信公众号:嵌入式微处理器】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

NAND 闪速存储器的内部结构

请教AD9954的内部存储器问题

DRAM存储原理和特点

EEPROM的存储原理/选型/特点/应用

STM32控制器芯片内部的程序存储空间

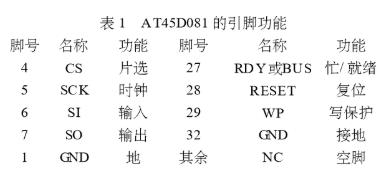

大容量闪烁存储器芯片AT45D081的内部结构、特点及应用

随机存取存储器的最大特点

浪潮存储在全闪存储领域的产品及技术布局

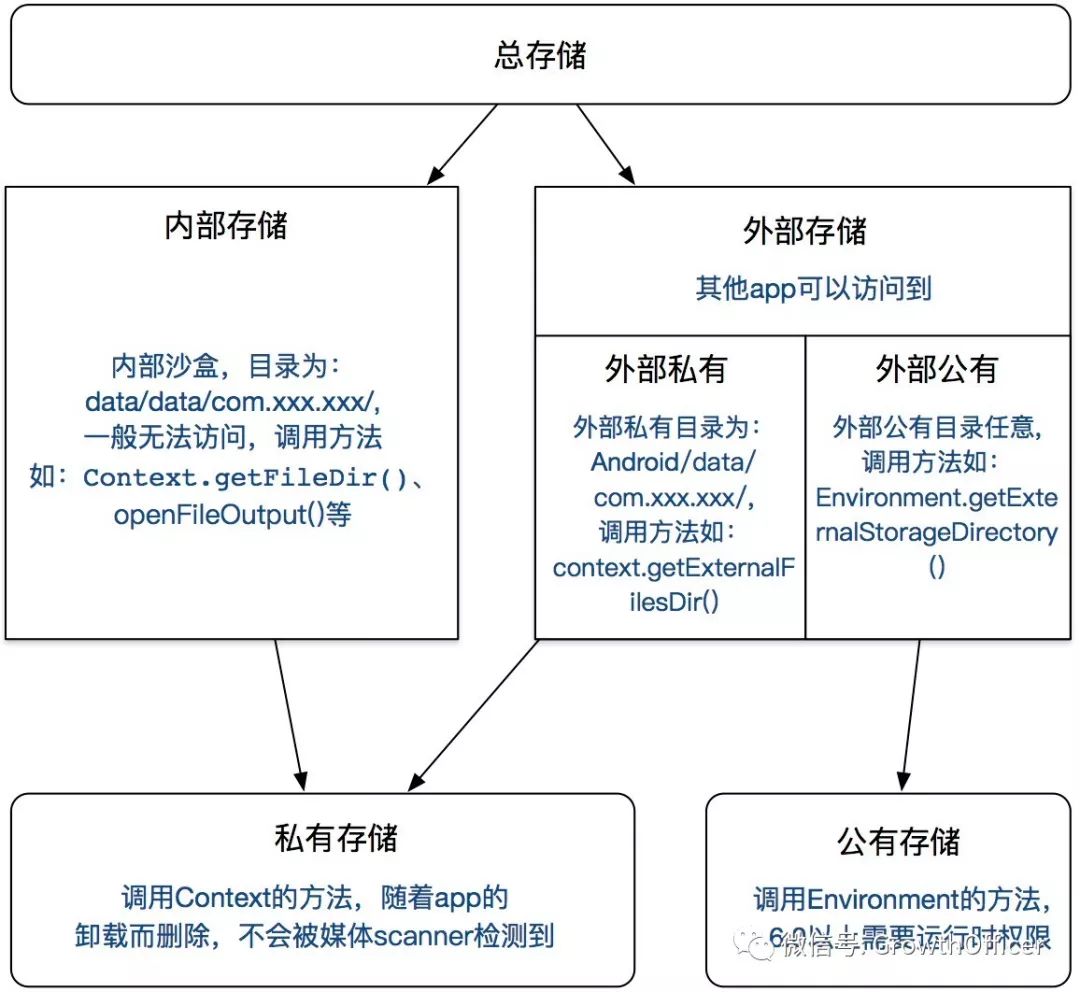

外部存储和内部存储的区别

芯片内部存储布局及存储操作特点

芯片内部存储布局及存储操作特点

评论