在介绍事务层之前,首先简单地了解一下PCIe总线的通信机制。假设某个设备要对另一个设备进行读取数据的操作,首先这个设备(称之为Requester)需要向另一个设备发送一个Request,然后另一个设备(称之为Completer)通过Completion Packet返回数据或者错误信息。在PCIe Spec中,规定了四种类型的请求(Request):Memory、IO、Configuration和Messages。其中,前三种都是从PCI/PCI-X总线中继承过来的,第四种Messages是PCIe新增加的类型。

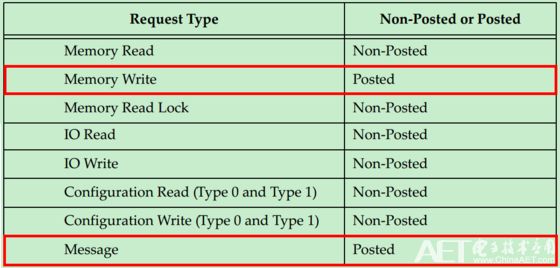

详细的信息如下表所示:

从表中我们可以发现,只有Memory Write和Message是Posted类型的,其他的都是Non-Posted类型的。所谓Non-posted,就是Requester发送了一个包含Request的包之后,必须要得到一个包含Completion的包的应答,这次传输才算结束,否则会进行等待。所谓Posted,就是Requester的请求并不需要Completer通过发送包含Completion的包进行应答,当然也就不需要进行等待了。很显然,Posted类型的操作对总线的利用率(效率)要远高于Non-Posted型。

那么为什么要分为Non-Posted和Posted两种类型呢?对于Memory Writes来说,对效率要求较高,因此采用了Posted的方式。但是这并不意味着Posted类型的操作不需要Completer进行应答,只是此时Completer采用了另一种应答机制——Ack/Nak的机制。

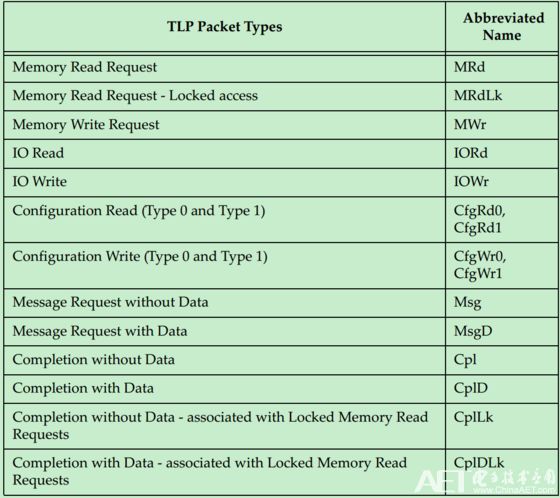

PCIe的TLP包共有一下几种类型:

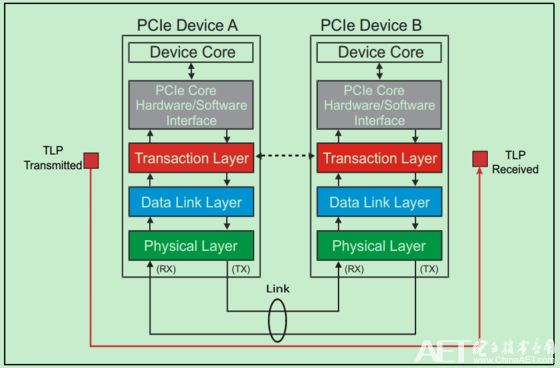

TLP传输的示意图如下图所示:

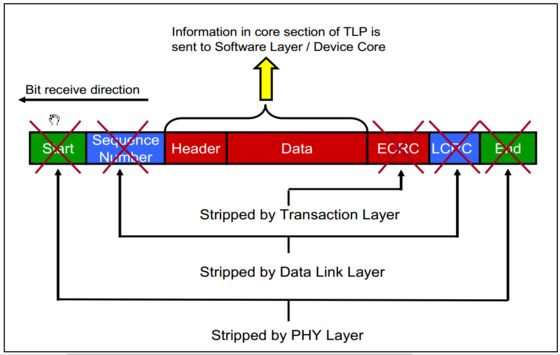

TLP在整个PCIe包结构的位置如以下两张图所示:(第一张为发送端,第二张为接收端)

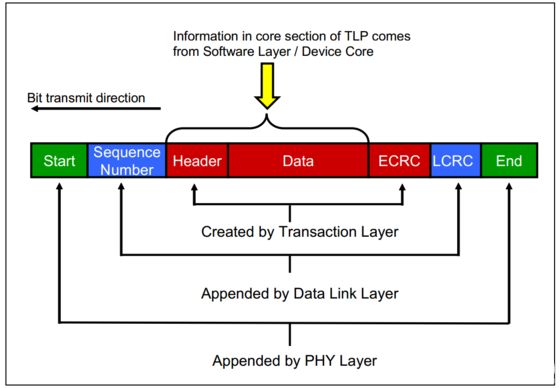

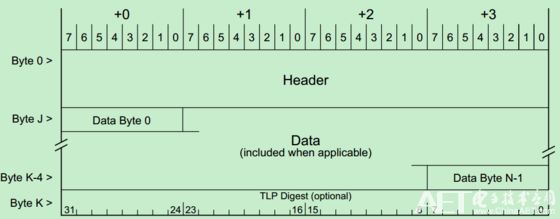

其中,TLP包的结构图如下图所示:

图中的TLP Digest即ECRC(End-to-End CRC),是可选项。此外,TLP的长度(包括其中的Header、Data和ECRC)是以DW(双字,即四个字节)为单位的。

-

总线

+关注

关注

10文章

2692浏览量

87141 -

PCIe

+关注

关注

13文章

1078浏览量

80694

原文标题:【博文连载】PCIe扫盲——PCIe总线事务层入门(一)

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

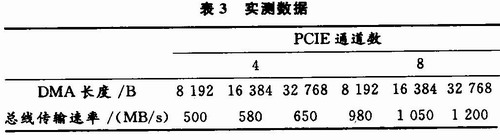

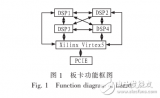

基于FPGA的PCIE总线扩展卡的设计

PCIe总线的复位方式是什么?

如何利用PCIe DMA总线实现一个基于FPGA的PCIe 8位数据采集卡?

基于PCIE总线的多DSP系统接口设计

进一步提升PCIe总线通信速度的方法

采用Flow Control机制的PCIe总线

PCIe总线的通信机制

PCIe总线的通信机制

评论