针对环形振荡器的功耗大、噪声大、线性度差等问题,基于TSMC 55 nm工艺,提出了一种新型交叉前馈结构环形振荡器电路。深入分析了器件自身热噪声、闪烁噪声对环形振荡器输出相噪贡献百分比,利用电容滤波技术来降低振荡器输出相噪,采用源极负反馈电路得到线性电流来改善调频线性度,并提供了宽调谐范围。Spectre RF仿真结果表明,设计的环形振荡器频率覆盖范围为0.2 GHz~3.8 GHz,产生8相位,相位噪声为-91.34 dBc/Hz@1 MHz,在1.2 V电源电压下消耗电流为4.6 mA ,线性度良好。

0引言

压控振荡器(VCO)是一种由电压控制输出频率的振荡器,是无线通信系统中一个重要的模块,也是锁相环电路(PLL)的核心,它的相位噪声、灵敏度等参数直接影响PLL的最终性能。环形振荡器比电感电容谐振压控振荡器(LC VCO)有很多显著的优势:不需电感元件,节省芯片面积,节省成本,调谐范围宽,并且很容易实现多相位。不过,环形振荡器的相位噪声性能通常要稍差一些。综合考虑其功耗低、面积小和集成高等优点,环形振荡器被广泛应用在通信领域。目前,低功耗、低噪声、宽调谐的新型环形振荡器结构吸引了众多学者投入研究,例如文献[1]中设计了一种频率范围为2.05 GHz~3.35 GHz的环形振荡器,其相位噪声为-89.6 dBc/Hz@1 MHz,核心电路的功耗为18.36 mW,不过,其功耗较大,不能满足在无线通讯系统中的低功耗要求。针对振荡器存在的功耗大、噪声大、线性度差等问题,提出了一种新型环形振荡器结构,该环形振荡器的频率范围为0.2 GHz~3.8 GHz,产生8相位,相位噪声为-91.34 dBc/Hz@1 MHz。

1环形振荡器

1.1 环形振荡器

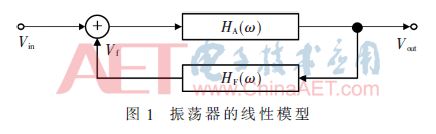

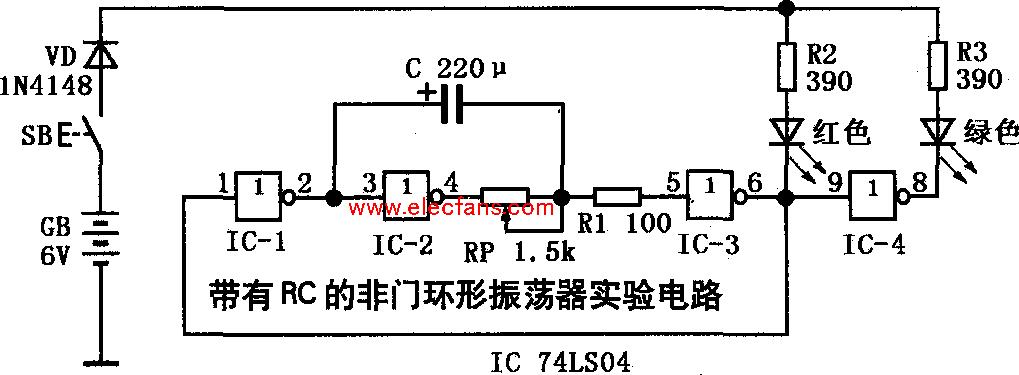

环形振荡器的核心结构是在一个振荡频率处呈正反馈的环路,如图1所示。

图中,HA(ω)是基本放大器的传输函数,HF(ω)为反馈网络的传输函数。反馈系统的闭环增益为式(1):

环形振荡器的工作原理是环路传输函数仅在一个频率点上满足Barkhausen判据,即在某一频率ω下满足式(2)就可以产生振荡。

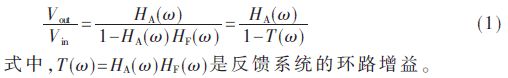

其中,ω0表示输入电压为0的输出频率,KVCO为VCO的增益,单位为rad/(s·V),Vcon为控制电压。

1.2 电路原理分析与设计

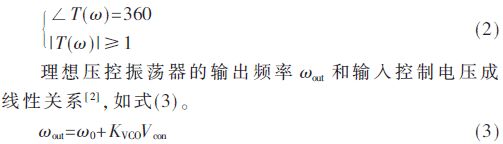

环形振荡器的相位噪声主要来自于散粒噪声、热噪声和环境噪声。热噪声是温度、带宽和电阻作用的结果;散粒噪声是直流偏置电流引起的;而环境噪声主要来自VCO外部电源的噪声和衬底的噪声。延迟单元可以采用单端结构和差分结构,以差分结构为基本延迟单元构成的差分环形振荡器具有很好的对称性,在克服环境噪声方面具有很大的优势,但是由于电路复杂,不仅增大了芯片的面积,而且带来较多的热噪声,因此选用结构简单、器件少的单端结构,可以有效地减少由器件本身带来的热噪声。一个N级的环形振荡器,每级的延时为td,则其频率为:

其中,Icharge为充电电流,Cpar为延时单元输出节点的总寄生电容,Vdd为供电电压。

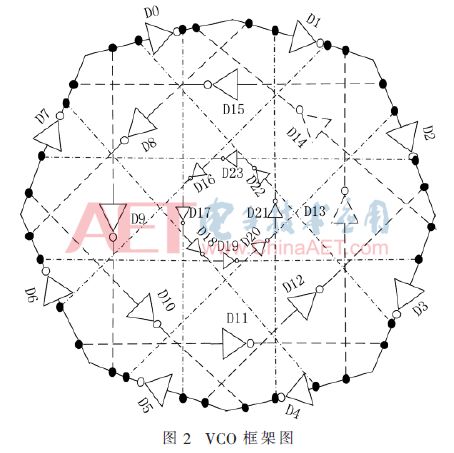

考虑到芯片面积,设计的环形压控振荡主要由24个反相器组成,如图2所示,其中D0~D8依次首尾相连构成主环形结构。输入端用 Vcon表示,VCO的振荡频率随着输入端电压的变化而变化。

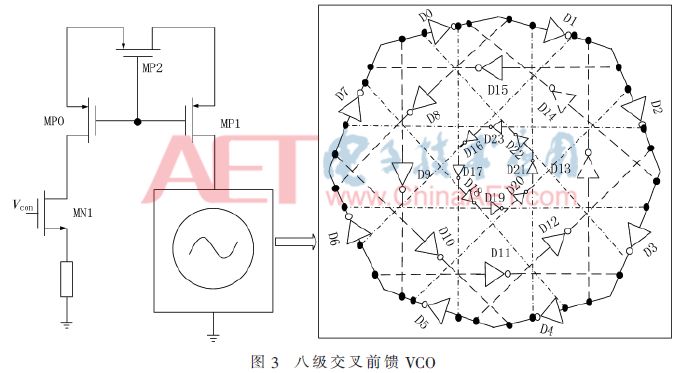

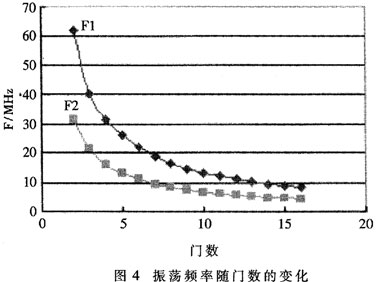

由图3可知,该VCO主要包含三种环路,第一种是由D0~D8八个延迟单元组成的最慢主环路,第二种是包含两个四级反向延迟单元组成的闭环环路,分别为D9—D11—D13—D15、D8—D10—D12—D14,另外还有一种包含四个闭环环路,分别为D16—D20,D17—D21,D18—D22,D23—D19分别组成的环路,主环路与各个子环路之间保持一个完美的对称关系。

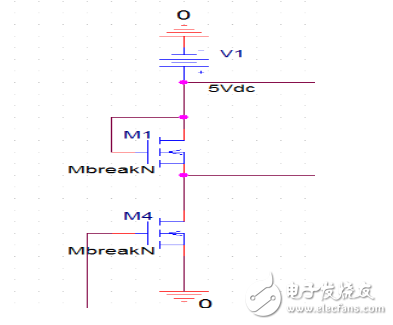

通过改变MN1的电流来改变负阻大小,那么MP0、MP1漏极等效电阻也随之改变,进而调节振荡频率,由于是低电源供电,MP0、MP1采用电流镜结构。MP0、MP1漏极等效阻值的变化会导致不同频率信号的输出摆幅不同,会影响VCO的噪声性能,为满足通信系统的需要,需要调整电流镜的宽长比进而优化压控振荡器相位噪声。

根据环形振荡器的振荡原理,这个以八级反相延迟单元为主环形链的VCO构成的压控振荡器可以实现正交相位的频率信号输出,可以有效抑制环境噪声,在时钟数据恢复电路中有着重要的应用[5]。

1.3 缓冲器设计

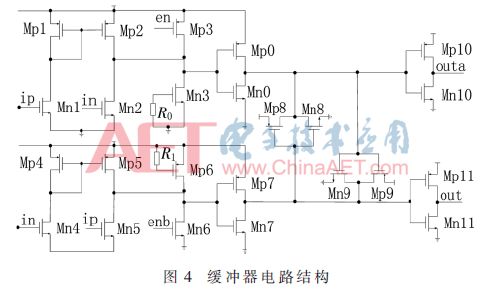

为了使环形振荡器有良好的输出匹配,在电路中引入如图4所示的缓冲级,它主要由差分对、单端反相器以及latch组成,差分对的输出作为反相器的输入,从而确保了电路的对称性。该缓冲级可以将环形振荡器的输出波形变为占空比50%的时钟信号,并且可以提高驱动能力。

1.4 版图设计

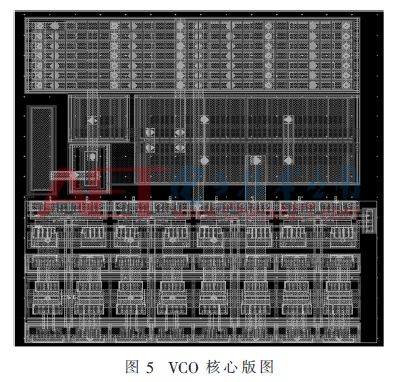

版图设计是集成电路工艺的重要部分,版图设计的好坏直接影响芯片的功能。本文设计的环形振荡器基于TSMC 55 nm工艺,着重分析了VCO匹配和降噪等问题,根据版图设计的基本规则利用virtuoso Layout Editor工具进行布局布线,并通过了DRC和LVS验证。设计的环形振荡器版图如图5所示,核心版图面积为70 μm×81 μm。

1仿真结果

2.1 前仿结果

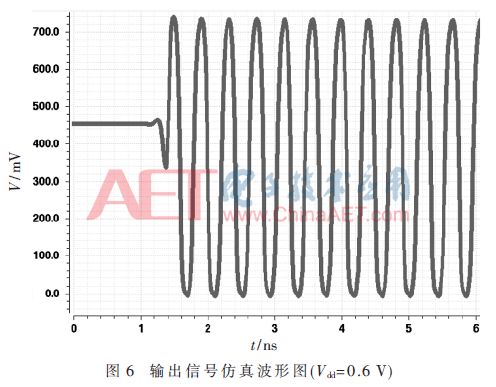

利用Cadence公司Spectre RF仿真工具进行瞬态仿真,结果如图6所示。从图中可以看出,当Vdd=0.6 V时,环形振荡器的起振时间约为1.4 ns,振荡幅度约为0.74 V。该结果说明振荡器的起振情况良好,且起振时间比较短。

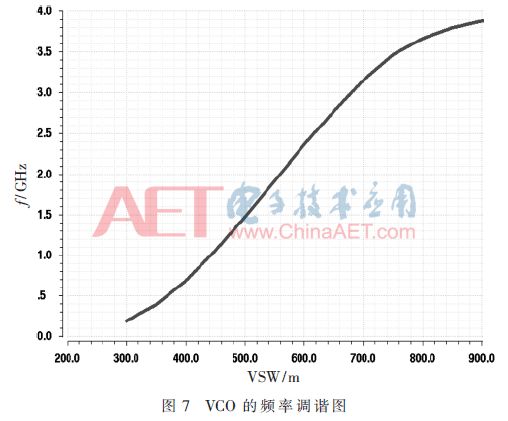

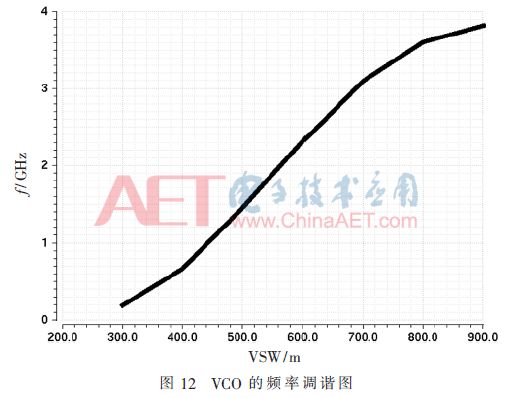

VCO的频率调谐图如图7所示,从图7可以看出,当控制电压在0~0.9 V之间变化时,VCO频率调谐范围为0.2 GHz~3.8 GHz,且调谐曲线在0.4~0.8 V具有较好的线性度。

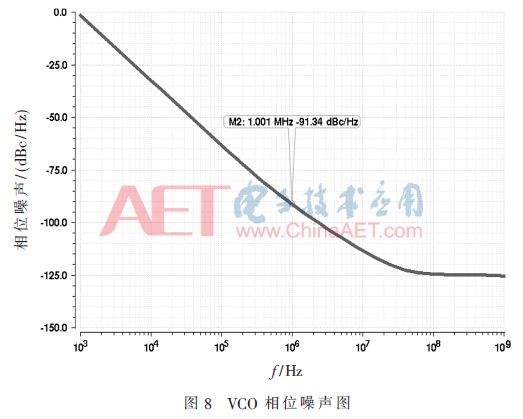

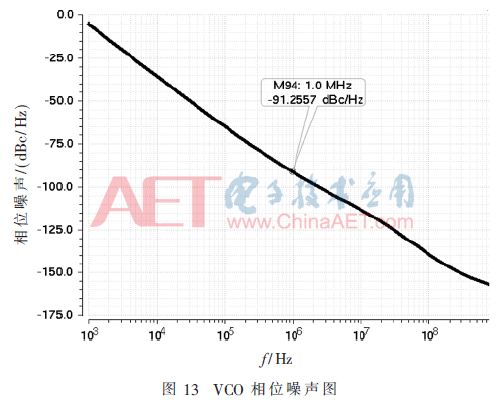

相位噪声是压控振荡器的重要参数和性能指标。压控振荡器的相位噪声性能通过PSS和PNOISE共同仿真得到,频偏范围设置为1 kHz到1 GHz。当调谐电压为0.6 V,输出中心频率为2.4 GHz时的整体电路相位噪声曲线如图8所示,可见在频偏1 MHz处,相位噪声为-91.34 dBc/Hz。

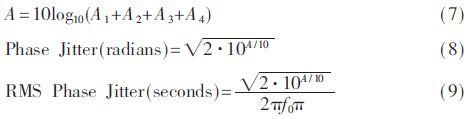

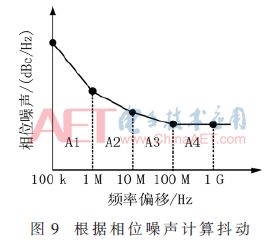

抖动(Jitter)和相位噪声均是衡量环形振荡器噪声性能的参数,抖动是在时域来衡量振荡器振荡信号过零点时间的不确定性;相位噪声是在频域来衡量振荡器的频谱纯度,它们在本质上是一样的,只是运用不同的表述方法来阐述同一种现象[6]。根据相位噪声计算抖动如图9所示,设A=面积=综合相位噪声功率(dBc),则:

在图8所示的相位噪声图中读取图9中各个频率偏移所对应的相位噪声。经计算得:

由于低频VCO通常抖动比较大,一般用PLL环可以有效过滤低频噪声。

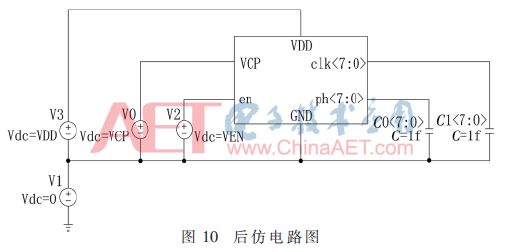

2.2 后仿真结果

经过对版图的修改与优化,通过DRC及LVS验证,运用版图参数提取工具PEX对版图进行了寄生电阻、寄生电容等参数的提取。图10给出了后仿真的电路原理图。

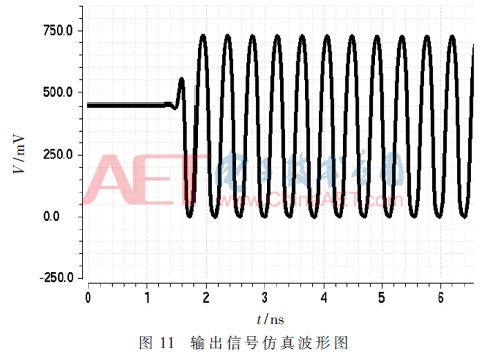

版图寄生参数提取后,搭建同样的仿真环境,运用仿真工具分别对VCO稳定振荡时的瞬态输出信号波形、调频特性和相位噪声性能进行了后仿真,后仿真结果分别如图11~图13所示。由图可知,后仿结果与前仿结果基本一致,可见版图设计满足振荡器的频率调节范围在0.2 GHz~3.8 GHz之间,中心频率处的相位噪声为-91.34 dBc/Hz@1 MHz,功耗为4.6 mW,线性度良好。

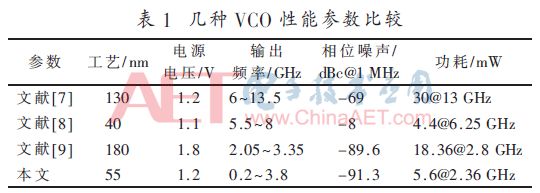

表1总结了设计的环形压控振荡器的性能参数,并与工艺条件相近的振荡器进行对比。可以看出,设计的环形振荡器在低功耗的条件具有较高的频率,并且相位噪声较好。

3结论

基于TSMC 55 nm工艺,采用交叉前馈电路结构设计了一个2.4 GHz的低功耗环形振荡器,在1.2 V电源电压下整个环形振荡器的最大功耗为5.6 mW,相位噪声为-91.34 dBc/Hz,该VCO具有低功耗、低相噪、可调节范围宽等优点,可应用于锁相环、频率发生器及时钟恢复等电路。

-

电路

+关注

关注

170文章

5480浏览量

169466 -

无线通信

+关注

关注

56文章

4193浏览量

142289 -

压控振荡器

+关注

关注

10文章

115浏览量

29167

原文标题:【学术论文】一种低功耗低噪声8相位输出环形振荡器

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

一种新型交叉前馈结构环形振荡器电路

一种新型交叉前馈结构环形振荡器电路

评论