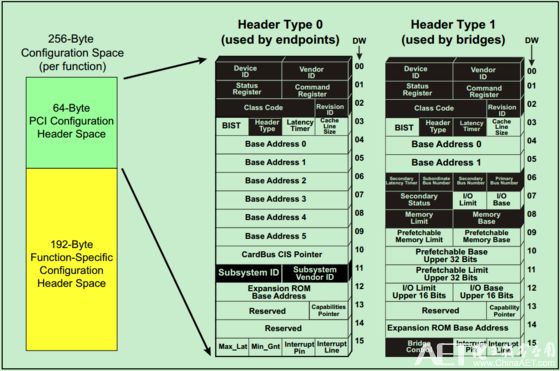

前面的文章中多次说道,PCIe总线在软件上是向前兼容PCI总线的。因此,PCIe总线完整的继承了PCI总线中的配置空间(Configuration Header)的概念。

在PCIe总线中也有两种Header,Header0和Header1,分别代表桥和非桥设备,这与PCI总线是完全一致的。在PCIe总线中,非桥设备也就是Endpoint。如下图所示:

如图所示,对比前面介绍的PCI的Header可以发现:PCIe的Header基本上与PCI的Header是一致的,只有少许差别。但是这些差别并不影响PCIe对PCI的兼容性(还有PCIe到PCI桥对其进行处理)。

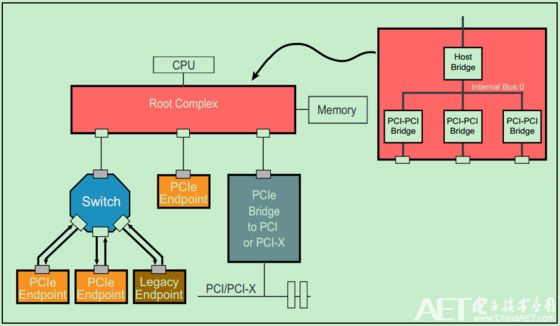

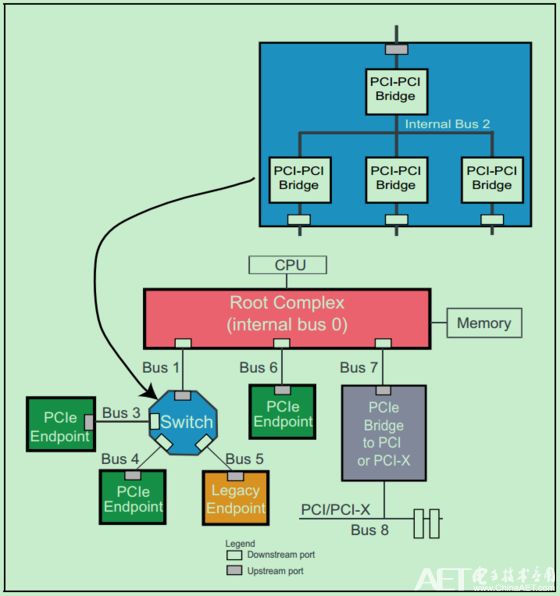

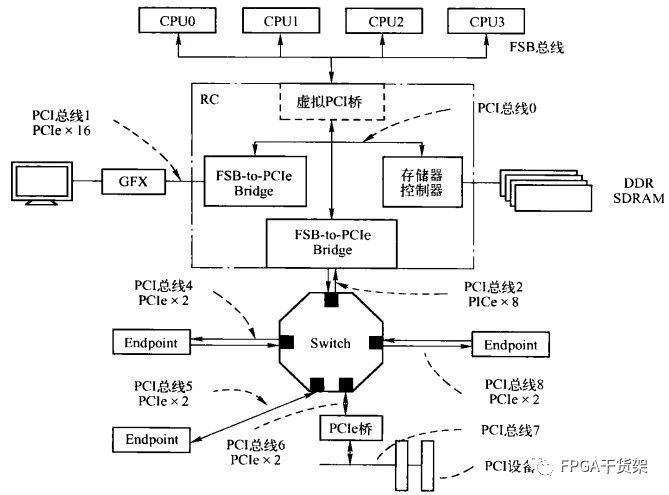

需要特别说明的是,Root Complex(RC or Root)和Switch都是全新的PCIe中的概念,它们结构中的每一个端口(Port)都可以对应于PCI总线中的PCI-to-PCI桥的概念。也就是说,每一个RC和Switch中一般都有多个类似于PCI-to-PCI桥的东西。分别如下两张图所示:

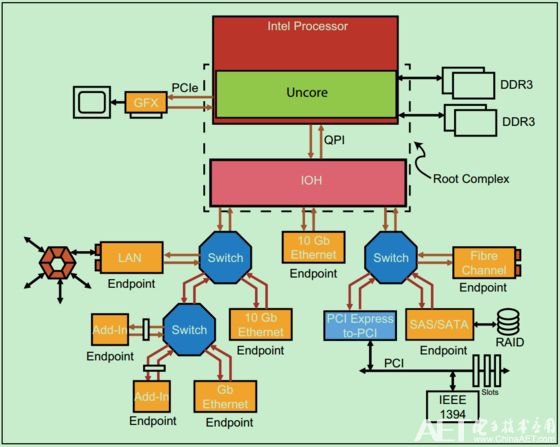

前介绍到过,PCIe总线是一种点对点(Point-to-Point)的总线,如果需要连接大量的设备,则需要很多的Switch来进行拓扑,这无疑会大大地增加系统的功耗与设计成本。在普通的PC或者小型计算机系统中,并不要连接很多的PCIe设备,因此Switch就显得并不是那么的必要了。一个典型的服务器PCIe总线系统的拓扑结构图如下图所示:

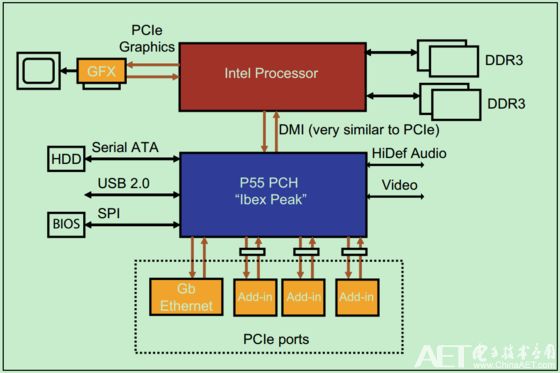

典型的PC的PCIe总线系统的拓扑结构图如下图所示:

-

pci总线

+关注

关注

1文章

200浏览量

31535 -

PCIe

+关注

关注

13文章

1083浏览量

80798

原文标题:【博文连载】PCIe扫盲——PCIe总线怎样做到在软件上兼容PCI总线

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于FPGA的PCIE总线扩展卡的设计

PCI Express总线架构和总线层次结构浅析

PCI总线接口芯片9054及其应用

PCI总线接口芯片9050及其应用

PCI总线接口芯片9054及其应用

基于FPGA的PCI Express总线接口应用

基于PCI总线的CPLD实现

Arm PCI配置空间访问固件接口1.0BET1平台设计文档

FPGA在PCI Express总线接口中的应用

PCIe总线完整的继承了PCI总线中的配置空间的概念

PCIe总线完整的继承了PCI总线中的配置空间的概念

评论