近日,IC 圈里出了一件大事,联发科技宣布推出业内第一个通过 7nm FinFET 硅验证的 56G PAM4 SerDes IP,扩大 ASIC 产品阵线。据了解,该 IP 方案具有一流的性能、功耗及晶粒尺寸(Die-area),已通过 7nm 和 16nm 原型芯片实体验证,可以很容易地整合进各种前端产品设计中。

联发科技在 ASIC 方面志向远大,涉足多种应用领域:企业级与超大规模数据中心、超高性能网络交换机、路由器、4G/5G 基础设施(回程线路Backhaul)、人工智能及深度学习应用、需要超高频宽和长距互联的新型计算应用。

一贯擅长 SoC 设计的联发科技,为什么要做 ASIC ? 这款 SerDes 方案有何优势?如何满足新一代以太网的高速传输需求?除 IP 外,联发科技提供怎样的 ASIC 服务?

小编为你带来最劲爆的分析~

Why ASIC?

ASIC 是 Application-Specific Integrated Circuit 的缩写,即“专用集成电路”,是指应特定用户要求,在一个芯片上实现特定部分或全部功能的集成电路。在服装界有定制的概念,根据个人的喜好和要求,为某个人单独设计一套衣服,满足人们的个性化需求。如果套用这个概念,ASIC 可以说是定制芯片,根据客户的需求,量身打造专用芯片,是企业实现产品差异化的好工具。

近年来,我们注意到,物联网、通信及一些消费领域的企业,尤其需要独特的 ASIC 解决方案。联发科技提供通过 7nm和 16nm 制程硅验证的 IP,可无缝整合进入先进的 ASIC 产品,更好地满足市场所需。

广泛的 SerDes 产品组合

SerDes 是英文 Serializer (串行器)和 Deserializer (解串器)的简称,取两个单词的前三个字母组合而成。

在介绍 SerDes 之前,我们有必要了解下串行和并行的区别。我们可以把串行比喻成一个车道,并行比喻成 8 个车道。并行虽然一次传输的字节数量多,但是由于 8 条通道之间的互相干扰,传输速度不免受到限制,而且当传输出错时,要同时重新传 8 位数据。而串行一次只传输一个字节,抗干扰能力更强,传输出错后重发一位就可以了,所以在长距离传输时,速度要比并行快。

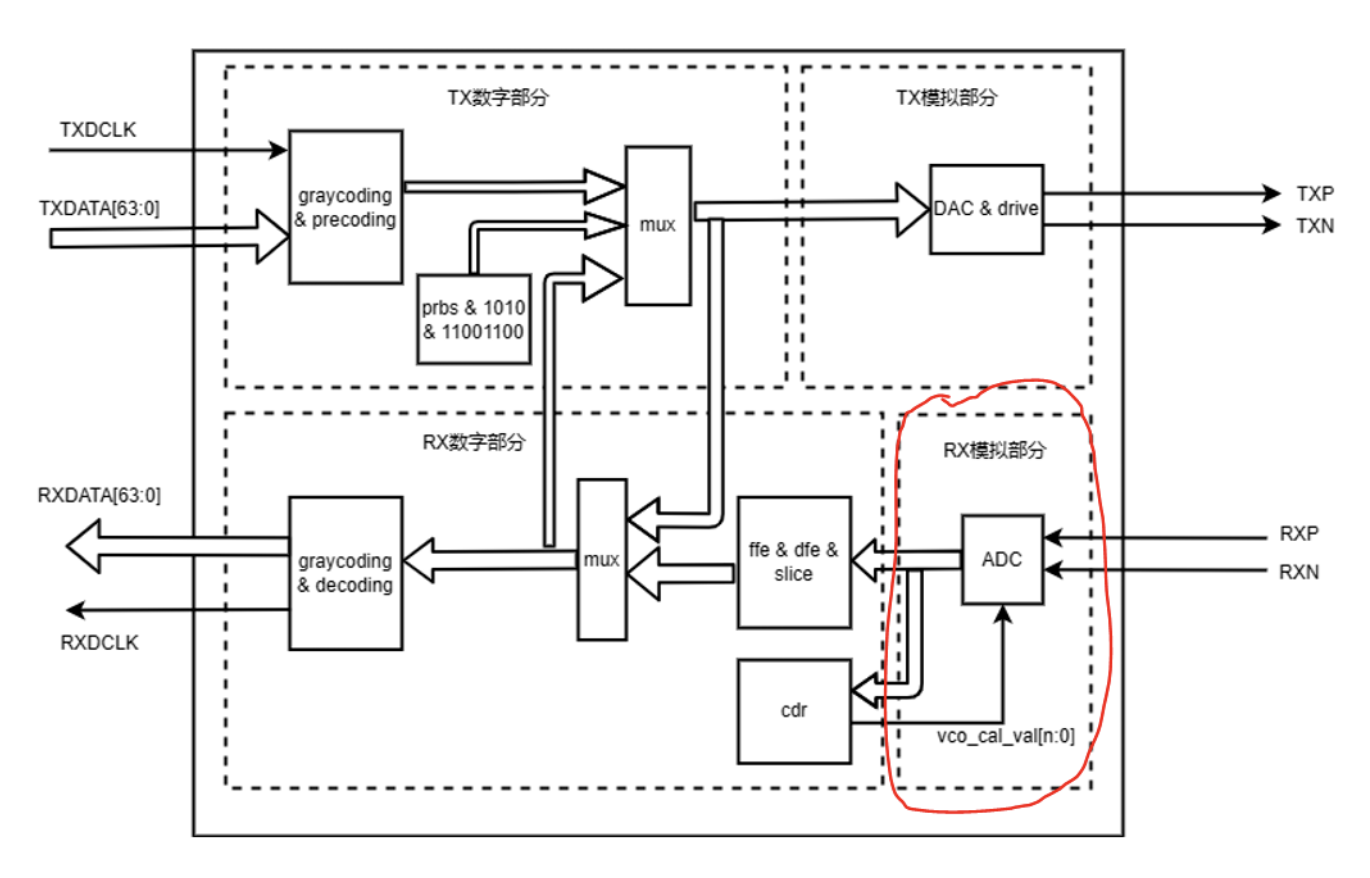

SerDes 在发送端将多路低速并行信号转换成高速串行信号,经过传输介质,最后在接收端,高速串行信号重新转换成低速并行信号,非常适合端到端的长距离高速传输需求。除了高速率外,联发科技 SerDes IP 的厉害之处还在于,可以保障信号在串/并行转换和传输过程中不失真。联发科技具有业界最广泛的 SerDes 产品组合,能为 ASIC 设计提供从 10G、28G、56G 到 112G 的多种解决方案。

用 PAM4 迎合新一代以太网

当大数据、云计算和物联网走向规模应用,万物的智能互联引发数据生态的巨变,从骨干网,核心网到交换中心的数据流量均大幅增加,因此必须提高网络带宽,以应对激增的数据压力。

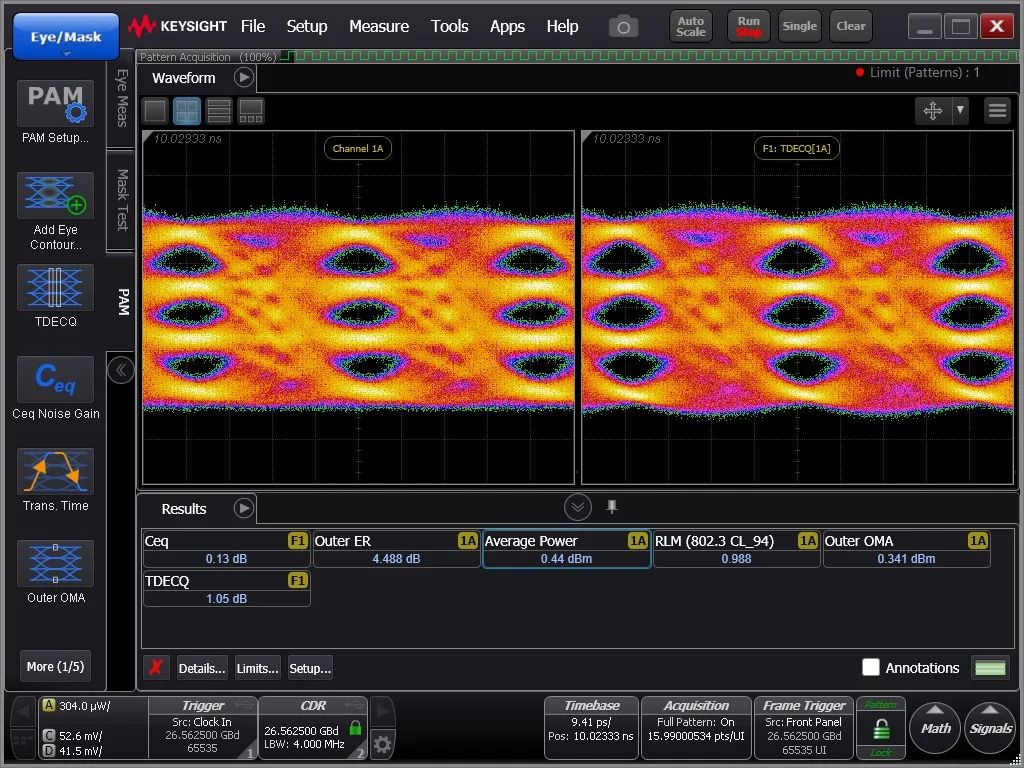

PAM4(4 级脉冲幅度调制)被公认为是实现新一代线路速率的最高可扩展性多级信号协议,它能够将现有基础架构的带宽提升一倍,帮助推进新一代以太网部署。

联发科技最新发布的 SerDes 解决方案基于数字信号处理(DSP)技术,采用高速传输信号 PAM4,可实现 56Gbps 的传输速率,满足高性能网络交换机、大规模数据中心等对数据传输的需求。

端到端完整的 ASIC 服务

不只提供 IP,联发科技还提供完整的 ASIC 服务,致力帮助寻求专业设计及客制化芯片设计方案的客户,在多个领域拓展商机,如:有线和无线通信、超高性能计算、低功耗物联网、无线连接、个人多媒体、先进传感器和射频。

联发科技的 ASIC 服务涵盖从前端到后端的任何阶段— 系统及平台设计、系统单芯片(SoC)设计、系统整合及芯片物理布局(Physical layout)、生产支持和产品导入。

ASIC 市场正在迎来新的发展机遇。我们相信,每一次小的升级、大的发布,都是去到下一个里程碑过程中的重要步骤。采用联发科技 56G SerDes IP 的首款产品已经在开发中,预计于 2018下半年上市,让我们一起期待吧!

-

IC

+关注

关注

35文章

5525浏览量

173117 -

云计算

+关注

关注

38文章

7324浏览量

135598 -

物联网

+关注

关注

2865文章

41495浏览量

357931 -

大数据

+关注

关注

64文章

8621浏览量

136565

原文标题:为您量身定制的专属芯片了解一下~

文章出处:【微信号:mtk1997,微信公众号:联发科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

2024年全球与中国7nm智能座舱芯片行业总体规模、主要企业国内外市场占有率及排名

AMD硅芯片设计中112G PAM4串扰优化分析

如何克服PAM4调制的仿真挑战呢?

Cadence扩大TSMC N3E制程IP产品组合,推出新一代224G-LR SerDes IP,助力超大规模SoC设计

serdes串行发送和接收是怎么实现的?serdes就是用56G的ADC和DAC吗?

CIOE参展手札 | Samtec 224Gbps PAM4性能演示精彩亮相

R8C/56E 组, R8C/56F 组, R8C/56G 组, R8C/56H 组 数据表

IP_数据表(I-3):16Gpbs SerDes for TSMC 28nm HPC+

IP_数据表(I-4):16Gpbs SerDes for TSMC 28nm HPC

IP_数据表(I-1):Combo Serdes PHY for TSMC 28nm HPM

IP_数据表(I-5):SerDes PHY for TSMC 28nm HPC+

易飞扬再定义200G数据中心,新推出PAM4 DML的200G QSFP56 DR4/FR4光模块

联发科技推出 7nm 56G PAM4 SerDes IP,扩大 ASIC 产品阵线

联发科技推出 7nm 56G PAM4 SerDes IP,扩大 ASIC 产品阵线

评论