中国金融市场已经是全球最大的金融市场之一,随着市场规模的不断扩大,金融市场的功能发挥日益明显,服务相关产业和国民经济的能力不断提高。金融交易系统(例如股票交易系统)具有交易时间相对集中、交易指令和数据密集的特点,对交易系统处理速度具有很高的要求。近年来,资本市场的快速发展和算法交易技术(尤其是高频交易)在全世界范围内的应用,使得交易所在低交易延时领域面临着巨大的技术挑战。

交易所对于交易系统延时测量监控需求也越来越迫切,同时对于大规模数据密集型计算的实时性要求也越来越高。对于交易系统及环节的高精度延时测量,达到近实时的分析性能基本可以准确快速的监测股票交易系统性能和状态,但对于大规模实时交易数据分析,则需要达到更快的处理速度,实时性要求更高,直接关系到交易系统的服务质量(QoS)。传统的软件技术或以软件为核心的软硬件加速技术难以满足微秒级实时分析和实时响应的要求,采用FPGA专用硬件结构实现大规模数据密集型计算的并行加速称为提高交易系统服务质量的迫切需求。

针对金融网络数据处理的技术研究而言,国外已经预言或实现了很多相关硬件加速和并行计算的FPGA实现,其中Altera公司2008年面向蒙特卡罗算法(QMC)的FPGA加速模型建立,对价格衍生证券的实时精确估计判断做出了很大的促进作用。此外,2009年英国帝国理工学院和英国金融加速解决方案供应商Celoxica合作,提出实现了一种叫“低延迟交易数据反馈计算模型”。针对现在越来越大的交易市场的变化数据(甚至超过gigabit),他们为投资者提供了网络传输数据分析的FPGA加速处理方案,利用FGPA的可配置特点,可选择地实现对交易数据的压缩,过滤,筛选。其性能优越,每秒最多处理高达3.5M条信息,处理延迟也控制在微秒量级上。不但激活了投资者的投资热情,同时也极大促进了金融市场流动性。

基于FPGA的硬件以太网协议跨层解析

在数据分析获取过程中,以太网的协议解析占据了很大的时间比例。如果采用一般的软件解包方法,时间一般延迟包括每一网络层的解包时间和中间数据的传输时间,时间延迟可达毫秒级甚至更高。考虑到降低整个系统的数据传输延迟,进而提升处理性能,提出以下两种解决方案。

使用FPGA集成的可配置IP核。FPGA的IP核基于硬件原理实现,在数据传输延迟和网络数据解包能力上都大大优于传统的软件处理过程,而且极大缩短了开发周期,其可靠性,可配置性,通用性都相当出色。适合在项目的中前期作为数据输入的模拟测试。但是具体面向此项目IP核也会有自身的冗余,在MAC层不能进行自定义的协议解析,总的延迟大约在几十微秒至几百微秒。

针对本应用设计基于跨层解析的以太网数据分析模型。由于套利计算的数据源的包格式固定,封装简单,而且属于旁路数据,完全可以自行设计针对本应用的专用数据解析功能部分,方案优势和创新点在于在MAC层跨层解析数据以及包过滤,数据接收与解析时间重叠。采用状态机逐层进行包过滤,在有限机器周期内便可获得需要计算的数据,时间延迟可控制在微秒级。

基于FPGA的硬件以太网协议跨层解析能够降低传统软件协议栈的数据包处理固有延迟(可能占据整个延迟的80%以上开销),大大提高数据获取和预处理效率。

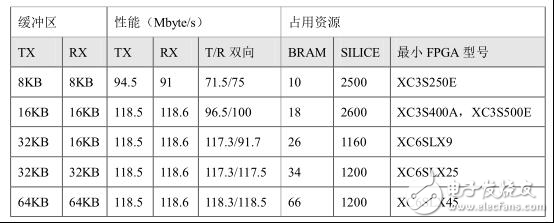

基于 FPGA 的千兆 TCP 硬协议栈,实现 TCP 与 FIFO 之间的数据连接,内部集成了千兆以太网 MAC 层,ARP 处理,TCP 处理等功能。RGMII 接口,直接连接 PHY 芯片,10/100/1000M 自适应。自动迅速的 ARP 响应。

硬逻辑的 TCP 协议栈,具有 listen 功能,可接受 1 个 TCP 连接,完整的三次握手建立

连接(syn)、数据快速重传、保活(keepalive)、窗口调整、被动关闭(fin)等功能。 可设置 MAC 地址,IP 地址,端口号,超时时间,以用于实时性高的场合可配置的缓冲区大小,以满足不同成本和性能的应用。

数据输入和数据输出为 FIFO 接口,使用独立的时钟。

适用于 xilinx 的 FPGA,spartan-3 系列,spartan-6 系列,virtex-4/5/6/7 系列不同配置的性能。

实时金融指数行情计算模型与并行调度策略

研究实时金融指数(本计划书以股票ETF50为例)股票推导的计算模型与计算方法,根据数据计算类型的特点设计专用硬件处理单元的结构模型;

研究有限计算资源条件下的行情数据缓存与并行调度策略,研究硬件计算资源划分与共享技术;

研究透明数据接口技术,包括输入端旁路高速数据获取技术与实现方法以及输出端的应用接口技术。

基于FPGA的并行加速技术

研究基于FPGA的硬件千兆以太网数据获取技术,实现完全硬件的TCP/IP协议栈解析和数据包过滤;

研究行情驱动的大规模专用套利数据处理单元结构、数据缓存与并行分发机制以及数据流水调度算法。

研究面向同构计算单元(同种计算模型)和异构计算单元(异种推导模型)协同的FPGA资源划分技术,对资源进行优化配置,在有限计算资源条件下获得最高的并行加速性价比。

实时金融指数行情的可配置与可扩展技术,充分考虑FPGA专用逻辑特点提供计算模型的配置与合约推导的扩展方案。

研究实时金融指数行情数据的高速分发及应用接口技术,采用高速传输总线结构实现实时金融指数行情数据的提取和管理。

基于FPGA的并行加速技术方案

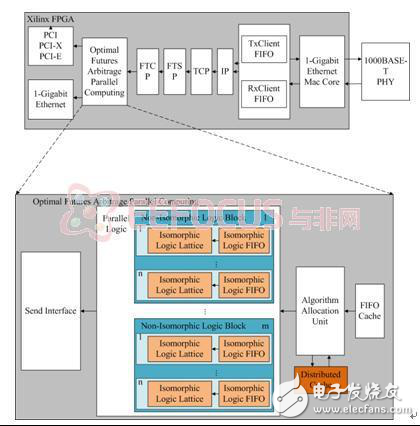

图为系统结构图,主要由数据接收模块、股票信息并行处理模块、数据发送模块组成。数据接收模块主要负责协议包的跨层解析以及包过滤。股票信息并行处理模块是整个系统的算法核心,采用高速并行方式分析股票信息,计算相关指数,并通过数据发送模块快速发布。在股票信息并行处理模块中,算法定向单元负责调度下层的异构逻辑块,异构逻辑块通过同构逻辑晶格完成最基础的数据计算。在股票信息并行处理模块中,将所有的数据存储于FPGA内部的分布式RAM中,突破了IO传输的瓶颈。

图7 FPGA计算系统结构图

北京太速科技有限公司 一直致力于大数据智能计算平台产品开发。基于 FPGA的微秒级实时金融平台 欢迎参与合作。

来源:北京太速科技有限公司

-

FPGA

+关注

关注

1601文章

21296浏览量

593083

发布评论请先 登录

相关推荐

FPGA图书分享系列-2024.01.31

通信中的调制指数具体怎么计算?

新手求推荐入门级的fpga板子

数字货币交易系统中的货币资产指数详解

请问怎么在ucosII中实现微秒级的延时?

HAL库微秒级的延时实现

基于windows仿真光学遥感微秒实时通信

基于windows仿真光学遥感微秒实时通信

基于FPGA与PCI总线的实时控制计算机的设计

4通道光耦 PS2801-4(NEC2801-4), 2011年价格行情指数

4通道光耦 PS2801-4(NEC2801-4), 2011年价格行情指数

基于FPGA微秒级实时金融指数行情计算

基于FPGA微秒级实时金融指数行情计算

评论