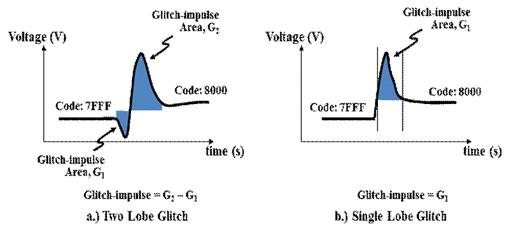

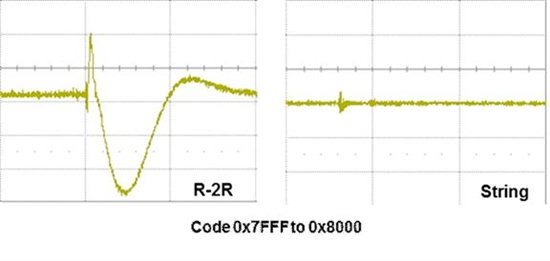

在使用数模转换器 (DAC) 进行设计时,您肯定希望输出能够从一个值向另一个值单调转换,但实际电路并不总是以这种方式工作的。在某些特定代码范围内出现过冲与下冲(即干扰脉冲)也很平常。这些脉冲会以这两种形式中的一种出现,如图 1 所示。

图1:DAC 干扰行为

图 1a 是一种可产生两个代码转换误差区的干扰,在R-2R 高精度 DAC中很常见。图 1b 是单波瓣干扰脉冲,在电阻串 DAC拓扑中较常见。干扰脉冲可通过能量测量进行量化,单位常为每秒纳伏 (nV-s)。

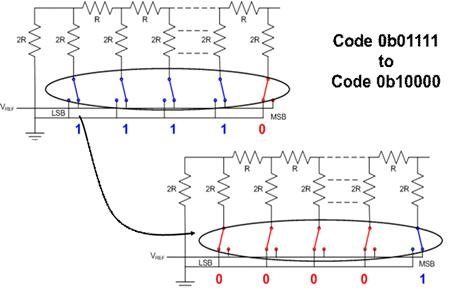

在讨论 DAC 干扰源之前,我们必须先给“主要进位转换”这个术语下定义。主要进位转换是指因较低位 (LSB) 转换而造成最高有效位 (MSB) 发生变化的单个代码转换。0111 到 1000 或 1000 到 0111 的二进制代码转换就是主要进位转换的具体实例。可将其看作是大多数开关的反相。这也是干扰最常见的地方。

两个需要注意的地方是多个开关同时触发时的开关同步与开关电荷转移。为了便于讨论,我们需要看一下设计旨在依赖开关(可在代码转换过程中同步)的 R2R 电阻串 DAC,如图 2 所示。

图2:DAC 主要进位转换

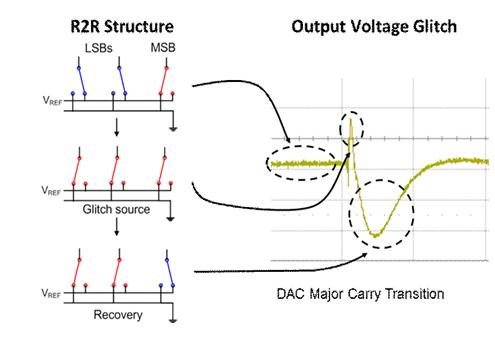

我们都知道完美同步是不可能实现的。开关过程中的任何变化都会导致所有开关在短时间内处于或高或低的切换状态,造成 DAC 输出误差。恢复之后,开关电荷将在趋稳之前创建一个反向波瓣。

因此,让我们来看一下主要进位转换过程的三个阶段以及 DAC 输出响应情况,如图 3 所示。

图3:转换过程中的 DAC 输出

-

代码转换前的 DAC 初始阶段。我们看一下本例中代表二进制代码 011 的 3 个 MSB。

-

DAC 输出进入主要进位转换后,会导致所有 R-2R 开关短时间接地。

-

短期开关电荷注入之后,DAC 恢复,同时输出开始趋稳。

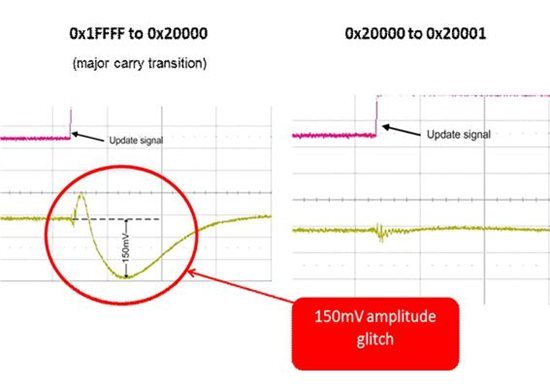

通过比较主要进位转换与非主要进位转换的输出干扰(如图 4 所示)可以证明, 开关同步是其主要原因。

X 轴标度是 200ns/div,Y 轴标度是 50mV/div。

图4:R-2R DAC 输出干扰

到目前为止,我们已经了解了 R-2R DAC 架构中的干扰现象,证明开关同步是产生干扰的主要原因。但当我们了解电阻串 DAC 的干扰时发现事情并非完全如此。在设计上,它会接入电阻器串上的不同点来产生输出电压。在不进行多重开关的情况下,不仅脉冲幅度比较小,而且主要由数字馈通控制。图 5 是进行相同主要进位代码转换时,R-2R DAC 与电阻串 DAC 拓扑的对比。

图5:R-2R 与电阻串 DAC 的输出干扰对比

理解干扰产生的原因有助于您确定设计方案是否能够承受这类短暂脉冲。未来几周内我将介绍一些帮助降低干扰的方法。

如欲了解有关电阻串及 R2R DAC 的更多详情,敬请在这里查看模拟线路上DAC 基础知识系列以前发布的这类博客文章。

-

信号干扰

+关注

关注

0文章

91浏览量

45747 -

数模转换器

+关注

关注

13文章

741浏览量

82425

发布评论请先 登录

相关推荐

STM32 IAP升级,KEIL如何一份代码运行于两个APP区?

一种有效的可转换的认证加密方案

【连载笔记】信号完整性-电磁干扰和两个重要结论

两个转换器同步方法和整合多个转换器

怎样去构建一种包含STM32H745两个内核代码的二进制图像呢

差分电路两个输入端之间加一个电容可起到什么作用?

所有这些干扰是怎么回事?

所有的这些干扰是怎么回事?

一种可产生两个代码转换误差区干扰分享

一种可产生两个代码转换误差区干扰分享

评论