公司演示了FPGA业界首项计划在 7nm 产品应用的112G PAM4 收发器技术,并宣布 Virtex UltraScale+ 系列新增 58G PAM4 FPGA 产品

赛灵思公司今天宣布在 2018 年美国光纤通讯展览会及研讨会(OFC 2018)上展示了其在光纤网络上的技术领先优势。公司通过FPGA 行业突破性的 112G PAM4 光纤网络电气信号传输技术的首次演示,以及 16nm Virtex® UltraScale+™ 系列新增带有 58G PAM4 收发器器件系列的宣布,让与会者一睹了未来网络技术的风采。

云服务和5G 的推出驱动数据流量大幅增长,这为满足网络中迅速增长的带宽需求带来了挑战。要想以高性价比满足带宽需求,路由器和交换机的线路卡端口密度、光学标准的演进发展以及光学网络带宽升级都是面临的主要约束。向58G和112G收发器的过渡,是在相同的现有空间上实现400G和800G+数据速率的重要一步。

112G PAM4技术演示—赛灵思定义新一代产品性能

赛灵思预见到对速度和吞吐量的需求将进一步增长,因而其在单个通道上演示了全双工 112G PAM4 信号传输方案。业界专家认为 112Gb/s的收发器性能对满足新一代光纤网络和线路卡密度的要求至关重要。客户将在赛灵思即将推出的 7nm产品系列看到采用 112G 收发器的可编程器件。

Moor Insights & Strategy 的 高性能计算( HPC)和机器学习高级分析师 Karl Freund 表示:“赛灵思在推动标准工作以及串行互连技术性能突破方面有着悠久的历史,今天更是通过业界首个112G PAM4的演示以及58G PAM4解决方案的推出,持续推动着这项事业。对于面临着光纤网络带宽性能提升挑战的网络架构师而言,赛灵思今天宣布的消息乃是一次重大的飞跃。”

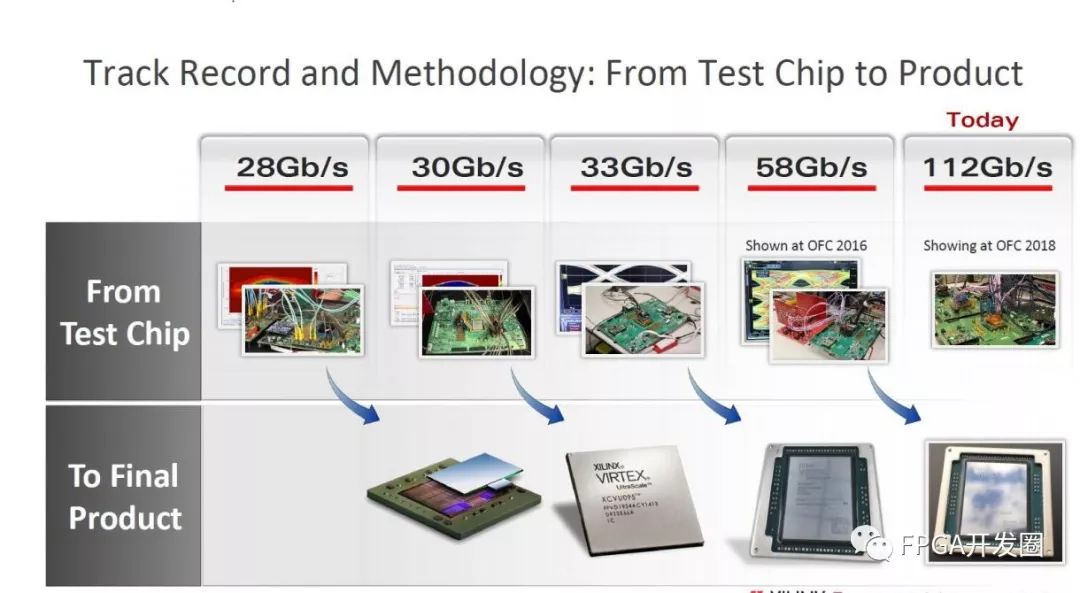

赛灵思收发器技术里程碑

全新 58G PAM4 FPGA—客户今日起即可展开设计工作

全新赛灵思收发器架构构建在高端应用领域炙手可热的 Virtex UltraScale+ 系列器件之上,能将编程逻辑的灵活性与 58G PAM4 收发器完美结合在一起,从而帮助客户高效地将现有系统的带宽水平提高一倍。上述器件能在现有25G背板上工作,不仅能延长当前系统的使用寿命和扩展带宽,同时还可为新一代技术发展铺平道路。就技术移植而言,采用 58G 收发器的新器件可与现有 Virtex UltraScale+ 量产器件在占位面积上相兼容。

最新收发器架构的目标应用为云计算、5G 网络、核心网络(OTN、以太网)以及网络功能虚拟化(NFV)等,可帮助厂商以简约紧凑的系统设计实现 50G、100G 和 400G 端口以及 Tb 级接口的规模进行扩展。

赛灵思通信市场副总裁 Farhad Shafai 表示:“网络发展日新月异,需要支持更快速、更灵活和适应性更强的系统,而业界也在为预期中的新型光纤器件与标准的发展变化积极做好准备。我们很高兴能为我们的客户交付最灵活和适应性最强的解决方案以及经生产实践验证的芯片,同时延续一贯保持的高品质,并与光学、背板及其它关键技术所构成的生态系统密切合作。”

全新 58G PAM4 Virtex UltraScale+器件,整合了新一代互联所需的集成型PAM4收发器、100GE IP模块以及所有相关的前向纠错编码(FEC)技术。

赛灵思宣布16nm Virtex® UltraScale+™ 系列新增带有 58G PAM4 收发器器件系列

-

收发器

+关注

关注

10文章

2966浏览量

104708 -

光纤网络

+关注

关注

0文章

122浏览量

17599 -

5G

+关注

关注

1340文章

47793浏览量

553878

原文标题:Xilinx 面向未来光纤网络的突破性技术与产品亮相OFC 2018

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Achronix的FPGA有哪方面的优势?

AMD推出全新Spartan UltraScale+ FPGA系列

AMD 扩展市场领先的 FPGA 产品组合,推出专为成本敏感型边缘应用打造的AMD Spartan UltraScale+ 系列

AMD推出Spartan UltraScale+ FPGA系列产品

AMD 扩展市场领先的 FPGA 产品组合,推出专为成本敏感型边缘应用打造的AMD Spartan UltraScale+ 系列

AMD推出全新Spartan UltraScale+ FPGA系列

针对UltraScale/UltraScale+芯片DFX应考虑的因素有哪些(2)

使用加密和身份验证来保护UltraScale/UltraScale+ FPGA比特流

UltraScale和UltraScale+ FPGA封装和管脚用户指南

Virtex UltraScale+ FPGA数据手册:DC和AC开关特性

适用于Xilinx Ultrascale+ FPGA的PMBus稳压器参考设计

Virtex UltraScale+ 系列新增 58G PAM4 FPGA 产品

Virtex UltraScale+ 系列新增 58G PAM4 FPGA 产品

评论