我知道,我对与电子有关的所有事情都很着迷,但不论从哪个角度看,今天的现场可编程门阵列(FPGA),都显得“鹤立鸡群”,真是非常棒的器件。如果在这个智能时代,在这个领域,想拥有一技之长的你还没有关注FPGA,那么世界将抛弃你,时代将抛弃你。

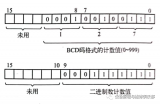

FPGA中计数器设计探索,以计数器为32位为例:

第一种方式,直接定义32位计数器。

reg [31:0]count;

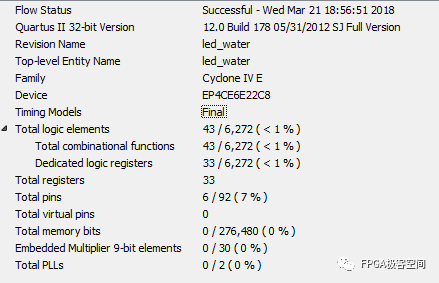

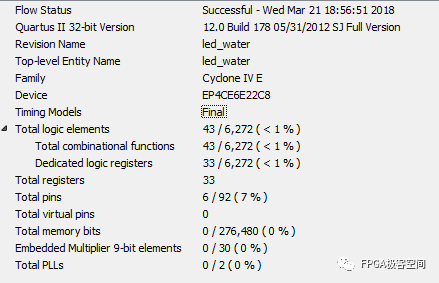

quartus ii 下的编译,资源消耗情况。

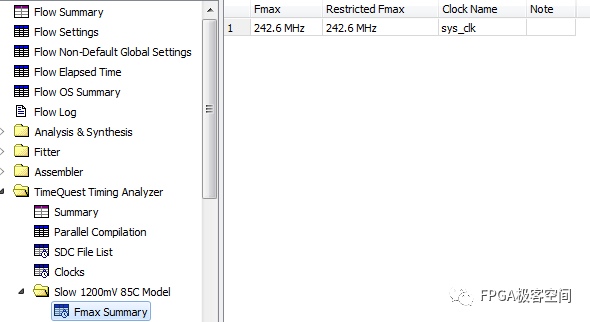

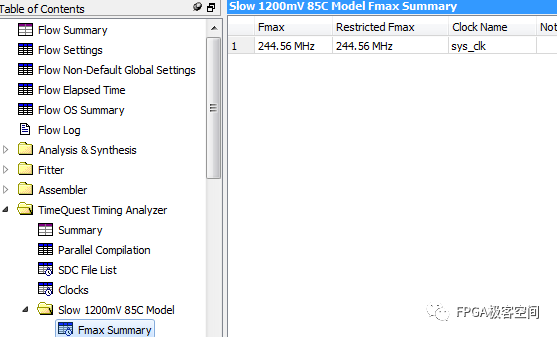

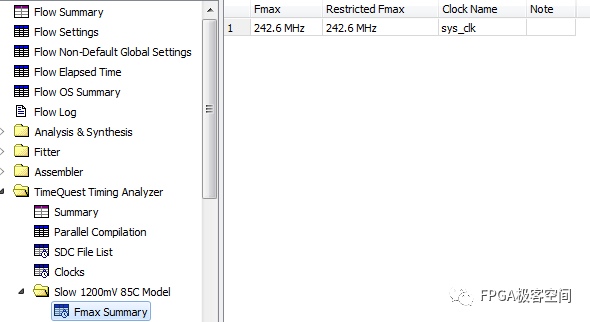

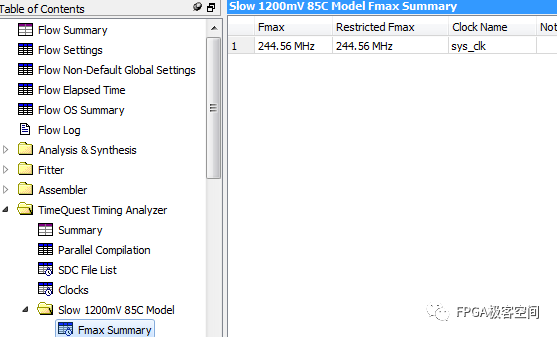

85C模型下的时钟频率。

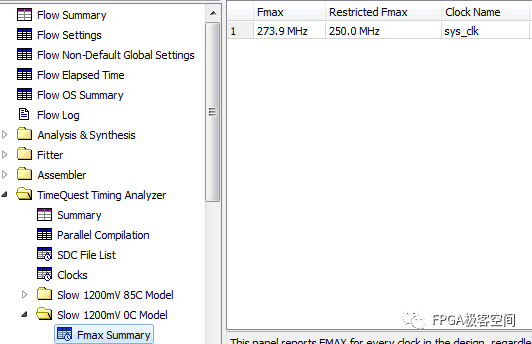

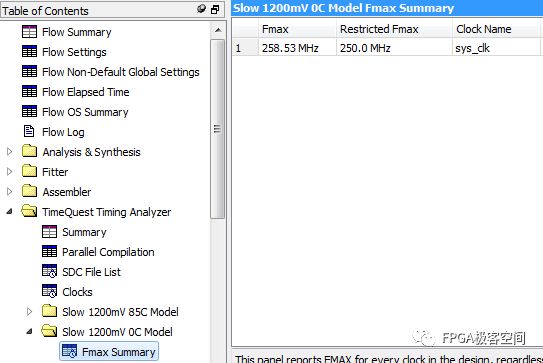

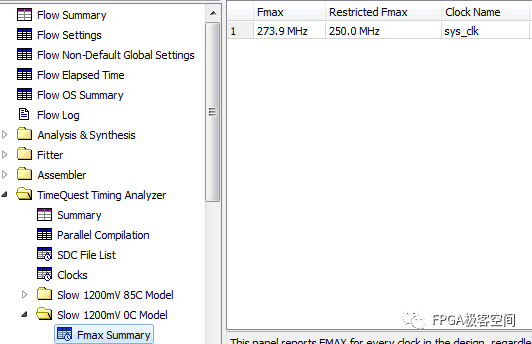

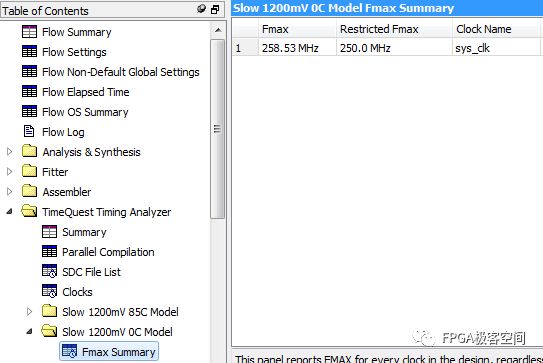

0C模型下的时钟频率。

chip planner下资源分布情况。

第二种方式,定义2个16位计数器。

reg [15:0]count1,count2;

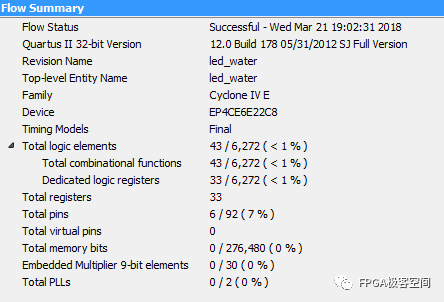

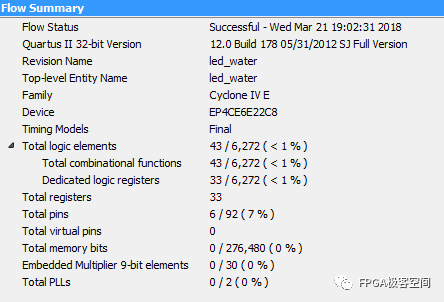

quartus ii 下的编译,资源消耗情况。

85C模型下的时钟频率。

0C模型下的时钟频率。

chip planner下资源分布情况

从上述两种情况来看,结合C4内部LAB的结构,两种方式消耗资源一样多,两种模型下的时钟频率比较接近。

值得注意的是,以上测试是在资源足够频率不高的条件下测试的。根据经验,当资源使用较多,时钟频频较高时,建议使用方式二。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

原文标题:FPGA中计数器设计探索

文章出处:【微信号:ALIFPGA,微信公众号:FPGA极客空间】欢迎添加关注!文章转载请注明出处。

相关推荐

计数器是计算机领域中常用的一种数据结构,用于记录和控制程序执行中的指令或事件发生的次数。计数器可以根据同步机制或异步机制进行操作。本文将详细讨论计数器的同步性和异步性,深入探讨两者的区别及其在实际

![的头像]() 发表于

发表于 02-22 15:14

•476次阅读

计数器是一种被广泛应用于各个领域的实用工具,在我们的日常生活中随处可见。无论是进行时间统计,协助工作任务的完成,还是用于科学研究和编程技术,在各个领域都起到了重要的作用。本文将详细介绍计数器

![的头像]() 发表于

发表于 02-03 10:04

•1196次阅读

雷击计数器的基本原理是利用雷电流通过导线时产生的感应电压或电流来驱动计数器的计数。根据计数器的类型,可以分为机械式雷击计数器和电子式雷击

![的头像]() 发表于

发表于 01-31 09:50

•154次阅读

我定期抽样看门狗计数器(例如,每个1 毫秒),以验证看门狗的有效性。

监视器计数器必须定期重设(例如,每1000 毫秒),以防止中断或PSoC 重设。

看门狗

发表于 01-29 08:16

避雷器计数器怎么归零 避雷器计数器是用来监测避雷器的使用情况的一个设备,通常用于记录避雷器的工作次数和剩余容量。归零避雷器计数器是为了实时监测避雷器的状态以及及时更换避雷器,以确保设备的正常运行

![的头像]() 发表于

发表于 12-20 15:16

•626次阅读

同步计数器和异步计数器是两种常见的数据结构,它们都用于控制对共享资源的访问。它们的主要作用是实现多个线程之间的同步和并发控制。尽管它们都被用于同步的目的,但它们有很多不同的特点和用例。 同步计数器

![的头像]() 发表于

发表于 12-15 10:49

•639次阅读

4017计数器是一种广泛应用于数字电路中的集成电路,它可以用来计数和控制电子设备。4017计数器有10个输出引脚,可以依次输出从0到9的十个数字,因此也被称为“十进制计数器”或“分频

![的头像]() 发表于

发表于 12-15 09:24

•1207次阅读

同步计数器和异步计数器的区别详解 同步计数器和异步计数器是数字电路中两种常见的计数器类型,它们在实现方式和功能上存在明显的区别。本文将详细介

![的头像]() 发表于

发表于 12-13 14:54

•2437次阅读

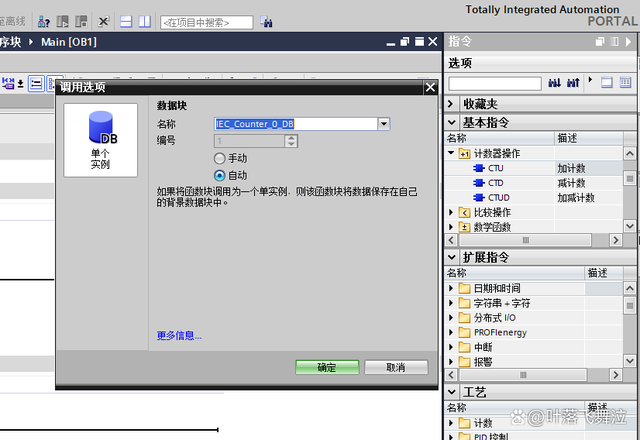

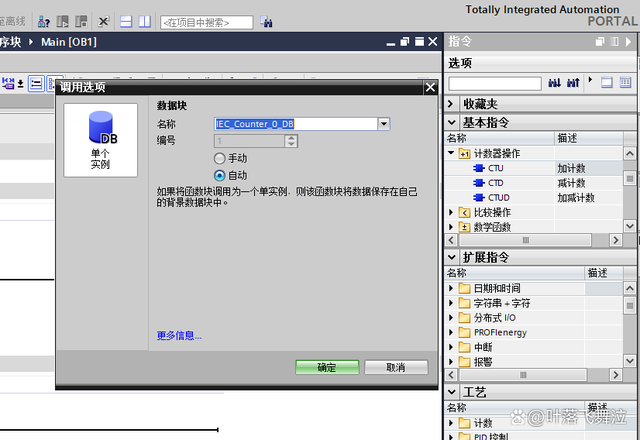

基本指令里面找到计数器操作,点击加计数

![的头像]() 发表于

发表于 11-08 17:22

•1101次阅读

盖格计数器是一种核探测器,能够通过某种间接方法检测不同类型的核辐射,例如α粒子、β粒子和伽马辐射,在某些情况下还可以检测中子。这种盖格计数器所基于的原理非常有趣,但在我们深入讲解之前,让我们先讨论这种计数器的结构。

![的头像]() 发表于

发表于 08-28 16:48

•636次阅读

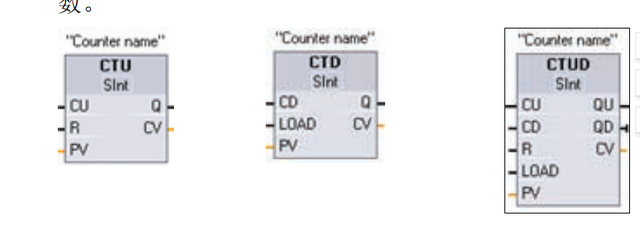

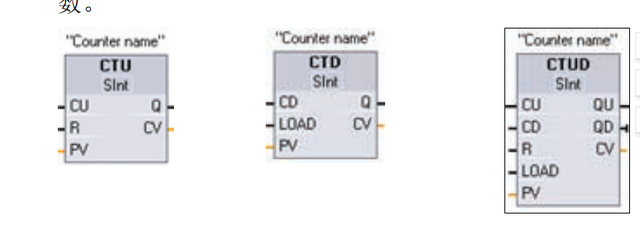

PLC程序除了梯形图之外,还有FBD功能块作为指令,这种指令一般都有背景DB。

PLC计数器指令可使其对内部程序事件和外部过程事件进行计数。这样就可以节约外部计数器的使用。

每个

![的头像]() 发表于

发表于 07-04 15:57

•1000次阅读

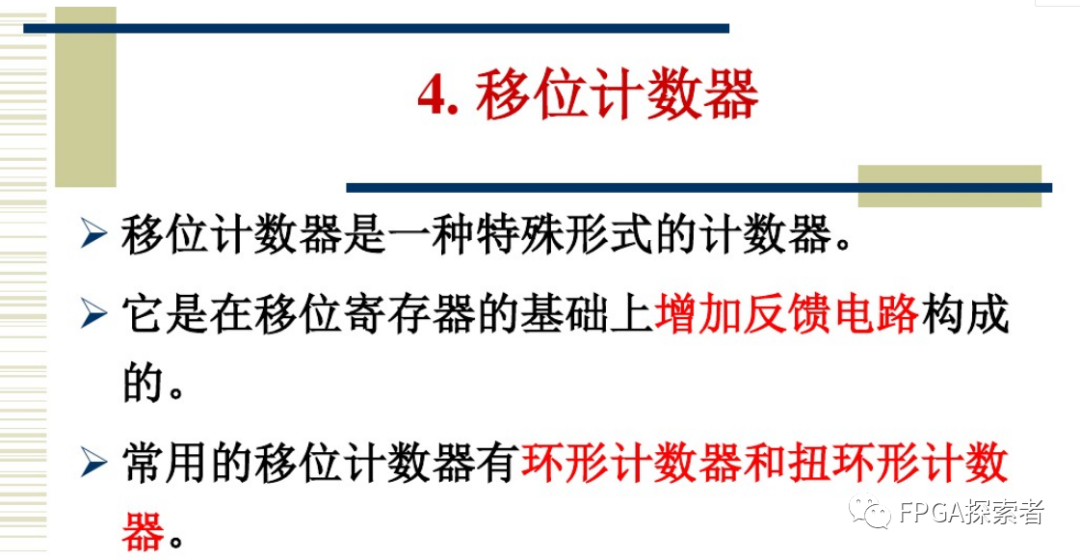

扭环形计数器,每次状态变化时仅有一个触发器发生翻转,译码不存在竞争冒险,在n(n≥3)位计数器中,使用2n个状态,有2^n-2n个状态未使用;

![的头像]() 发表于

发表于 06-27 10:18

•1466次阅读

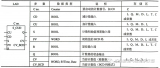

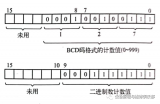

计数器的功能是完成计数功能,可以实现加法计数和减法计数,计数范围是0~999.计数器有三种类型:

![的头像]() 发表于

发表于 05-04 09:59

•4923次阅读

加计数器(S_CU)在计数初始值预置输入端S上有上升沿时,PV装入预置值,输入端CU每检测到一次上升沿,当前计数值CV加1(前提是CV 小于999);当前计数值大于0时,Q输出为高电平

![的头像]() 发表于

发表于 04-27 15:38

•1674次阅读

计数器的功能是完成计数功能,可以实现加法计数和减法计数,计数范围是0~999.计数器有三种类型:

![的头像]() 发表于

发表于 04-27 15:38

•902次阅读

以计数器为32位为例:FPGA中计数器设计探索

以计数器为32位为例:FPGA中计数器设计探索

评论