在本辑的“秒懂时钟”文章中,我想继续上期关于时钟相位噪声测量中杂散的讨论。上次我们说道,时钟相位噪声图中的杂散信号是离散频率分量。杂散通常很少且幅度较低,但通常不受欢迎,因为它们会影响时钟的总抖动。

然而,杂散也可以用于时序设备的评估和表征。我们可以使用配置为低电平调制的实验室信号源将直接或间接的频率分量作为输入激励应用于时钟设备或系统。然后用频谱分析仪或相位噪声分析仪测量得到的输出时钟杂散。

在这篇文章中,我将简要回顾一下适合的信号调制选项。接下来我将讨论一些值得注意的测量。最后,我将给出选择示例的结果,抖动传输。欢迎往下阅读或点击“阅读原文”至Silicon Labs中文社区观看完整文章。

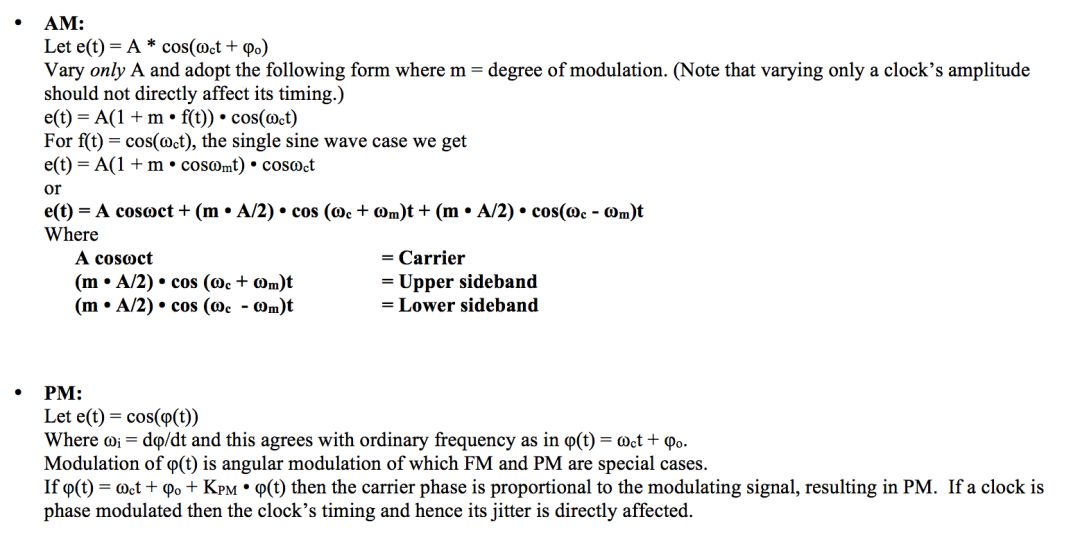

调制选择,既不是所有杂散都是相等的大多数实验室级别的发生器有三种基本的模拟调制选项,即AM,FM或PM,分别指的是调幅,调频和相位调制。每个人都在我们的“ spur toolbox ”中占有一席之地。但首先,考虑下面的每个频谱分析仪屏幕大小。该载波标称为100MHz,并且在距载波100kHz偏移的每一侧有一对对称的杂散信号。每个杂散距离载波约60dB。

你能告诉哪个屏幕上限对应于AM,FM或PM吗?不,不是,没有额外的信息。在这个特定的例子中,图像按字母顺序排列。

那么,为什么他们很难区分呢?有几个原因:

-

频谱分析仪只测量光谱的振幅,而不测量相位。在这个意义上,它就像一个电压表。请参阅Keysight Technologies的Spectrum Analysis Basics应用笔记。

-

FM和PM都是角度调制方法,它们的行为方式相同,只是其调制功能不同。 FM信号可以产生PM,反之亦然。

-

最后,在低调制指数下,AM,FM和PM边带振幅看起来非常相似。

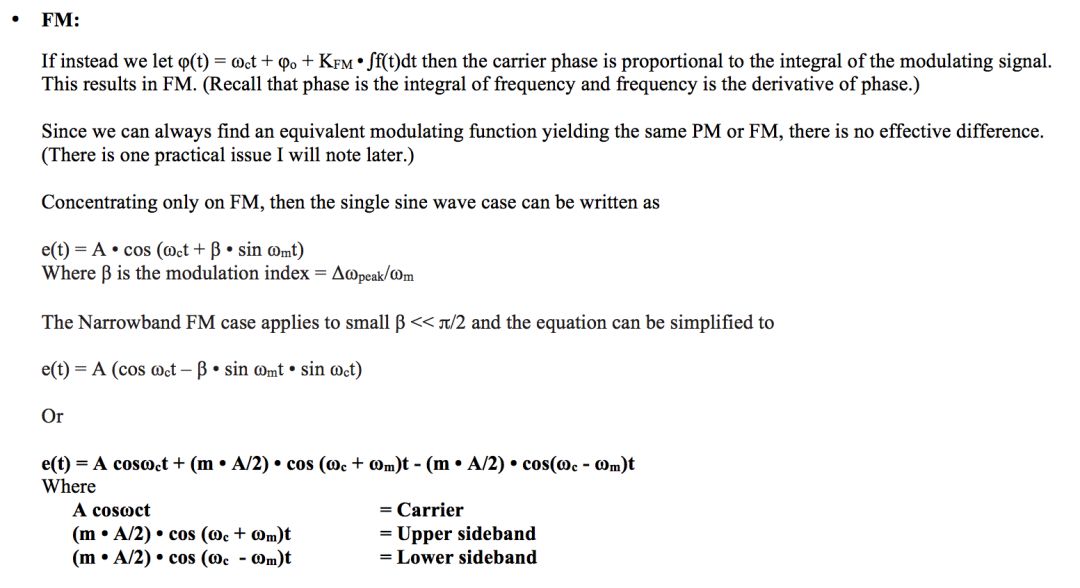

我们来看看最后几点的细节。Keysight Technologies的Spectrum Analysis Amplitude and FrequencyModulation(https://literature.cdn.keysight.com/litweb/pdf/5954-9130.pdf)应用笔记中附录了以下关系。

注意:这些FM组件与AM的大小相同,但与AM不同,在下边带前有一个负号。但是,由于频谱分析仪不保存相位信息,因此低调制AM,FM和PM组件看起来相同。

通常,AM,FM或PM的SSB或单边带杂散与载波比率是20 * log10(调制指数/ 2)。例如,给定200 Hz峰值频率偏差和100 kHz频率调制,我们预计SSB杂散如下:

SL = 20 log10 {(200/2)/100E3} = -60 dBc

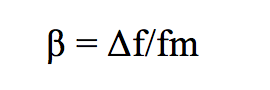

现在,这里是使用FM与PM的实用方面。如果您的信号源支持PM,那么您可以直接输入峰值相位调制量。当您逐步调整频率或刺激偏移频率时,无需更改此设置。但是,如果您的信号源仅支持FM,则必须按照以下关系维护频率调制指数。

在这种情况下,您需要调整峰值频率偏差Delta-f以及调制频率fm以保持Beta恒定。

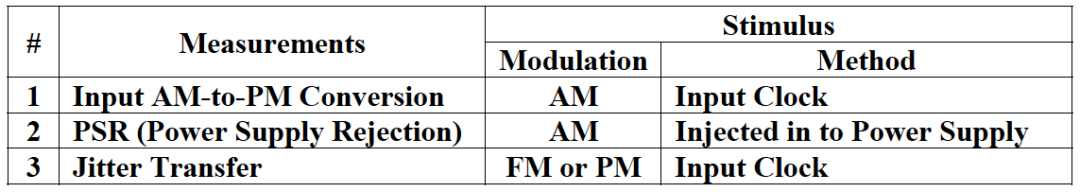

那么,我们可以用调制杂散进行哪些测试通常,我们将使用频谱分析仪或相位噪声分析仪来测量频域中的输出时钟杂散。我们选择不同的调制方法,这取决于我们需要对系统应用哪种激励。下表总结了一些值得注意的测量。我将简要地讨论这些测试中的每一个,然后更详细地关注最后一个测试。

您会注意到FM或PM可用于生成抖动传输测试的输入时钟杂散。唯一需要跟踪的是相位或频率调制指数。现代AWG(任意波形发生器)通常支持AM,FM和PM。更高频率的射频和微波信号发生器也至少支持FM。

这里是关于表中提到的每个测试的更多细节。

输入AM到PM转换高增益设计良好的时钟缓冲器将倾向于抑制AM并且仅通过相位(定时)误差。然而,没有输入时钟缓冲器是完美的,并且可以发生一些AM-PM转换。这种转换的机制和数量通常会根据调制频率而有所不同。

该测试的设置是直接进行的,即将输入时钟与AM一起使用,然后在幅度调制频率处检查输出时钟杂散偏移。进行这种测试时需要注意几点注意事项:

-

保持低的调制指数,因此实际上只有一个边带刺激的后果。

-

改变感兴趣区域的调制频率。

-

在频谱分析仪或相位分析仪的输入端使用限幅器,以便我们不必担心仪器中的AM到PM转换。

PSR或电源抑制类似于之前的测试,因为应用了AM。但是,在这种情况下,它不是调制的输入时钟。相反,AM通过电源间接引入,然后像以前那样刺激测量。这种类型的测量还通过其他名称,如PSRR(电源抑制比)或电源纹波测试。

除了早先的AM-PM注意事项之外,还有其他一些:

-

如果可能,我们通常要移除所有旁路电容。这消除了一个变量,并且更容易注入固定的幅度波动,例如,在感兴趣的频率范围内进入电源干线100 mVpp。比较设备时也比较公平。

-

AM需要注入电源而不会影响仪器或其他系统组件。我们通常为此使用偏置式Tee。

-

一致性对低水平杂散测量很重要,因此在比较设备时尽量保持设置相同。

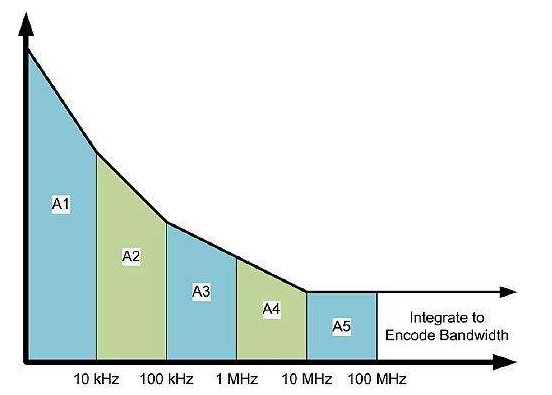

检查时钟PLL芯片传输曲线的一种相对快速的方法是应用低电平PM或FM杂散信号,并将调制偏置频率从远低于预期环路带宽的地方调到远远高于它。然后使用相位噪声分析仪,启用Max Hold,您将看到施加的杂散是如何滚降的。杂散幅度的渐近线允许我们估计环路带宽。

您可以通过查看相位噪声来了解发生了什么,但使用固定的调制索引输入时钟可以更精确地测量传输函数。下面的两个屏蔽帽是对Si5345抖动衰减器应用相位调制的25 MHz输入时钟(0.2°相位偏差),并在最大保持时间内连续测量相位噪声,以获得100 MHz的输出时钟。

在下面的第一种情况下,DSPLL带宽设置为400 Hz。如预期的那样,该图显示注释的渐近线在400Hz左右相交。拐角频率附近的滚降略高于30 dB / dec。

在下面的第二种情况下,DSPLL带宽设置为4 kHz。这次曲线显示注释的渐近线相交于4.5 kHz左右,比标称目标稍宽。这里转角频率附近的滚降看起来接近25dB / dec。

使用Max Hold功能可以让我们进行手动测量。然而,我们可以使用平均和存储运行集合中的杂散幅度来进行更仔细的测量,以准确表征DUT的环路带宽。

与往常一样,如果您有建议,或者有问题想要回答,请发送邮件至kevin.smith@silabs.com,并在主题行中添加Timing 101字样。

-

电源管理

+关注

关注

112文章

6013浏览量

141101 -

频谱分析仪

+关注

关注

15文章

941浏览量

84869 -

相位噪声

+关注

关注

2文章

150浏览量

22644

原文标题:秒懂时钟Part 7: 探讨时钟相位噪声测量中的杂散(下篇)

文章出处:【微信号:SiliconLabs,微信公众号:Silicon Labs】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

相位噪声定义 相位噪声来源 相位噪声对信号的影响

低相位噪声晶振选型,应该从何入手?

AD9467采集信号的杂散如何消除?

请问2个AD9576之间怎么实现同步来保证16个AD输出时钟相位都同步?

AD9164杂散问题如何解决?

AD7606 SPI通信的时钟极性和时钟相位要求是什么?

HbirdV2-SoC中如何配置QSPI1和QSPI2的时钟极性CPOL和时钟相位CPHA?

SPI时钟极性和时钟相位

时钟相位噪声测量中杂散的讨论及应用

时钟相位噪声测量中杂散的讨论及应用

评论