本文探讨了使用MSP430F5xxx实现ETC系统中实时HDLC编解码的方法。MSP430F5xxx是TI公司MSP430家族最新产品序列,采用先进的0.18工艺,1MIPS消耗的电流低到了惊人的160uA。同时,F5xx产品都配备了高效灵活的DMA模块,对16bit数据进行搬移只需要2个时钟周期。本文给出了结合F5xx的DMA,TimerA,CRC16及SPI,实现几乎实时的HDLC FM0软解码办法和利用SPI的便捷的FM0编码方法。本文包括相关的两个实例代码。

MSP430介绍

TI公司的MSP430 单片机产品系列具备16-bit RSIC架构,超低功耗。作为MSP430最新产品序列,F5xxx首次采用0.18um工艺,1MIPs消耗的电流低到了惊人的160uA,主频达到25MIPs 。同时,MSP430F5xxx提供了丰富的片上功能模块,例如,硬件的RTC,12-bit ADC,灵活的时钟系统,硬件CRC16,电源管理模块和多通道的灵活强大的DMA,支持待机模式下的数据交换。

高速公路不停车收费系统(ETC)介绍

不停车收费系统(又称电子收费系统Electronic Toll Collection System,简称ETC系统)是利用RFID技术,实现车辆不停车自动收费的智能交通子系统。该系统通过路侧单元RSU(Road Side Unit)与车载电子标签之间OBU(On Board Unit)的专用短程通信,在不需要司机停车和收费人员操作的情况下,自动完成收费处理过程。

ETC车载单元结构

图 1. ETC OBU结构图

如图一所示,OBU由电池系统,MCU,射频,显示和读卡部分(ESAM卡,CPU卡,射频卡)组成。MCU作为整个系统的中心,负责管理显示,读卡以及与射频部分的数据处理及交换。

FM0编码方式介绍

在车辆通过收费站时,OBU和RSU通过5.8G的载波调制,进行高速的数据交换。数据采用HDLC FM0调制。FM0编码遵循以下三个规则:

A.一个周期内有电平跳变表示”0” ;

B.一个周期内没有电平跳变表示”1”;

C.相邻两个周期电平相反。

数据形式请参考图2

图 2. FM0编码方式

车载电子标签(OBU)对MCU的挑战

车载电子标签系统对MCU有两个挑战 。一是低功耗;二是高速数据通信能力。

车载电子标签的电池要求有5年以上寿命或者能够支持1万次以上交易。整个系统的低功耗设计成为工程师们的首要任务。其次,RSU对OBU下行数据波特率达到了256Kbps,上行数据波特率512Kbps。由于车辆通行时间非常短,需要OBU对RSU的数据和命令快速响应。而数据包最长能够达到1Kbits,不允许OBU收下整个数据包之后再解码,这要求MCU有实时编解码的能力。

一般情况下,对FM0的软解码需要得到数据的电平宽度,从而实现解码。通常有两种方式,一种是Timer捕获数据沿,然后软件在中断中判断数据沿之间的宽度。另外一种是定时采样数据口线的电平,通过计数方式得到电平宽度。ETC下行数据速率达到256Kbps,对数据“0”来讲,数据跳变沿之间的宽度只有2uS。对数据“1”来讲,数据沿宽度只有4uS。以第一种方式为例,传统的软解码方式过程如下:

图 3. Timer 捕获中断方式

如图2所示,数据接收过程中,Timer会每2uS或者4uS捕获到一个数据沿,并把数据沿保存到对应寄存器。所以,Timer捕获寄存器里的数据会最快每2uS更新一次。这就需要CPU速度足够快,能够在至少2uS之内完成解码过程。否则,Timer捕获寄存器的数据就会被新的数据覆盖掉,造成解码错误。假设MCU完成1个bit解码的时间需要50个cycle,那么至少需要MCU主频达到25MIPS以上才能实现实时解码。通常,我们会选取主频超过40MIPs的MCU,而这些高速MCU功耗往往难以满足ETC系统的要求。所以,很多ETC生产商采用双MCU的方式,由一颗高速MCU实现FM0实时编解码,另外还有一颗低功耗MCU,通常是MSP430来管理整个系统的功耗。这增加了系统的成本和复杂度。MSP430F5xxx的问世,能够同时满足ETC系统对MCU所有的挑战,解决了客户的困扰。

用F5xxx 片上DMA和TimerA捕获功能实现FM0实时解码的方法

MSP430F5xxx卓越的低功耗特性能够满足ETC OBU的低功耗要求。作为MSP430最新产品序列,F5xxx首次采用0.18um工艺,1MIPs消耗的电流低到了惊人的160uA,片上PMM(电源管理模块)让用户能够根据MCU负荷灵活调节核电压,确保功耗最低。另外,具备多种低功耗状态。在典型的LPM3模式下,打开RTC,RAM数据保持的情况下功耗仅为2uA。

除了卓越的低功耗特性外,MSP430F5xx主频虽然最高只能达到25MIPS,但由于有灵活的多通道DMA,能够与Timer联动,实现数据的自动搬移而不干扰到CPU,这极大的增强了MCU的数据吞吐能力,使主频不再成为瓶颈,而完成对FM0近乎实时的解码。另外,硬件的CRC16模块让MCU只需要操作寄存器就可以完成数据校验。利用DMA和CRC16的实时解码过程如图4所示:

图 4. DMA自动数据搬移的解码方式

数据接收过程中,Timer每2uS或者4uS捕获到一个数据沿,这时会自动触发DMA,DMA自动将Timer寄存器的数据搬移到RAM区的指定数组当中。整个数据接收过程不需要CPU的参与。有了DMA的存在,CPU就不需要频繁的进出中断去取数据,也不用担心Timer捕获寄存器数据的丢失,只需专注于解码过程。

图 5. FM0 DMA方式解码图示

解码过程说明:

1. 待机状态:TimerA配置成捕获模式,使能TimerA中断,等待数据到来

2. 捕获到第一个数据沿:在TimerA中断中使能DMA,使能TimerB及TimerB中断

3. 数据接收:DMA自动将后续的数据沿搬移到内存数组中;同时MCU解码

4. 数据结束:TimerB判断数据接收结束

5. 解码结束

图 6. 程序流程图

实测结果:

采用120bytes的数据做FM0解码测试,其中数据位”1”和“0”约各占50%。MSP430F5438完成解码后,通过串口输出数据如图7所示:

图 7. 串口接收到的数据

对上图1Kbits数据,实测MCU完成解码,滞后数据包接收完毕约220uS.如图8所示

图 8. 解码实时性

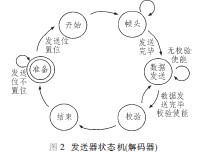

使用MSP430F5xx SPI及DMA实现FM0编码及发送的办法

ETC OBU系统MCU上行数据率是512Kbps。通过灵活应用片上DMA及SPI模块,可以方便的完成FM0数据发送

-

msp430

+关注

关注

178文章

2223浏览量

228525 -

车载电子

+关注

关注

0文章

53浏览量

17508 -

rsic

+关注

关注

0文章

2浏览量

2775

发布评论请先 登录

相关推荐

基于CPLD的CMI编解码电路的设计与实现

音频记录PCM编解码系统

求一种基于FPGA的HDLC协议编解码器设计方案

基于HarmonyOS编解码能力,实现Camera实时预览流的播放

H.264 便携式实时编解码器的设计

接口协议智能编解码方法研究

WTB网络HDLC在FPGA中的实现

用XC9572实现HDB3编解码设计

二维条码的编解码及系统实现

FFMPEG视频编解码流程 H.264硬件编解码实现

NANDFLASH快速BCH编解码算法及便件实现

实现ETC系统中实时HDLC编解码的方法

实现ETC系统中实时HDLC编解码的方法

评论