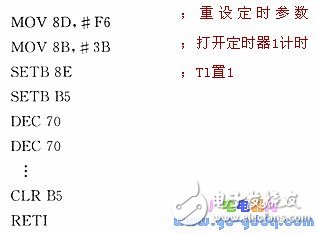

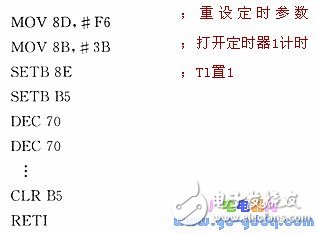

动态存储器的一个显著特点就是存储的数据具有易失性,必须在规定时间内对其刷新。在本系统中采用8031的定时器1定时中断实现对DRAM的刷新。其定时中断刷新的程序如下:

刷新时,先将Tl置1,在DEC 70H语句的取指周期,8031从外部程序存储器EPROM取指令,PSEN有效,此时Tl为高,使RAS有效;同时,存储指令的EPROM地址也送到了地址线上,其低9位也作为行地址同时送给DRAM,实现对DRAM -行的刷新。由于DEC 70H语句是对内部RAM的操作,此时地址线上不会有其他地址,连续执行OlOOH条DEC 70H语句(0200H个字节),可实现对1 MB DRAM的刷新(1 MB DRAM需9位刷新地址)。

进入中断程序,立即重设定时器1参数并打开定时器,使定时连续。定时器1的计数输入信号来自内部的时钟脉冲,计数速率是振荡器频率的1/12。若用12 MHz石英晶体作振荡器,则计数速率为1MHz。设定时参数为FFFFH - F63BH一09C4H,则定时刷新周期为2.5 ms。目前一般1 MB DRAM刷新周期为16 ms,所以定时参数值还可设置得大些。

数据缓存器管理

数据缓存器的管理可采用循环队列的方式。由主程序向上位机发送数据,并根据队列的头尾指针位置及前后标志判断队列的情况,利用中断接收新数据和刷新DRAM。这种边接收、边发送的运行方式可使缓存器保持高效率。刷新DRAM的中断源级别应高于接收数据的中断申请,以保证DRAM的按时刷新。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

相关推荐

一般来说DRAM芯片的工作原理,比SRAM要复杂。这主要是由于DRAM在存储数据的过程中需要对于存储的信息不停的刷新,这就成为

发表于 07-15 11:40

。 关键词:刷新控制单元(RCU) DRAM控制器 状态机 CPLD VHDL语言80C186XL16 位嵌入式微处理

发表于 02-24 09:33

分布电容里的信息随着电容器的漏电而会逐渐消失,一般信息保存时间为2ms左右。为了保存DRAM中的信息,必须每隔1~2ms对其刷新一次。因此,采用 DRAM的计算机必须配置动态

发表于 11-28 10:23

缓存控制概述 用户级别的Hexagon缓存管理指令可以在HVM用户下进行使用,如dcfetch, icinva,dccleaninva,dccleana,dcinva有些

发表于 09-20 10:19

使用NI的 FPGA,开辟了一个1294*1040大小的DRAM,在60HZ帧频下按地址一个MCK一个地址的刷新DRAM中的数据,也就是每个地址刷新

发表于 11-07 23:57

51单片机数码管动态显示程序,用三个7段共阴极数码管动态显示0~99,每隔0.5s刷新一次数字。用keil与Proteus联合仿真硬件设计以AT89C51

发表于 07-19 07:44

存储器是怎样进行分类的?分为哪几类?为什么要对DRAM进行刷新?如何进行刷新?

发表于 09-28 08:50

简要地写了如何使用51单片机控制动态数码管的过程,内含模块信息、源代码、原理图等。

发表于 11-18 06:03

片头因为环形缓存在单片机程序中的使用是非常有效的,非常有用的,关于这个话题在此专门开一文章来聊聊这个话题。环形缓存的用途主要是来缓存数据,而

发表于 12-06 08:29

本篇文章是为了记录flash,sram,dram,rom,ram在单片机等的应用ROM和RAM都是半导体存储器。ROM停止供电仍然可以保持数据,RAM掉电之后丢失

发表于 01-11 06:25

本文代码可以实现:上位机通过串口向单片机传输数据,单片机通过DMA将数据缓存到存储

发表于 01-20 07:28

提示。对于G.5.9.1中的单处理器系统,只有一个示例,没有数据高速缓存刷新操作。因此,在单处理器系统中,用于编写转换表条目的示例指令序列包

发表于 08-16 15:20

怎么用51单片机实现动态内存管理

发表于 10-15 12:43

读取一字节数据的程序段如下: 读取数据时,T1先置1,其后的RD信号将行地址送到地址线AB上,并使D。触发器锁存Tl,Q,变成低电平,使RAS有效(低电平),实现行选通;再置TO为l,其后的RD信号

![的头像]() 发表于

发表于 03-17 11:33

•7938次阅读

的作用。动态存储器DRAM具有容量大,价格低的特点,适合于数据量比较大的单片机应用系统;但其不足之处在于,必须在规定的时间范围内进行定时刷新

![的头像]() 发表于

发表于 03-17 11:36

•5639次阅读

单片机控制的动态数据缓存器DRAM刷新过程与管理

单片机控制的动态数据缓存器DRAM刷新过程与管理

评论