随着通信系统中的时钟速率迈入GHz级,抖动这个在模拟设计中十分关键的因素,也开始在数字设计领域中日益得到人们的重视。在高速系统中,时钟或振荡器波形的时序误差会限制一个数字I/O接口的最大速率。不仅如此,它还会导致通信链路的误码率增大,甚至限制A/D转换器的动态范围。有资料表明在3GHz以上的系统中,时间抖动(jitter)会导致码间干扰(ISI),造成传输误码率上升。

1时钟抖动(Jitter)的基本概念

抖动的定义为“信号的定时事件与其理想位置之间的偏差”。用SONET SPEC中的描述则为:Jitter is defined as the short-term variations of a digital signal's significant instants from their ideal positions in time.

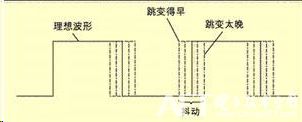

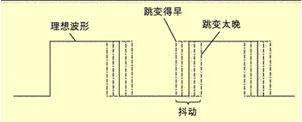

在理想情况下,一个频率固定的完美的脉冲信号(以1MHz为例)的持续时间应该恰好是1us,每500ns有一个跳变沿。但不幸的是,这种信号并不存在。如图1所示,信号周期的长度总会有一定变化,从而导致下一个沿的到来时间不确定。这种不确定就是抖动(jitter)。

抖动是对信号时域变化的测量结果,它从本质上描述了信号周期距离其理想值偏离了多少。在绝大多数文献和规范中,时间抖动(jitter)被定义为高速串行信号边沿到来时刻与理想时刻的偏差,所不同的是某些规范中将这种偏差中缓慢变化的成分称为时间游走(wander),而将变化较快的成分定义为时间抖动(jitter)。

图1 时间抖动示意图

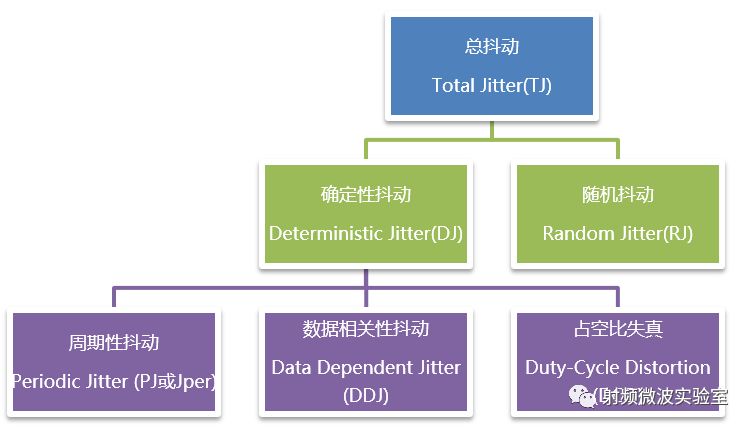

2时钟抖动的分类

抖动有两种主要类型:确定性抖动和随机性抖动。

确定性抖动是由可识别的干扰信号造成的,这种抖动通常幅度有限,具备特定的(而非随机的)产生原因,而且不能进行统计分析。

随机抖动是指由较难预测的因素导致的时序变化。例如,能够影响半导体晶体材料迁移率的温度因素,就可能造成载子流的随机变化。另外,半导体加工工艺的变化,例如掺杂密度不均,也可能造成抖动。

按照抖动的计算方式,可以将其分为如下三种:

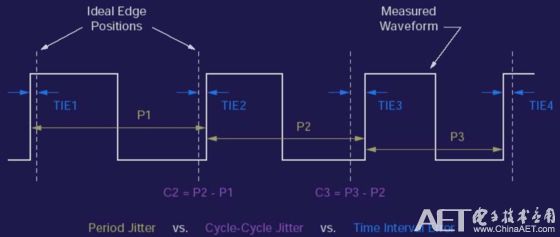

1)周期抖动(period jitter)

测量实时波形中每个时钟和数据的周期的宽度。这是最早最直接的一种测量抖动的方式。这一指标说明了时钟信号每个周期的变化。

2)周期间抖动(cycle-cycle jitter)

测量任意两个相邻时钟或数据的周期宽度的变动有多大,通过对周期抖动应用一阶差分运算,可以得到周期间抖动。这个指标在分析锁相环性质的时候具有明显的意义。

3)时间间隔误差(timer interval error,TIE)

测量时钟或数据的每个活动边沿与其理想位置有多大偏差,它使用参考时钟或时钟恢复提供理想的边沿。TIE在通信系统中特别重要,因为它说明了周期抖动在各个时期的累计效应。

图2 三种时间抖动的示意图

3时钟抖动的计算方式

例:某100MHz时钟,第一个到第四个周期分别为9.9ns, 10.1ns, 9.9ns, 10.0ns,假设其理想时钟固定在10ns。

TIE Jitter:

T1 = 10-9.9 = 0.1, T2 = 10-10.1 = -0.1, T3 = 10-9.9 = 0.1T4 = 10-10 = 0

TIE pk-pk jitter = 0.1 – (-0.1) = 0.2 ns

TIE RMS jitter = 参数T1..T4 的标准偏差

Period Jitter

P1 = 9.9 P2 = 10.1 P3 = 9.9 P4 = 10

Period Jitter pk-pk value = 10.1 - 9.9 = 0.2 ns

eriod Jitter RMS value =参数P1..P4 的标准偏差

Cycle to Cycle jitter

C1 = P2-P1 = 10.1-9.9 = 0.2 C2 = P3-P2 = 9.9-10.1 = -0.2C3 = P4-P3 = 10-9.9 = 0.1

Cycle to cycle jitter PK-PK value = 0.4 ns

Cycle to cycle jitter RMS value =参数C1..C4 的标准偏差

图3 标准偏差计算公式

4时钟抖动的来源

4.1.随机抖动(RJ,Random Jitter)

随机抖动是时间上的噪音,并没有任何已知的模式。尽管在随机过程的理论中,随机抖动可能有各种概率分布,但是jitter模型中通常假定为高斯正态分布。原因有两个:第一,许多电路中,随机噪声的主要来源是热噪声,其具有高斯分布;第二,根据中心极限定律,许多独立不相关噪声源叠加后趋近于一个高斯分布。由于随机抖动满足高斯分布,因此它的峰值是无界的。这是随机抖动区别于确定性抖动的重要特征。

4.2.确定性抖动(DJ,Deterministic Jitter)

相对于随机抖动,确定性抖动(DJ)是可以重复和预测的时间抖动,因此,DJ的峰峰值是有界的,而这个边界的位置随着测量次数的增加可以逼近真实值。DJ又可以分成几种,每种有自己的特点和背后对应的物理机制。

1)数据依赖型抖动(DDJ,Data Dependent Jitter)

数据依赖型抖动是和数据每一位内容相关的抖动。通常产生DDJ的原因是数据流通过带宽明显受限的信道时,出现码间干扰(ISI)而引起的。DDJ通常具有两个分立脉冲形式的直方图,并且两个峰的高度相同(根据峰所处的位置又可以分成高概率DDJ和低概率DDJ)。

2)占空比失真抖动(DCD,Duty Cycle Distortion)

占空比失真抖动是当时钟信号占空比不是50%时,由于过零点的位置不同所带来的测量抖动。其产生的原因有两种,其一,信号上升沿的摆率和下降沿的摆率不同,其二,由于判决阈值偏高或偏低。DCD通常具有和DDJ类似的两个分立脉冲形式的直方图,并且两个峰的高度相同。

3)有界不相关抖动(BUJ,Bounded Uncorrelated Jitter)

有界不相关抖动是一类在时间上不与jitter测量时刻相关,分布上有具有有界峰峰值的时间抖动的统称。其来源通常有3种:电源噪声。由于供电电源带来的噪声,可能会影响误码率;串扰和外部噪声。由于传输过程中可能由相邻传输线或外部电磁干扰引起的噪声;周期性噪声。由于各种周期性噪声带来的信号周期性抖动(PJ,Period Jitter)。例如:开关电源噪声或测试时使用的周期信号。只有单一频率成分的周期性抖动(PJ)具有一个两端为峰值中间凹陷形式的直方图。

5时钟抖动的分析手段

由于实际测试中,往往得到的复合时间抖动是由以上两种或几种Jitter模型的组合。利用概率论的知识可以知道复合抖动概率密度函数是组成该抖动的各个随机变量的概率密度函数的卷积。例如,一个DCD抖动和一个随机抖动的概率密度函数是将随机的高斯分布调制到DCD的两个尖峰上。此外,对于周期性抖动(PJ)不光有基波成分,往往还伴随着高次谐波。

5.1.统计特性和统计直方图

由于所有包含jitter的信号中都有随机成分的存在,因此统计计算被广泛应用在jitter性能的评估中。常用的统计参数有平均值、标准差、最大值、最小值、峰峰值等。通常采用直方图的形式来形象的描述jitter的这些统计特性。

统计直方图的横坐标是jitter的大小,纵坐标是jitter在某一区间内出现的频率。当测量次数足够多时,直方图是对jitter大小的概率密度函数的一个很好的估计,因此在通过jitter估计系统误码率时,统计直方图发挥着及其重要的作用。

需要注意的是直方图中不包含每个jitter点发生的先后顺序,因此不能用来显示jitter中存在的周期性信息。

5.2.Jiiter—时间曲线和Jitter的频率谱

由于统计直方图不能显示Jitter中存在的调制或周期性成分信息,这时可以用Jitter-时间曲线来描述Jitter随时间变化的趋势。曲线的横坐标为测量Jitter的时刻,纵坐标为Jitter的大小。这样从图中就可以清楚的看到Jitter随时间变化的模式。

既然Jitter中有随时间周期变化的成分,那么有一个很显然的分析手段就是对Jitter-时间曲线做傅立叶变换,从而得到其频域的特征。

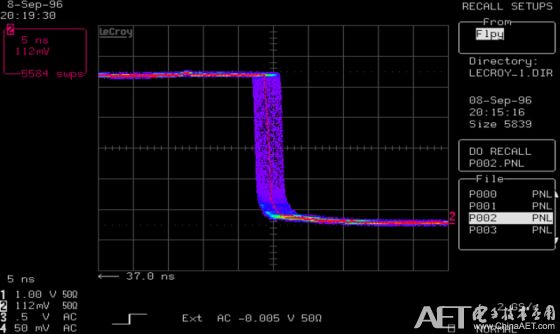

5.3.眼图

目前为止,眼图仍然是分析数字通信过程中的一种定性而方便的方法,它可以同时给出传输的幅度信息和时间信息。将一系列波形的短段将叠加在一起,与额定边沿位置和电压电平对齐。一旦抖动达到+-0.5UI,眼睛会闭上,接收机电路会出现误码。

需要注意的是在测量眼图时使用的触发源应该是有高频率稳定度低Jitter的标准时钟源,其指标直接影响到测量的精度。如果直接用测试信号的边沿做触发,需要示波器有时钟恢复功能。

6时钟抖动的测量方式

6.1.示波器测量Jitter

使用示波器测量信号的Jitter首先要求示波器有足够的带宽、信噪比、分辨率、时间准确度和信号保真度,以减少测量误差带来的影响。示波器内部往往采用软件的时钟恢复手段恢复出理想的边沿时刻(当然也可以采用外接高品质时钟源触发作为理想边沿时刻),此时示波器就可以通过叠加生成眼图。通过对眼图的分析,从而得到Jitter的各种参数。

在使用示波器分析的时候,往往需要进一步做Jitter分析,以得到误码的性质。这时需要输入数据流按一定规律重复发送(通常采用伪随机序列发生器),以使DDJ成分的能量尽量集中。通过示波器采集到这样的码流波形后,就可以做如下分析。

1)通过采样得到的数据进行内插恢复出采样波形,对于某个判决电平计算出每个边沿的过判决时刻;

2)通过软件锁相环的方法恢复出输入信号的时钟,并分别计算出每个边沿的jitter大小;

3) 对于连1或连0等不存在边沿的地方,通过线性内插法得到对应的Jitter;

4)对得到的Jitter-时间函数做FFT,得到Jitter的频谱。

接下来就可以通过对Jitter频谱的分析,找出对应的DCD、DDJ、PJ对应的峰值,以及RJ的底噪大小。然后分离出各个成分做IFFT就可以得到各个成分的Jitter-时间函数了。这里具体结果和FFT的分辨率、窗函数的选择有很大关系。

目前许多示波器生产厂家提供了跟示波器配套的分析软件,可以按一定模型对Jitter做有效地分解分析。例如:Tektronix提供的TDS JIT3就是用来配套TDS5000以上示波器的Jitter分析套件。

当然在进行复杂的Jitter分析之前,建议先使用传统的方式——余辉显示,来预先估计Jitter的严重程度:

此时的设置非常简单,只需要使用cursor测量波形边沿的宽度。但是应当注意的是:像素或屏幕分辨率(量化误差)会降低精度;且只有单个波形,并引入了触发抖动。

-

半导体

+关注

关注

327文章

24484浏览量

202024 -

振荡器

+关注

关注

28文章

3515浏览量

137629 -

时钟抖动

+关注

关注

1文章

54浏览量

15840

原文标题:【精品博文】聊一聊数字电路中时钟抖动

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

介绍FPGA设计中时序分析的一些基本概念

抖动的知识及测量方法

如何计算输出时钟的DISCRETE JITTER?

时间抖动的概念及其分析方法介绍

stm32f4时钟树和时钟控制基本概念

什么是jitter,jitter是什么意思?

用DSP实现抖动(Jitter)测量的方法

时钟抖动(Jitter)的基本概念

时钟抖动(Jitter)的基本概念

评论