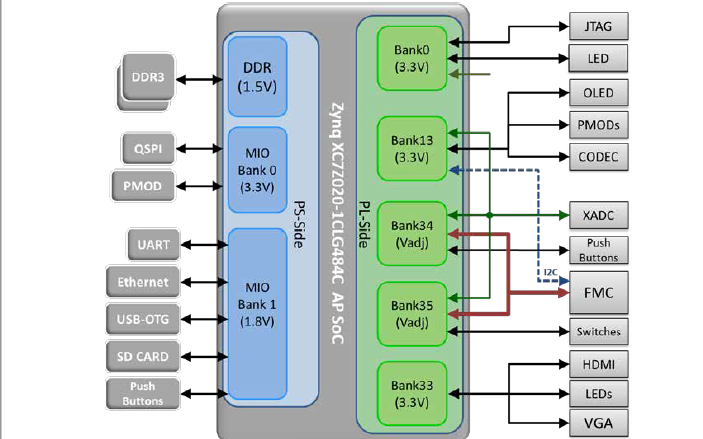

zedboard可以将逻辑资源和软件分别映射到PS和PL中,这样可以实现独一无二和差异换的系统功能,主要分为两大部分,处理系统和可编程逻辑。以及二者之间的互联特性。这篇笔记主要记录zedboard的大体架构。

1. 处理系统(PS)

应用处理单元(APU)

存储器接口

I/O外设,包括静态存储器和Flash存储器接口,可以通过共享一个54引脚的多路复用io(MIO)

互联,也可以扩展访问PL中的IO

2. 可编程逻辑(PL)

PS和PL使用了大量的借口和信号可以满足几乎所有的连接。

系统的启动

zynq的启动过程包含多个阶段,启动过程至少包含启动rom和第一级的启动引导代码( first-stage boot loader FSBL ),t同时包含可启动的rom,这个rom用户不可修改,完成了启动rom之后,然后执行FSLB 。复位之后,zynq可以自动的从外部的引导设备中启动设备,根据需要,用户可以配置zynq的PS和PL,可以使用jtag借口,用于启动时的调试。

在使用过程中,可以选择性的关闭PL一侧的电源,以降低功耗,当然也可以降低PS内的时钟。

处理系统的PS特性

1. 应用处理单元(APU)

arm 双核Cortex-A9多核处理器( ARM V7 )

系统特性:从PL和PS的加速器一致性端口(ACP),带有校验的256K的OCM,

2. 存储器接口

DDR控制权,四-SPI控制器,并且应当注意的是,下面的存储器可以作为基本的启动设备:

NAMD控制器,并行SRAM/NOR控制器

3. IO特性

提供了标准的io、工业标准接口。

GPIO,

3模式的以太网控制器,

USB控制器,可以作为主设备或者OTG

SD/SDIO控制器,两个,可以作为基本的启动设备,支持sd 2.0规范,

SPI控制器:四线总线,MOSI,MISO,SCLK,SS,支持全双工操作,

CAN控制器(两个)

UART控制器两个

i2c控制器(两个)

可编程逻辑PL特性

可配置逻辑块(CLB)

36KB的Bram,双端口,最多72位宽度,可编程fifo逻辑,

时钟管理

可配置的io

模数转换特性(XADC)

互联特性

1. 基于AXI高性能数据通路开关的PS互联

OCM互联,提供来自中央互联和PL的,用于对256KB存储器的访问,

CPU和ACP的接口,

中央互联,

中央互联是64位的,将IOP和DMA控制连接到DDR存储器控制器,片上系统RAM的接口开关。将以太网、usb、和sd/sdio控制器内的本地DMA单元连接到中央互联,将PS内的主设备连接到IOP。

2. PS-PL接口,包含所有PL设计者的可用信号,可以基于PL的功能和PS集结在 一起。

功能接口,包含AXI互联,用于大多数的IO外设、中断,DMA控制流、时钟和调试接口的扩展MIO接口,

-

Zedboard

+关注

关注

45文章

70浏览量

49070

发布评论请先 登录

相关推荐

玩转赛灵思Zedboard开发板(3):基于Zynq PL的流水灯

PYNQ案例(一):ZYNQ的PL与PS开发

Linux下如何通过UIO监控PL给到PS的中断

玩转赛灵思Zedboard开发板(2):最简单的测试工程

如何在使用PS和PL时使用SDK生成启动映像和程序闪存?

怎么在zedboard上测试DDR读写?

zynq 7020 PS和zynq PL是如何通话的?

请问是否可以在同一个Zynq FPGA中从PS控制PL JTAG?

一步一步学ZedBoard:使用PL做流水灯(完整工程文件下载)

一步一步学ZedBoard Zynq(二):使用PL做流水灯

基于ZedBoard的SCA架构的设计原理

Zedboard开发板硬件用户手册的资料免费下载

zedboard的大体架构介绍(PS、PL、硬件互联)

zedboard的大体架构介绍(PS、PL、硬件互联)

评论