通过简单地降低电压或频率来实现低功耗不可取——试问有谁会去买性能打过折的产品呢?那么,低功耗CPU到底又是怎么实现的?

随着智能手机等移动应用的兴起,目前的处理器设计不仅要提供高性能,还必须要符合另一个重要指标,那就是低功耗。通过简单地降低电压或频率来实现低功耗不可取——试问有谁会去买性能打过折的产品呢?那么,低功耗CPU到底又是怎么实现的?EDN小编今天来和大家理一理,简单来说,我们可以从微架构设计和制造工艺这两个方面来看。

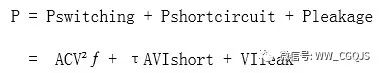

低功耗设计的基础:处理器功耗分析的经典公式

要想实现低功耗,就必须了解电路中功耗的来源[1]。对于CMOS电路功耗主要分为三部分,分别是:电路在对负载电容充电放电引起的跳变功耗;由CMOS晶体管在跳变过程中,短暂的电源和地导通带来的短路功耗;以及由漏电流引起的漏电功耗。其中跳变功耗和短路功耗为动态功耗,漏电功耗为静态功耗。以下是SoC(即CPU)功耗分析的经典公式:

其中:ƒ是系统的频率;A是跳变因子,即整个电路的平均反转比例;C是门电路的总电容;V是供电电压;τ是电平信号从开始变化到稳定的时间。

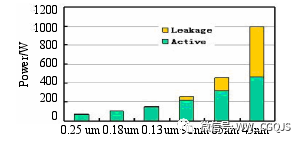

在深亚微米工艺下,电路的功耗主要是跳变功耗,短路功耗和漏电功耗可以忽略不计。但随着工艺发展到纳米级,漏电功耗在整个功耗中的比例将显著提高(如下图所示)。

图:不同工艺下动态功耗和静态功耗对比图

低功耗的微架构设计

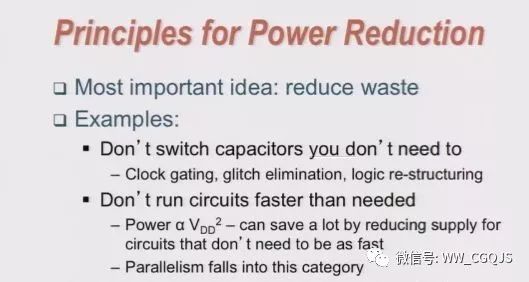

基于上面这个功耗分析的公式,我们要设法降低的主要就是其中的第一项和第三项功耗,即跳变功耗和漏电功耗。我们首先来看微架构设计,基本思路如下图:

因此,我们可以衍生出很多的低功耗微架构设计方法。里面比较重要的一些如下:

•时钟门控:给每个模块的时钟加上门控,不需要时将它关闭,从而尽可能降低功耗。

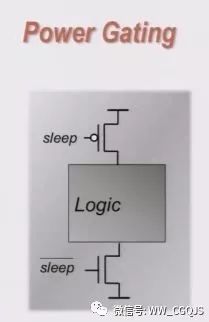

•电源门控:原理同上,尽可能降低动态功耗和漏电功耗。

•降低电压:电压受频率影响,可以通过降低频率来降低所需电压。当频率降低,电路开关速度降低,就能有更多时间去进行充电,因此所需充电电压就能降低(电压越大充电速度越快)。同时,可通过流水线分割组合逻辑。若同时保持频率不变,电路能有更多时间去进行充电,从而降低所需充电电压。

•系统设计时考虑优化,如减少电路开关,用RAM代替寄存器文件,减少存储器读写。

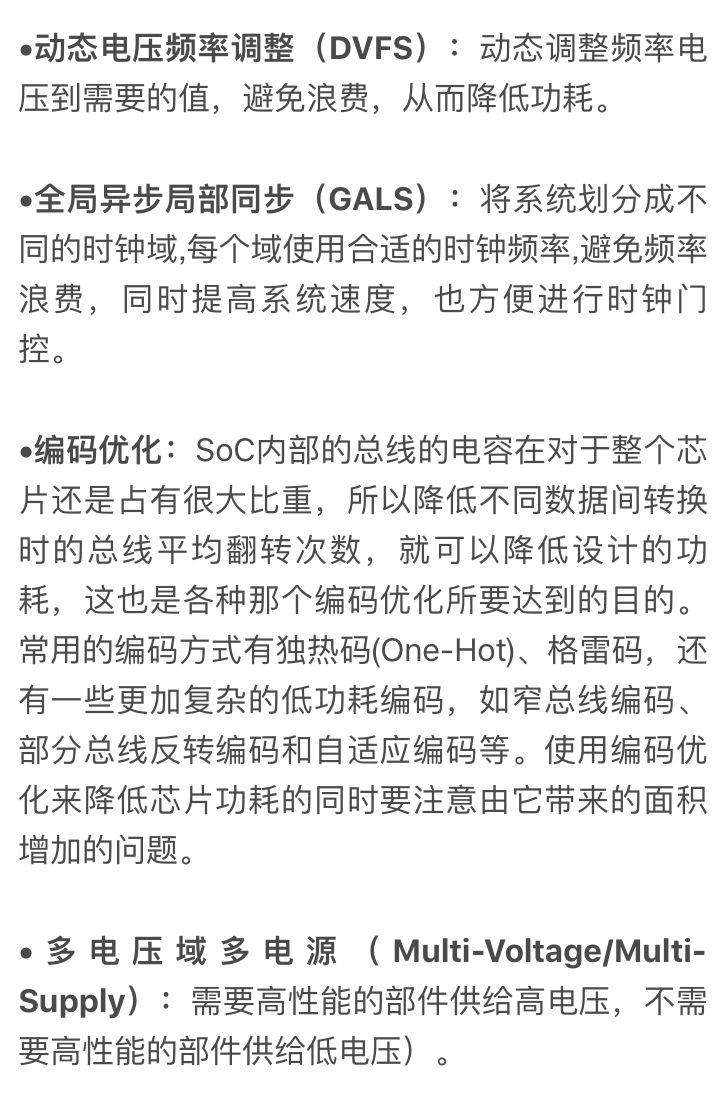

除了上述这些方法,高效的低功耗技术还有许多,比如衬底反偏(加反向电压降低衬底漏电),多阈值单元(Multi-Vth cell)等等设计方法。下图是一些比较热门的RTL级低功耗技术。

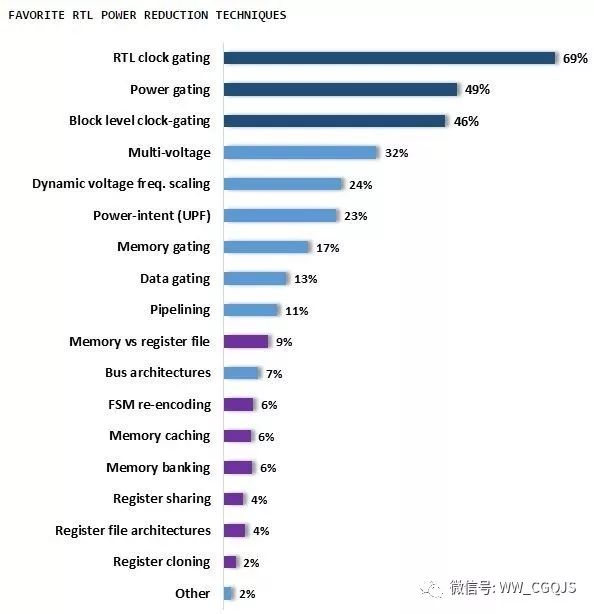

此外,对于CPU而言,PPA(性能、功耗和面积)也总是在互相权衡的。通过增加CPU内核数和采用ARM的big.LITTLE架构等,也是近年来常用的低功耗设计方法。

先进的低功耗制造工艺

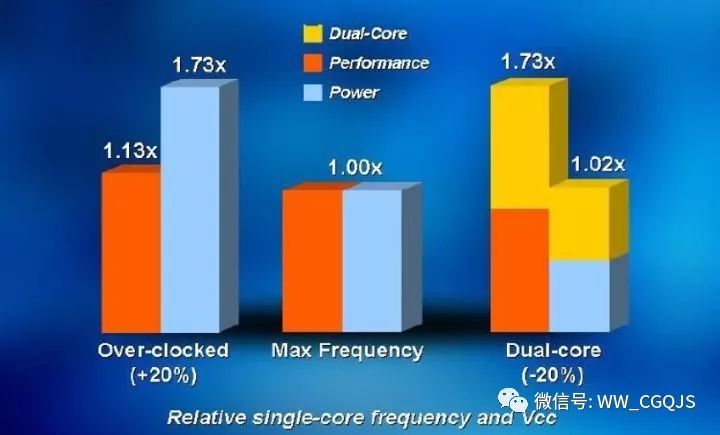

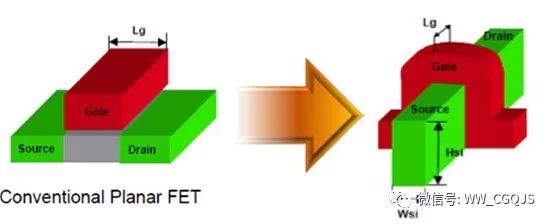

芯片的制造工艺在不断向前发展。一个常识是,工艺越先进(纳米数越低),功耗和性能都会提升。但是其原因又是为何?此外,FinFET工艺又是什么,为什么会更进一步实现二者的提升?这要从晶体管说起了:

这里,我们尽量把事情说简单。上面这副示意图中就是一个典型的半导体晶体管。其中两个绿色的部分(源极Source和漏极Drain)分别是晶体管的两级,类似电池的两级。红色的部分就是用来控制这两个电极的通断的,而通断分别对应数字化时间的1和0。所谓数字化世界其实也就是非常非常多的晶体管的通断变化组合出来的。红色栅极(Gate)的宽度就是我们通常所说的沟槽宽度或者线宽——我们通常说的多少多少nm就是指的这个宽度。

这个栅极的宽窄决定了性能和功耗。晶体管的开关速度(每次0/1变化)对应处理器的运算速度。红色的栅极越宽,两个绿色电极就越远,导致它们直接连通一次的时间就越长。所以栅极越小,晶体管一次状态变化所需的时间就越短,单位时间的工作次数就越多。这样一堆晶体管单位时间可做的运算自然就更多,所以性能更好。

再来看功耗。栅极是通过加电压帮助两个绿色电极通电的。而栅极越宽,就需要更高的电压才能导通两极;栅极越窄,导通就更容易,所需的电压也就越低。功耗的大小与电压的平方成正比,所以导通电压的下降是新工艺能够降低功耗的主要因素。还有一个因素,即便是电压相同,通过导体的面积和长度越小,电流也会越小。更小的栅极等于是缩小的导体,因此也会减少功耗。

那么,FinFET又是什么?

-

cpu

+关注

关注

68文章

10428浏览量

206517 -

制造工艺

+关注

关注

2文章

157浏览量

19538 -

低功耗

+关注

关注

9文章

2224浏览量

102637 -

COMS

+关注

关注

1文章

90浏览量

32494

原文标题:低功耗CPU是怎样炼成的?

文章出处:【微信号:WW_CGQJS,微信公众号:传感器技术】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

低功耗蓝牙上层架构浅析

汽车电子电气架构设计及优化措施

低功耗蓝牙怎么低功耗?如何界定

低功耗DFM和高速接口

基于超低功耗架构设计的智能手表平台W307

全极低功耗霍尔开关HAL250 纳安级霍尔IC全新上市

介绍STM32低功耗睡眠模式事件唤醒的实现

集成电路芯片AI低功耗设计的新方法

【书籍评测活动NO.18】 AI加速器架构设计与实现

《SoC底层软件低功耗系统设计与实现》阅读笔记

使用Simulink实现软件架构设计

从微架构设计和制造工艺低功耗CPU的实现

从微架构设计和制造工艺低功耗CPU的实现

评论