随着智能手机,以及物联网的普及,芯片功耗的问题最近几年得到了越来越多的重视。为了实现集成电路的低功耗设计目标,我们需要在系统设计阶段就采用低功耗设计的方案。而且,随着设计流程的逐步推进,到了芯片后端设计阶段,降低芯片功耗的方法已经很少了,节省的功耗百分比也不断下降。

芯片的功耗主要由静态功耗(static leakage power)和动态功耗(dynamic power)构成。静态功耗主要是指电路处于等待或者不激活状态时的泄漏电流所产生的功耗,主要是有反偏二极管泄漏电流,门栅感应漏极泄漏电流,亚阈值泄漏电流和门栅泄漏电流。动态功耗是指晶体管处于跳变状态所产生的功耗,主要由动态开关电流引起的动态开关功耗以及短路电流产生的短路功耗两部分组成。这些概念自己去看下参考书吧,不细展开了。

那我们来学一下,在数字后端阶段,有哪些方案可以降低上述功耗。

第一种方案就是多电源多电压技术,Multi supply Multi Voltage(MSMV)。这是一种可以有效降低动态功耗的技术。芯片可以划分为不同电压域(Voltage Area),也被称为Power Domain,不同逻辑模块处于不同的电源域中,由不同电源供电。高性能的部分在高电压域,低性能要求的部分就分配在低电压域。举例来说,一个SOC芯片中,CPU应该工作在尽可能高的时钟,则它的电压应该是最高电压;而外设中的USB模块,有协议定义的固定速率,则只要分配给能满足要求的工作电压即可;一些平时不工作的模块甚至可以将电压关断(Power Gating),也就可使功耗趋于0。这样一个芯片中,就会划分为各种不同的电压域。

那我们如何创建Voltage Area呢?

首先,我们需要有一个统一的功耗约束文件,这边以UPF来配合介绍,该文件可以实现在前端门级网表到最后逻辑验证等整个芯片开发过程的贯通使用。命令不多,比较好学。接下来几篇文章,大家一起和我配合着UPF文件来学习下Low Power知识。

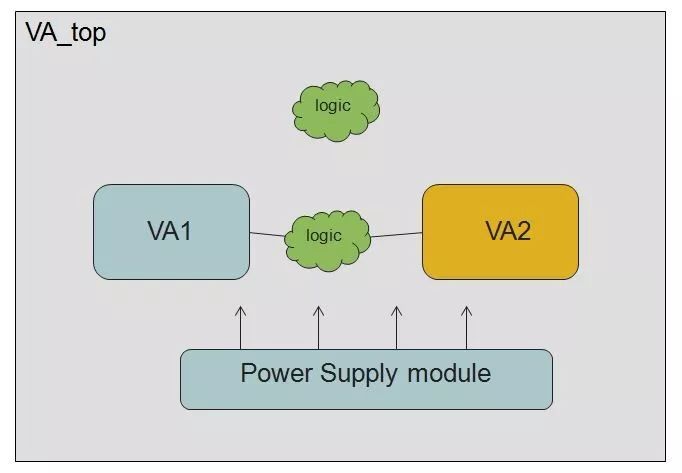

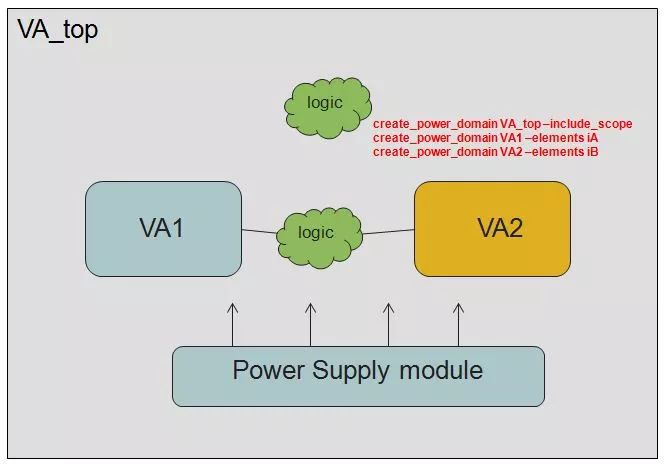

比如说我们要实现如下一个简单的MSMV设计,VA1和VA2两个不同的Voltage Area以及defalut的VA_top。

1.首先定义Voltage Area的信息

create_power_domain VA_top –include_scopedefault voltage area

create_power_domain VA1 –elements iA VA1

create_power_domain VA2 –elements iB VA2

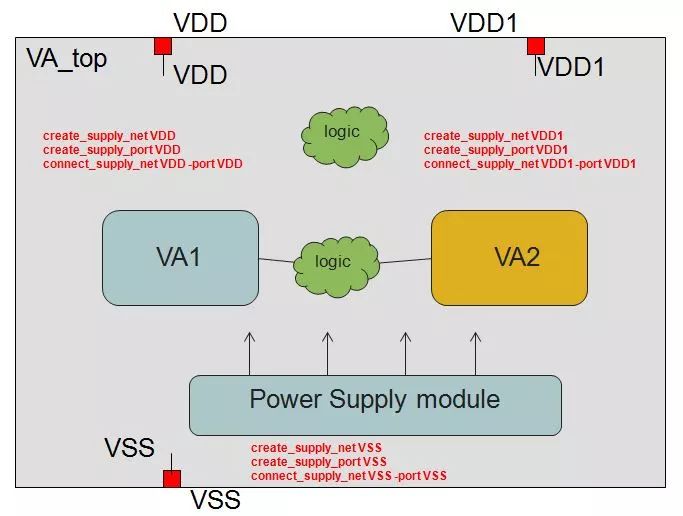

2.创建default voltage area上供电连接关系

create_supply_net VDD 创建supply net VDD

create_supply_port VDD 创建supply port VDD

connect_supply_net VDD -port VDD 将VDD net和VDD port在逻辑上关联

create_supply_net VDD1 创建supply net VDD1

create_supply_port VDD1 创建supply port VDD1

connect_supply_net VDD1 -port VDD1 将VDD1 net和VDD1 port在逻辑上关联

create_supply_net VSS 创建supply net VSS

create_supply_port VSS 创建supply port VSS

connect_supply_net VSS -port VSS 将VSS net和VSS port在逻辑上关联

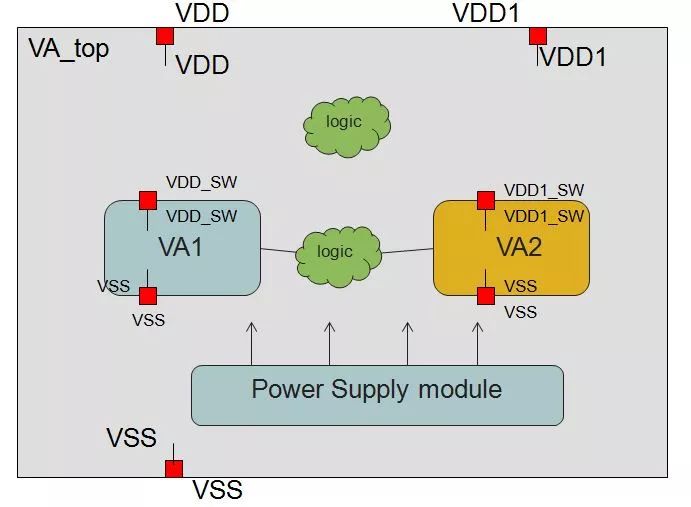

3.创建VA1和VA2 voltage area中的供电连接关系

create_supply_port VDD_sw–domain VA1

create_supply_portVDD1_sw–domain VA2

create_supply_port VSS -reuse –domain VA2

create_supply_port VSS -reuse –domain VA1

create_supply_net VDD_sw –domain VA1

create_supply_net VDD1_sw–domain VA2

create_supply_net VSS-reuse–domain VA1

create_supply_net VSS-reuse–domain VA2

connect_supply_net VDD_sw –ports VDD_sw –domain VA1

connect_supply_net VDD1_sw –ports VDD1_sw–domain VA2

connect_supply_net VSS –ports VSS–domain VA1

connect_supply_net VSS –ports VSS–domain VA2

4.创建供电集合,关联到Voltage Area

create_supply_set ss_top \ default voltage area set

-function {power VDD} \

-function {ground VSS}

create_supply_set ss_pd1 \ VA1set

-function {power VDD_sw} \

-function {ground VSS}

create_supply_setss_pd2 \ VA2 set

-function {powerVDD1_sw} \

-function {ground VSS}

associate_supply_set ss_top \

-handle VA_top.primary

associate_supply_setss_pd1\

-handle VA1.primary

associate_supply_setss_pd2\

-handle VA2.primary

到这边,一个UPF文件中关于voltage area的定义就好了,当我们读入UPF文件以后,并定义好voltage area的形状以后,在GUI上,我们就可以看到voltage area的样子了。

-

芯片

+关注

关注

446文章

47676浏览量

408721 -

功耗

+关注

关注

1文章

750浏览量

31496 -

UPF

+关注

关注

0文章

47浏览量

13340 -

数字后端

+关注

关注

0文章

10浏览量

3020

原文标题:Low Power概念介绍

文章出处:【微信号:IC_Physical_Design,微信公众号:数字后端IC芯片设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

CC2530 如何降低ZC发现网络的频次以降低功耗?

如何利用FPGA满足电信应用中的降低功耗要求?

如何降低FPGA设计的功耗?

怎么降低动态功耗?

怎么降低嵌入式芯片的功耗?

如何降低ZC发现网络的频次以降低功耗?

如何创建Flasher的secure area进行安全烧录?

降低系统功耗的方法

动态电压与频率调节在降低功耗中的作用

降低移动设计功耗的逻辑技术方法

降低芯片功耗方法以及如何创建Voltage Area

降低芯片功耗方法以及如何创建Voltage Area

评论