Nios系统的所有外设都是通过Avalon总线与Nios CPU相接的,Avalon总线是一种协议较为简单的片内总线,Nios通过Avalon总线与外界进行数据交换。

Avalon总线接口分类

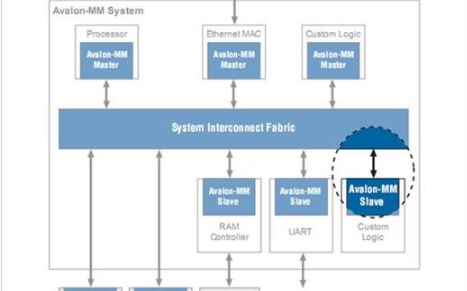

可分为两类:Slave和Master。slave是一个从控接口,而master是一个主控接口。slave和master主要的区别是对于Avalon总线控制权的把握。master接口具有相接的Avalon总线控制权,而slave接口是被动的。常见的Avalon的传输结构有:Avalon总线从读(slave read),Avalon总线带一个延迟状态从读,Avalon总线从写(slave write),Avalon总线带一个延迟状态从写。

Avalon总线的特点有

所有外设的接口与Avalon总线时钟同步,不需要复杂的握手/应答机制。这样就简化了Avalon总 线的时序行为,而且便于集成高速外设。Avalon总线以及整个系统的性能可以采用标准的同步时序分析技术来评估。

所有的信号都是高电平或低电平有效,便于信号在总线中高速传输。在Avalon总线中,由数据选择器(而不是三态缓冲器)决定哪个信号驱动哪个外设。因此外设即使在未被选中时也不需要将输出置为高阻态。

为了方便外设的设计,地址、数据和控制信号使用分离的、专用的端口。外设不需要识别地址总线周期和数据总线周期,也不需要在未被选中时使输出无效。分离的地址、数据和控制通道还简化了与片上用户自定义逻辑的连接 。

其他特性和约定

Avalon总线还包括许多其他特性和约定,用以支持SOPC Builder软件自动生成系统、总线和外设,包括:

最大4GB的地址空间——存储器和外设可以映像到32位地址空间中的任意位置

内置地址译码——Avalon总线自动产生所有外设的片选信号,极大地简化了基于Avalon总线的外设的设计工作

多主设备总线结构——Avalon总线上可以包含多个主外设,并自动生成仲裁逻辑

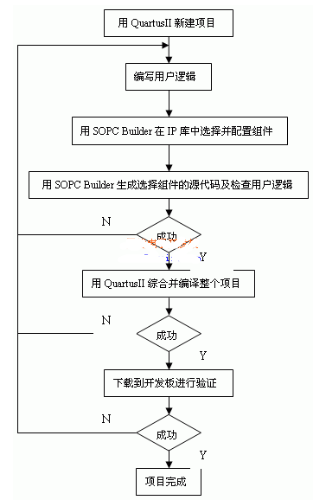

采用向导帮助用户配置系统——SOPC Builder提供图形化的向导帮助用户进行总线配置(添加外设、指定主/从关系、定义地址映像等)。Avalon总线结构将根据用户在向导中输入的参数自动生成

动态地址对齐——如果参与传输的双方总线宽度不一致,Avalon总线自动处理数据传输的细节,使得不同数据总线宽度的外设能够方便地连接

Avalon 总线模块为外设提供的服务

Avalon 总线模块为连接到总线的Avalon 外设提供了以下的服务:

数据通道多路转换——Avalon 总线模块的多路复用器从被选择的从外设向相关主外设传输数据。

地址译码——地址译码逻辑为每一个外设提供片选信号。这样,单独的外设不需要对地址线译码以产生片选信号,从而简化了外设的设计。

产生等待状态(Wait-State)——等待状态的产生拓展了一个或多个周期的总线传输,这有利于满足某些特殊的同步外设的需要。当从外设无法在一个时钟周期内应答的时候,产生的等待状态可以使主外设进入等待状态。在读使能及写使能信号需要一定的建立时间/保持时间要求的时候也可以产生等待状态。

动态总线宽度——动态总线宽度隐藏了窄带宽外设与较宽的Avalon 总线(或者Avalon 总线与更高带宽的外设)相接口的细节问题。举例来说,一个32 位的主设备从一个16 位的存储器中读数据的时候,动态总线宽度可以自动的对16 位的存储器进行两次读操作,从而传输32 位的数据。这便减少了主设备的逻辑及软件的复杂程度,因为主设备不需要关心外设的物理特性。

中断优先级(Interrupt-Priority)分配——当一个或者多个从外设产生中断的时候,Avalon 总线模块根据相应的中断请求号(IRQ)来判定中断请求。

延迟传输(Latent Transfer)能力——在主、从设备之间进行带有延迟传输的逻辑包含于Avalon总线模块的内部。

流式读写(Streaming Read and Write)能力——在主、从设备之间进行流传输使能的逻辑包含于Avalon 总线模块的内部。

-

NIOS

+关注

关注

2文章

104浏览量

52663 -

数据交换

+关注

关注

0文章

86浏览量

17810 -

Avalon总线

+关注

关注

0文章

11浏览量

10096

原文标题:Avalon总线概述

文章出处:【微信号:ALIFPGA,微信公众号:FPGA极客空间】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

avalon总线关于reset信号的问题

例说FPGA连载54:NAND Flash实例之Avalon-ST总线

nios与外面fpga的数据怎么通过avalon协议传输?

Avalon设备怎么定制?

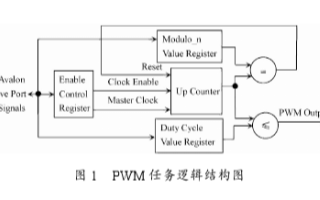

基于Avalon总线的PWM外设实现NiosⅡ嵌入式处理器的设计

Nios II处理器的体系结构及Avalon总线接口规范

锆石FPGA A4_Nano开发板视频:Avalon总线规范的讲解(2)

基于Nios II实现AVALON总线与USB控制器的接口设计

NiOSⅡ处理器的Avalon总线架构资料下载

基于Nios系统的Avalon总线概述

基于Nios系统的Avalon总线概述

评论