摘要:随着集成电路密度的不断提高,多晶硅栅的线宽不断变小,栅氧化层的厚度继续变薄,多晶硅的刻蚀变得越来越关键。多晶硅栅的形貌控制,栅氧化层二氧化硅的损失等关键特征已经被普遍关注。多晶硅刻蚀中的另一种现象:微沟槽缺陷(microtrench defect)也显得越发重要。该现象会造成器件的大面积漏电,严重杀伤每一个管芯,造成硅片的报废。作者通过相关试验,从工艺参数的角度对微沟槽缺陷的形成和控制做了讨论,对主要工艺参数对微沟槽缺陷的影响作了分组实验,为优化工艺参数来彻底防止微沟槽缺陷提供必要的指导。

1 引言

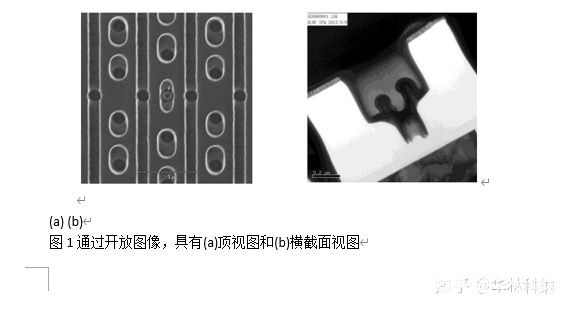

多晶硅刻蚀在集成电路芯片制造工艺中有着至关重要的作用,线宽和形貌的控制非常重要,也被大家普遍关注。但微沟槽缺陷(图 1,微沟槽缺陷的截面图)现象容易被忽视,因为通常的目检,镜检不易发现该缺陷[1-3]。但微沟槽缺陷对器件性能有致命影响,一旦形成器件漏电急剧加大,从而导致器件的各种失效[4]。微沟槽缺陷是在多晶刻蚀过程中,反应离子撞击下层栅氧化层,造成栅氧化层局部被击穿,在硅衬底上形成一个沟槽。由于其非常小,直径只有0.05~0.2 μm,深度只有 2 000~5 000 A,所以称之为微沟槽缺陷[5,6]。该缺陷在 0.35 μm 或以下线宽的技术中极易形成,主要是因为栅氧化层薄(小于 50 A), 较难阻挡离子的撞击。所以就有必要对刻蚀工艺的菜单进行优化,在取得垂直形貌的同时,也要寻找合适的工艺窗口,开发强大的工艺菜单,将微沟槽缺陷彻底消灭。

在实际生产中,多晶硅刻蚀的主流设备是反应离子刻蚀设备,且都具备独立可调的两组 RF 功率即源功率和偏压功率,都使用氯气和溴化氢气体作为主刻蚀气体,同时还有调节选择比的氧气和氦气混合气体。本次实验,我们在主刻蚀工艺步骤(终点监测步骤),对主要工艺参数:腔体压力,源功率,偏压功率,氯气/溴化氢气体比率这四个参数进行大范围的调整,用终点检测方法刻蚀实验片,通过扫描电镜仔细观察多晶硅边缘的缺陷数量,来判断该参数对微沟槽缺陷的影响,并对这一缺陷形成的原因进行了相应解释,并提出了改善措施。

2 实验

2.1 实验条件

在多晶硅刻蚀的主刻蚀步骤,对腔体压力,源功率(Source Power),偏压功率(Bias power)和氯气/溴化氢气体的比率进行分别拉偏分组,实验条件如下:

第 1 组,腔体压力分组:3 mT,5 mT,10 mT,20 mT。

第 2 组,源功率分组:150 W,200 W,250 W,300 W。

第 3 组,偏压功率分组:50 W,100 W,150 W,200 W

第 4 组,氯气/溴化氢气体比率分组: 25 / 75,33 / 66,50 / 50,66 / 33 (单位:SCCM)

附注:标准主刻蚀步骤的菜单为:腔体压力 10 mT,源功率 200 W,偏压功率 75W,氯气/溴化氢气体 33 / 66 SCCM,氧气-氦气 5 SCCM。终点监测:97%。

2.2 观察结构

为了方便观察刻蚀后的微沟槽缺陷程度,我们设计了一种特殊的图形结构。

在 3.3 μm×3.3 μm 的正方形区域中,设计了多根线宽为 0.3 μm 的多晶线条(Line),其间距也为 0.3 μm (Space)。即 Line 和 Space 的比例为1:1,共六条 Line,5 个 Space。

用扫描电镜观察两条多晶硅线条之间,在多晶硅边缘是否有微沟槽缺陷。一般用 10 K~50 K 的倍率观察,用 10 K 倍率寻找可疑点,用 50 K 倍率确认缺陷的存在。

2.3 多晶硅样片制备

硅片表面清洗后,先生长一层 50 A 的热氧氧化层,用 LPCVD 炉管淀积 3 000 A 多晶硅,DUV 光刻机曝光形成测试图形供刻蚀使用。光刻胶的形貌必须符合要求,即垂直的形貌(大于 88 ℃)并且无任何底膜残留。

2.4 缺陷程度

为了便于定性定量分析工艺参数与微沟槽缺陷数量的对应关系,我们对微沟槽缺陷的程度的描述做了如表 1。

3 实验结果

四组实验的结果(详见图 2,图 3,图 4 和图5)表明:

(1)腔体压力变化对微沟槽缺陷现象的产生有着重大影响。从线段图上可以看出随着腔体压力的减低,微沟槽缺陷现象越来越严重,在 3 mT 时,经常发现某些区域上许多微小的沟槽会逐渐连接结起来形成一条长沟槽(大于 0.5 μm),这说明微沟槽缺陷现象已经非常严重了。

(2)源功率的变化对微沟槽缺陷现象的产生几乎没有影响。在 150 W 到 300 W 范围内没有观察到微沟槽缺陷,由于在实际应用中没有必要使用大于 300 W 的源功率,所以没有做进一步加大源功率的实验。

(3)偏压功率对微沟槽缺陷现象的产生有着重大影响。从线段图上可以看出随着偏压功率的增加,当偏压功率达到一定数值时,微沟槽缺陷越来越严重,微沟槽缺陷数量会急剧增加。

(4)氯气/溴化氢气体比率的变化对微沟槽缺陷影响不大,但氯气上升太多,当氯气/溴化氢气体比率达到 2:1 比率时,也会形成中等数量的微沟槽缺陷。

4 微沟槽缺陷的形成机制与实验结果分析

微沟槽缺陷的形成已经被普遍认为和反应离子的反射有关,图 6 为简单示意图。在腔体中,反应离子向下撞击,部分离子撞击到多晶硅线条的侧壁上,会反射到多晶硅的边缘,造成局部区域的轰击力特别强大,这些区域的栅氧化层会首先被击穿,一旦氧化层被击穿,反应离子迅速刻蚀硅衬底,形成微沟槽。显而易见多晶硅下面的栅氧化层对微沟槽缺陷的形成起着阻挡和保护作用,只要栅氧化层足够强大,足够厚,就没有机会形成微沟槽。但是栅氧化层的厚度是由器件的性能决定的,0.35 μm 技术一般栅氧化层的厚度在 50~60 A 左右,0.18 μm 技术在 20~30 A 左右,这个厚度不足以阻挡微沟槽缺陷的形成。

腔体内反应离子的反射是客观存在的,在目前的条件下是无法避免的。但是反应离子要轰击氧化层就需要能量,如果能量不够大,在整个刻蚀时间内并不能击穿氧化层,微沟槽缺陷也不能形成。

所以反应离子的能量对微沟槽缺陷的形成起着决定性的作用。能量越大,离子对栅氧化层的轰击力也越大,造成氧化层局部被破坏的可能行就越大,就越容易形成微沟槽缺陷。

对上述四组试验结果分析。

(1)腔体压力的降低,反应离子的能量会显著增加。在刻蚀腔体中有大量的离子存在,这些运动中的离子都有一定的能量(动能),由于这些离子在运动,它们之间会不断地相互碰撞,碰撞会损失能量,最终导致撞击多晶硅线条侧壁的离子能量减低。

但是,随着腔体压力的降低,离子的平均自由程就变长。平均自由程长,离子间相互碰撞的几率就降低,离子的能量损失就会大幅度减少。

所以,压力越低,反应离子的能量就越大,栅氧化层就越容易被轰击击穿,微沟槽缺陷的程度就会显著增加。

(2)源功率的变化主要影响反应离子的密度即单位体积内的反应离子的数量,不增加反应离子的能量。所以它的增加,对微沟槽缺陷数量的变化没有贡献,但源功率增加会小幅增加刻蚀的速率。

(3)偏压功率变化对离子能量变化起着直接的作用。在反应离子刻蚀中,偏压是负值,而反应离子是正电荷。由负偏压产生的电场能显著加快离子向下(向着硅片表面)的运动速度,使撞击的力量显著增强。所以反应离子的能量随着偏压功率的增加而增加,那么微沟槽缺陷程度也随之增强。

(4)氯气/溴化氢气体主要是用来调节多晶硅对二氧化硅的刻蚀选择比,不对反应离子的能量变化产生影响。

正是因为该比率会影响选择比,所以氯气增加过多时,即氯气/溴化氢气体比率增加,对底部二氧化硅刻蚀速率也会增加,二氧化硅相对容易被刻蚀掉,这样二氧化硅就不能提供阻挡保护作用,从而形成微沟槽缺陷。

5 结语

通过实验明确了工艺参数对微沟槽缺陷形成的影响,工艺参数对多晶硅刻蚀过程和结果产生的影响是相互制约的,为了取得比较垂直的多晶硅形貌就需要比较大的偏压功率和较低的腔体压力,这对微沟槽缺陷的控制又是不利的。

一般建议压力不要低于 10 mT,偏压功率维持在 100 W 以下。在多晶硅刻蚀工艺开发中,要做好平衡,进行多尺度优化,对工艺窗口做一个全面检查,不能故此失彼,这样才能为生产提供一个足够强大的工艺菜单。

参考文献

[1] Michael A.Lieberman , Alan J.Lichtenberg.Principles of Plasma Discharges and Materials Processing, 2nd Edition[M].

[2] Stanley Wolf,Richard N. Tauber.Silicon Processing for the VLSI Era,Vol.1: Process Technology 2nd Edition[M].

[3] Wai-Fah Chen.VLSI Technology[M].

[4] 严利人等.微纳尺度制造工程[M].电子工业出版社,2011.

[5] S.Van Nguyen, D.Dobuzinski, S.R.Stiffler, G.Chrisman.Ion scattering from sloped sidewall surfaces[J]. Electrochem. Soc, 1991, (138)1112 .

[6] Robert J.Hoekstra,Mark J.Kushner, Valerity Sukharev, Phillipe Schoenborn, J.Vac.Sci.Microtrenching resulting from specular reflection during chlorine etch of silicon[J].Technol B,1998, 16(4).

-

集成电路制造

+关注

关注

0文章

10浏览量

6900 -

反应离子刻蚀

+关注

关注

0文章

5浏览量

1785

原文标题:微沟槽缺陷的形成与改进

文章出处:【微信号:appic-cn,微信公众号:集成电路应用杂志】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

通过一体式蚀刻工艺来减少通孔的缺陷

工艺参数对微沟槽缺陷形成的影响并改进微沟槽缺陷

工艺参数对微沟槽缺陷形成的影响并改进微沟槽缺陷

评论