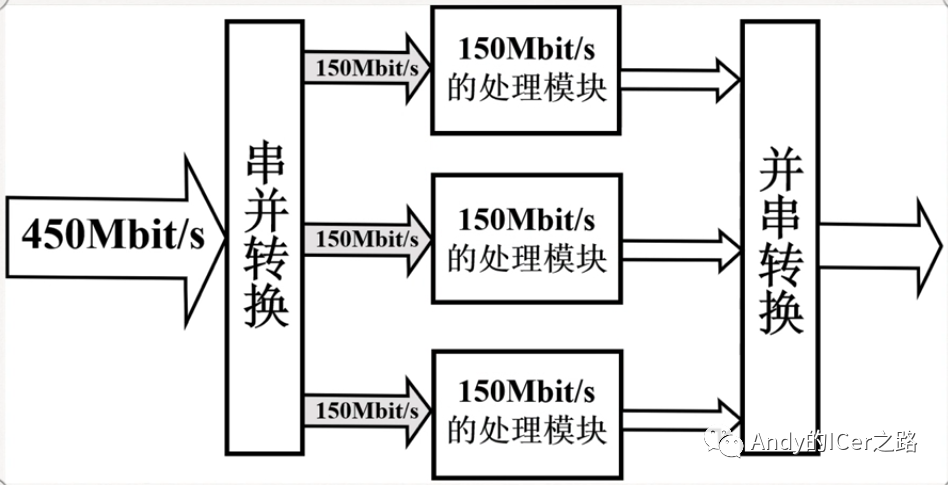

速度和面积互换原则。以面积换速度可以实现很高的数据吞吐率,其实串/并转换、就是一种以面积换速度的思想

2.乒乓操作。

3.串/并转换的思想。

高速数据处理的重要技巧之一。这里我来举一个多相滤波器抽取的例子:

抽取之后,两路数据以二分频的速度进行处理即可

4.流水线设计(在fir滤波器中表现很突出,一个时钟输出一个数据)

流水线设计可以从某种程度上提高系统频率。。前提是:设计可以分为若干步骤进行处理,而且整个数据处理的过程是单向的,即没有反馈或者逆运算、前一个步骤的输出是下一个步骤的输入。。。

5.逻辑复制与模块复用。

模块复用在节省逻辑资源方面使用非常广泛(举个例子吧)

对比一下,不多说了,一例胜千言!

至于逻辑复制呢,以后再说,目前还没碰到。把概念先抄上来:逻辑复制是一种通过增加面积来改善时序条件的优化手段,其最重要的应用是调整信号的扇出。换句话说,也就是其扇出非常大,那么为了增加这个信号的驱动能力,就必须插入很多级的Buffer,这样就在一定程度上增加了这个信号的路径延时。这种情况下就可以赋值生成这个信号的逻辑,用多路同频同相的信号驱动后续电路,是平均到每路德扇出变低,这样就不需要插入Buffer就能满足驱动能力增加的需求,从而节约该信号的路径延时。

总之。模块复用节省面积,牺牲速度,而逻辑复制正好相反。。

6.模块化设计

就是自顶向下的设计方法。。不讨论了、很简单有很难得东西。

7.时钟设计技巧

尽量避免使用FPGA内部逻辑产生的时钟,因为它很容易导致功能或时序出现问题。内部组合逻辑产生的时钟容易出现毛刺,影响设计的功能实现;组合逻辑固有的延时也容易导致时序问题。

如果采用内部组合逻辑产生的输出作为时钟信号或者异步复位信号,可能会不可避免的出现毛刺。如果此时信号正处于变换过程,那么它将违反建立时间和保持时间的要求,从而影响后续电路的输出状态,甚至导致整个系统运行失败。

如果要减少毛刺,最好用时钟打一下。。达到同步处理的效果。

对于设计中需要用到的分频时钟,应该尽量使用使能时钟,让分频信号作为使能信号来使用。

-

FPGA

+关注

关注

1599文章

21275浏览量

592837 -

FPGA设计

+关注

关注

9文章

425浏览量

26266 -

可编程逻辑

+关注

关注

7文章

511浏览量

43892 -

智能硬件

+关注

关注

203文章

2304浏览量

106491

原文标题:FPGA重要设计思想

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA设计思想,速度和面积互换原则不可忽视

FPGA设计思想,速度和面积互换原则不可忽视

评论